STM32H747 / STM32H745 简单测试

目录

1 简介

2 datasheet关键点介绍

2.1 PWR

3 资料说明

4 例程运行

4.1 选择CM7作为项目工程对象,并编译下载程序

4.2 同理编译CM4项目对象

4.3 编译结果说明

参考链接

1 简介

STM32H747/757 系列产品线拥有 Cortex-M7 内核(带双精度浮点单元,运行频率高达 480 MHz)和 Cortex-M4 内核(带单精度浮点单元,运行频率高达 240 MHz)的双核性能。与 STM32F7 产品线相比,其动态功耗效率提升了两倍(运行模式下)。

得益于其拥有的 L1 高速缓存和 ART 技术,在Cortex-M7 的 480 MHz主频和 Cortex-M4 的 240 MHz 主频运行条件下,实现从内部flash执行程序零等待,并获得高达 3220 CoreMark/1327 DMIPS 的性能评分。DSP指令及双精度浮点数处理单元拓展了产品的应用范围。凭借片内L1 cache(16 Kbytes +16 Kbytes of I-cache and D-cache)和ART加速器,即使从外部flash执行程序代码也不会带来性能的损失。[1]

该产品为2019年推出,虽然价格与F1C100S比较没有优势,但ST更适合在工业领域使用,运行复杂的算法时优势明显。

当然,双核性能固然优越,但也提高了使用门槛。它丰富的电源管理策略使其很适合做低功耗设计,而要够理清这些电源模式和时钟树就不得不下大工夫了。如果你对STM32H743已经有足够的了解,并能接受这款芯片的电源管理的复杂性,同时对价格不太敏感,这一系列芯片将值得一试。

2 datasheet关键点介绍

熟悉STM32H743后,首先仔细阅读手册中 7、9、14、20章应该能对该芯片有一定的了解了,下文也将简要的介绍下7、9、20章。

The RCC block manages the clock and reset generation for the whole microcontroller, which embeds two CPUs: an Arm® Cortex®-M7 and an Arm® Cortex®-M4, called CPU1 and CPU2, respectively.

2.1 PWR

1、电源供给

The VCORE core domain supply can be provided by the SMPS step-down converter, voltage regulator or by an external supply (VCAP). VCORE supplies all the digital circuitries except for the backup domain and the Standby circuitry. The VCORE domain is split into 3 sections:

• D1 domain containing the CPU (Cortex®-M7), Flash memory and peripherals.

• D2 domain containing peripherals and a Cortex®-M4 CPU.

• D3 domain containing the system control, I/O logic and low-power peripherals.

When a system reset occurs, the voltage regulator is enabled and supplies VCORE. The SMPS step-down converter is also enabled to deliver 1.2 V. This allows the system to start up in any supply configurations (see Figure 22)

2、运行模式[7.6]

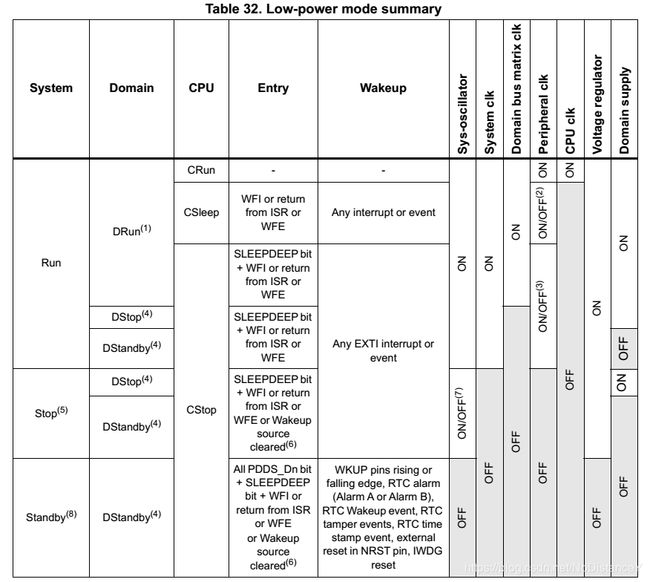

CPU的运行模式有:CRun,Csleep,Cstop

V_CORE域D1,D2的运行模式有:Drun,Dstop,Dstandby

CPU和V_CORE域的选择决定了系统运行的模式,如Table 32所示

3、电压和主频的关系

升频:先提高电压(change VOS),【使能PLL(仅VOS3->VOS2需要这一步)】,最后当PLL锁定时,变换系统时钟。

降频:降低系统频率,【失能PLL(仅VOS2->VOS3需要这一步)】,然后降低电平

4、当你理清程序运行策略后,可根据下图 37实现程序:

2.2 RCC

RCC寄存器对照表(register map)可以分为4类:[9.7.1]

| 寄存器组 |

描述 |

地址偏移 |

| 普通寄存器组(register bank) |

accessible by both cores and by any other master |

0x000~0x0D0 |

| 映射到相同地址的寄存器组 |

– When accessed by CPU1, CPU1 register bank is accessed. – When accessed by CPU2, CPU2 register bank is accessed. the “same address bank” can only be accessed by CPU1 or CPU2. |

0x0D0~0x130 |

| CPU1寄存器组 |

containing the peripheral enable bits (PERxEN), the peripheral low-power enable bits (PERxLPEN) and reset flag status bits for peripheral allocation to CPU1 |

0x130~0x190 |

| CPU2寄存器组 |

CPU2 register bank containing the peripheral enable bits (PERxEN), the peripheral low-power enable bits (PERxLPEN) and reset flag status bits for peripheral allocation to CPU2. |

0x190~0x1FF |

根据RCC寄存器的配置,可以把片内外设分配给具体的MCU,每个MCU就能像以前熟悉的样子运行了。图65就是一个很好的例子:

需要注意的是:SRAM4, IWGD1, IWGD2 and RCC are common resources and are implicitly allocated to both CPU1 and CPU2.

2.3 NVIC

该系列芯片的中断设置还没发现有难点。总结如下:

a\两个CPU有各自独立的内核中断

b\两个CPU通过Hardware Semaphore (HSEM) interrupt 联系

c\普通中断线共用:如当CPU1和CPU2同时打开EXTI中断时,两个CPU可以各自独立运行自己的中断服务函数。

3 资料说明

1、STM32CubeMX 的STM32H7 1.3.2 及以前的包中并没有找到STM32H745/STM32H747相关的包,因此不能自动生成代码

2、STM32Cube_FW_H7_V1.5.0 文件下的projects有相关例程,可以认真阅读

3、运行代码前,需要安装较新版本的keil包,如Keil.STM32H7xx_DFP.2.3.1.pack

4、下文例子将在NUCLEO-H745ZI-Q评估板运行

4 例程运行

到以下目录打开工程:xxx\STM32Cube_FW_H7_V1.5.0\Projects\NUCLEO-H745ZI-Q\Examples\GPIO\GPIO_EXTI\MDK-ARM

实验说明则看上一级目录下的“readme.txt”,这里不再赘述。

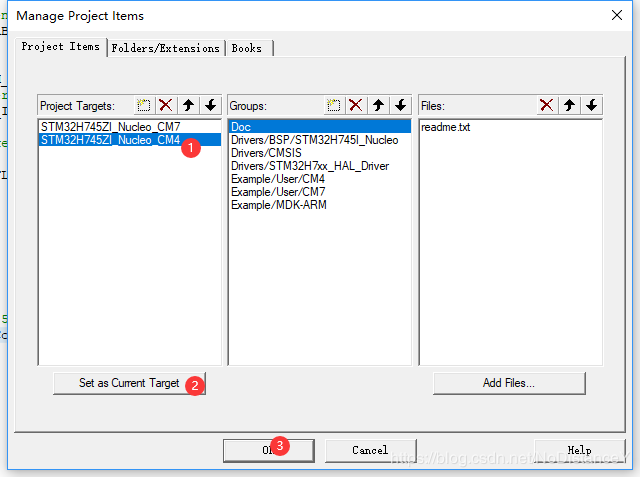

4.1 选择CM7作为项目工程对象,并编译下载程序

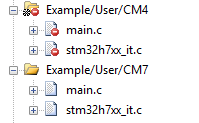

如果上图操作成功,则CM4文件夹中的文件应该是有减号的,如下图所示。带减号的文件表示文件不参与目标的编译,

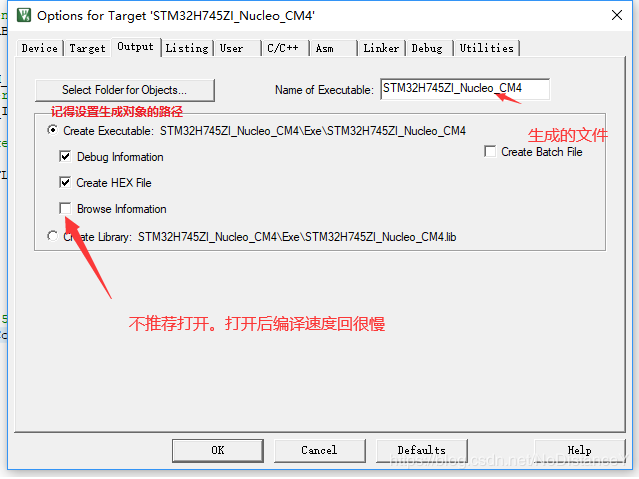

在编译前,需先进行编译选项配置

配置后,进行编译下载

4.2 同理编译CM4项目对象

设置成功后,工程变成下图的样子

在编译前进行编译设置

配置后,进行编译下载

4.3 编译结果说明

编译后会生成如下两个文件:

自己要设置在M7对象下运行,因如何把M4对象相关的文件屏蔽了呢,即如何生成减号?

以CM4文件夹下的main.c为例,

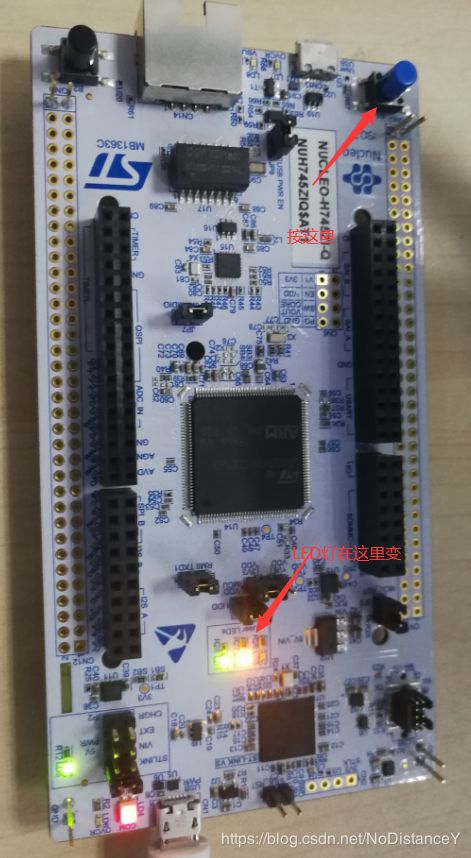

当下载程序后,按Nucleo开发板的蓝色按键,板子上的两个LED等会同时亮起。再按按键,两个LED等将关闭。

参考链接

[1] https://www.stmcu.com.cn/Product/pro_detail/cat_code/STM32H747_757/family/81/sub_family/236/sub_child_family/277/layout/product