STA-1. 从一个反向器开始说时序

前一篇讲到STA其实嵌入在综合,布局布线(简称PnR),时序签核(简称Signoff)等整个物理实现的过程中,对于STA的理解是每一个IC工程师,特别是后端工程师的必备素质。

看到文章的标题,我猜您也许会觉得反相器很简单,但其实反相器是所有数字设计的基本核心单元。下面就来考考您能回答到第几层问题。(注:有些是在应届毕业生面试中经常被问到的)

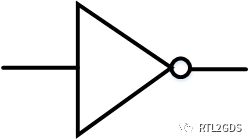

第一层:您能画出反相器的symbol吗?

肯定没问题,否则请出门左转,一定是走错场子了...

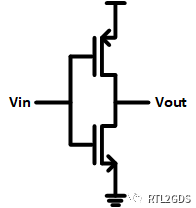

第二层:您能画出反相器的晶体管级电路图吗?

应该没问题,否则同上...

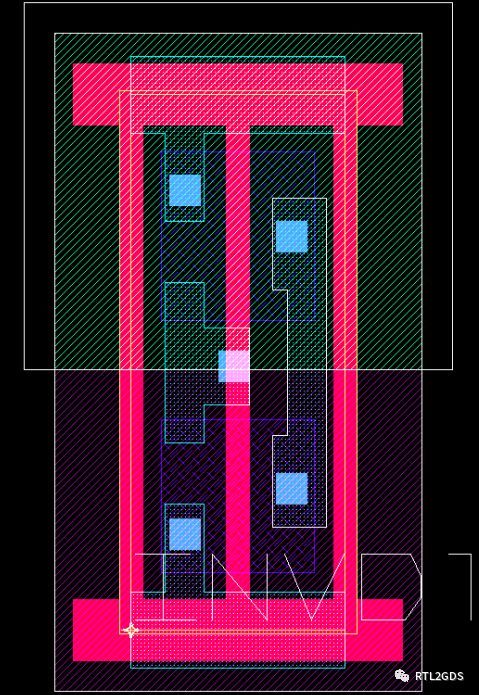

第三层:您能画出反相器的版图吗?

下图是量产工艺库里面一个最小反相器真实的版图:

第四层:您能画出反相器的工艺横截面图吗?

横截面示意图如下,应届生面试时特别容易考这个问题,而且会扩展出让你画闩锁效应等效电路图等进一步问题,需要仔细了解。下图显示的是:在P型衬底中有一块N阱,PMOS管长在N阱中,NMOS管长在P衬底中,红色为poly层,绿色为VIA0或者M1层绕线。

第五层:您知道反相器的传输延时在STA中是如何得到的吗?

这些传输延时(简称delay)都是通过库里面的查找表得到的,这些查找表是通过对标准单元进行建模,然后利用模型进行扫描仿真得到一个查找表,方便STA时使用。对于标准单元延迟时间的建模模型,需要特别了解的有两类,一类是基于电压源的NLDM(Non-Linear Delay Model),另一类是基于电流源的CCS模型(Composite Current Source)。

NLDM模型

NLDM模型的驱动端和接收端的模型如下:

通过改变输入信号转化时间(Input Transition)和输出负载(Output Load),仿真得到标准单元(简称stdcell)delay值的查找表,存在标准单元库(.lib)中,如下图所示,查找表中一般有index1(Input Transition或者slew)和index2 (Output Load)两个维度,其中:index1是纵坐标,index2是横坐标。那如果Input Transition的值,或者Output Load的值不在查找表中,工具会通过插值运算来计算出delay值。

NLDM模型的前提假设是接收端负责为纯电容性负载,但是随着集成电路尺寸的缩小,绕线电阻变得不容忽视,这种模型的误差也会变大。另外一点是因为在深亚微米工艺,绕线串扰引起的噪声影响越来越大,需要新的模型来更精确地来模拟噪声。CCS模型就是因此而引入的。

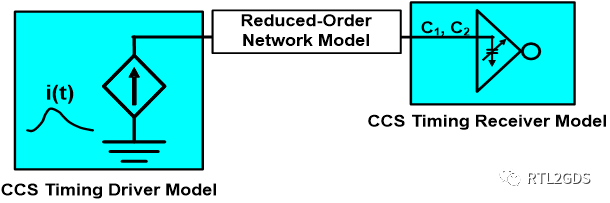

CCS模型

CCS模型的驱动端和接收端的模型如下,与NLDM不同的是,在驱动端采用电流源代替了电压源,在接收端采用两个电容,其中一个模拟近端的负载电容(C1),它的充放电速度快,另一个模拟的是远端的电容(C2),它的充放电速度慢,这样能够进一步提高上升和下降波形的精确度。

CCS模型在.lib中是以离散波形的形式存在的,如下图所示 :

从精度上来说,NLDM模型跟SPICE模型的误差在正负5%左右,而CCS模型跟SPICE模型的误差能达到正负2%。

第六层:您知道反相器的延时的计算公式吗?

一般反相器可以等效为下面的开关电阻电容模型,当输入为低电平时,NMOS管断开,PMOS管等效为一个电阻Rp,而当输入为高电平时,PMOS断开,NMOS等效为一个电阻Rn。

为了简化运算,我们暂时假设输入信号高低转换的时间为零,即为一个阶跃响应(实际上不可能,所以才需要考虑Input Transition),那么对于输出Vout来说,它从低到高的传输延时tpLH其实是电源VDD经过Rp对输出电容CL的充电时间。类似地,从高到低的传输延时tpHL其实是电容CL经过Rn对地的放电时间。公式如下:(如果对公式中0.69这个值不解,可以在公众号发消息给我)

那么问题又来了,怎样才能尽量保证下降和上升延迟一样呢?这一点对于时钟树上的clock inverter 和clock buffer尤为重要。通过上面的公式可以知道,方法就是让Rp和Rn尽量一致,由于PMOS管是利用空穴传输电流,而NMOS是利用电子传输电流,它们的迁移率是不同的,为了让Rp = Rn, 一般需要PMOS管的宽长比(Wp/Lp)是NMOS管(Wn/Ln)的2-3倍。

第七层:您知道反相器的SPICE模型吗?

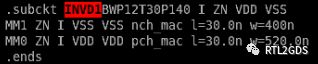

从前面的内容可以看出,衡量stdcell delay模型的好坏,其中一个指标是与SPICE模型的误差,那我们来看看一个标准单元库中最小尺寸反相器的SPICE模型:

它仅仅由一个NMOS管(nch_mac)和一个PMOS管(pch_mac)组成,它们的沟道长度都为30nm,宽度分别为400nm和520nm,容易看出,这个反相器在上升下降延迟上可能会有一定差别。那具体nch_mac和pch_mac的模型就更复杂了,模拟电路设计工程师需要特别关注,但是作为数字电路设计,不必深究,不过需要知道MOS管大致工作的几个区域,比如线性区(resistive,功能等效为电阻),饱和区(saturated),以及截止区(off)。下图中的反相器输入输出传输特性曲线上标出了不同输入电压下NMOS和PMOS的工作状态,有兴趣可以深究,在这里就不继续挖了。

总结

一个简单的反相器能体现出数字前端和后端设计中很多方面的知识,远远不止上面七个问题而已。这篇文章想重点介绍的是,STA所用到的标准单元库中stdcell delay值是怎么计算出来的,以及两种stdcell delay模型(NLDM和CCS)相关概念。

![]()

历史文章推荐:

为什么PrimeTime修timing时,带physical aware还不如不带physical aware

关于Virtual clock

为什么异步时钟不要设false path