FPGA学习——使用Quartus II+VHDL编写数据选择器和奇偶统计校验器并进行波形仿真

数据选择器

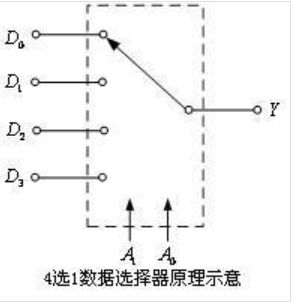

先大致说一下入门时老师会让编写的数据选择器的原理:

数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器

接下来,我们也来做一个用VHDL编写的四选一的选择器,并在Quartus来仿真波形检验

首先新建工程和VHDL就不再赘述。

开头代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;---以上,设计库和程序包调用

接着进行VHDL描述:

ENTITY xuanzeqi IS --VHDL描述起

PORT (a,b,c,d:IN STD_LOGIC;

s0,s1:IN STD_LOGIC;

y:OUT STD_LOGIC); --电路模块端口说明和定义

END ENTITY xuanzeqi; --VHDL描述实体结束

可以看到我们的a、b、c、d是四个数据输入端,y为输出端,s0、s1是地址输入端。

这样就可以利用指定s1、s0的代码,能够从a、b、c、d这四个输入数据中选出任何一个并送到输出端y。

因此,用数据选择器可以实现数据的多路分时传送。

接下来我们继续编写这个程序的灵魂,VHDL结构体描述部分:

ARCHITECTURE BHV OF xuanzeqi IS--VHDL结构体描述部分起

SIGNAL S:STD_LOGIC_VECTOR(1 DOWNTO 0);--结构体说明部分:让s1,s2只有0或1两种值

BEGIN

S<=s1&s0;--将s1,s0并到S中方便控制

PROCESS(s1,s0,a,b,c,d)--敏感信号源

BEGIN--下面是两种选择方法,有过c语言基础并且理解我前面说的应该都能看懂

--CASE(S)IS

--WHEN"00"=>y<=a;

--WHEN"01"=>y<=b;

--WHEN"10"=>y<=c;

--WHEN"11"=>y<=d;

--WHEN OTHERS =>NULL;

--END CASE;

IF S="00" THEN y<=a;

ELSIF S="01" THEN y<=b;

ELSIF S="10" THEN y<=c;

ELSIF S="11" THEN y<=d;

END IF;

END PROCESS;

END ARCHITECTURE BHV; --VHDL结构体描述部分结束

到这里,我们的程序就写完了,源码实测可用。

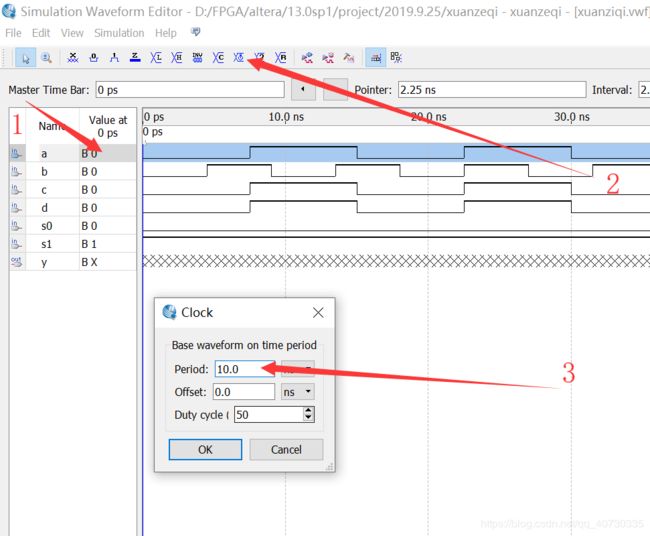

新建一个VMF文件

在这里看到我使用的是周期波形。还有很多仿真波形可以自己试试。记得给s1,s2也赋值,因为它们只能接受0和1所以直接按上面的0、1图标赋值即可。

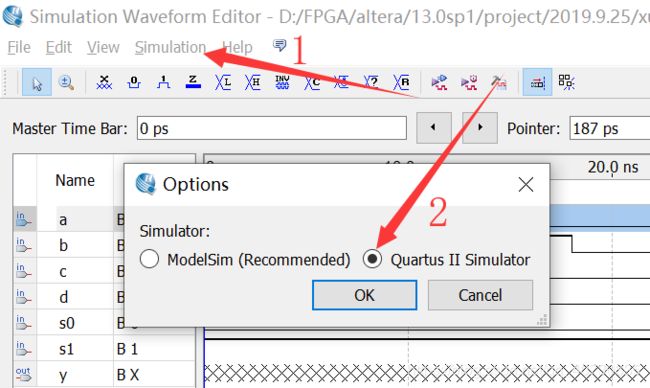

之后我们选择quartus II自带的仿真就可以看到结果。

需要注意的是quartusII自带的仿真一般只适用与学习和实验,真实设计环境下采用modesim或其他仿真。

0/1奇偶统计器

奇偶校验器在现实中是非常实用的

数据的传输总是大量的,传输的数据都是由0和1构成的进制数字组成。

这就导致在数据传输或数字通信中,由于存在噪声和干扰,二进制信息的传输可能会出现差错(0 变为1,或者1变为0)。

为了检验这种错误,常采用奇偶校验的方法。

即在原二进制信息码组后添加一位检验位(监督码元),使得添加校验位码元后整个码组中1码元的个数为奇数或偶数。

若为奇数,称为奇校验;若为偶数,则称为偶校验。

在数据发送端用来产生奇(或偶),校验位的电路称为奇(或偶) 校验发生器。在接收端,对接收的代码进行检验的电路称为奇(或偶) 校验器

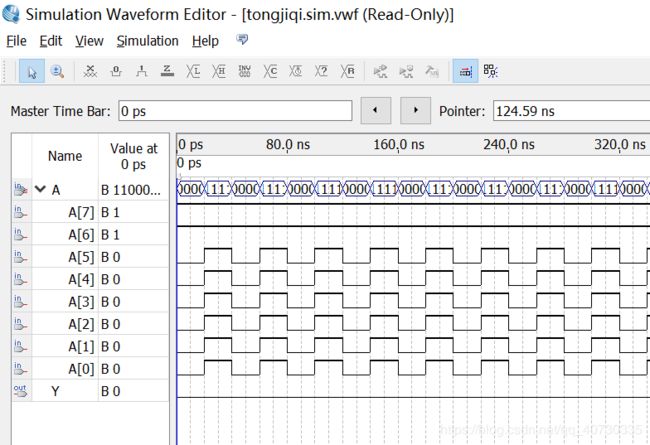

作为新手,我想的是先做一个奇偶统计器,利用较为简单的异或思想,假设我传输的数据是8位二进制。那么将每一位与初始量(我设定为0)异或后,如果1的数量是偶数则会输出0,如果1的数量是奇数则会输出1。

直接放代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;---以上,设计库和程序包调用

ENTITY tongjiqi IS--VHDL描述起

GENERIC(N:INTEGER:=8);

PORT (A:IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

Y:OUT STD_LOGIC);--电路模块端口说明和定义

END ENTITY tongjiqi;--VHDL描述实体结束

ARCHITECTURE BHV OF tongjiqi IS

signal temp:std_LOGIC:='0';

BEGIN

PROCESS(A)

--variable temp:std_LOGIC;--也可以用值的方法

BEGIN

--temp:='0';

for i in 0 to N-1 loop

--temp:=temp xor A(i);

temp<=temp xor A(i);

end loop;

y<=temp;

END PROCESS;

END ARCHITECTURE BHV;

仿真也和之前一样,可以整体赋值或单个赋值。

通过这两个例子,我学到最基本的软件操作和VHDL语言编写,但是实际连FPGA得门框都还没有碰着,也没有想好将来要不要往这方面发展,总之,感谢每一个看到这个得新手和大佬。