从零开始学USB(五、USB的电器特性)

关于机械特性就不在这里详细描述了,这里列出几个重要的知识点。

USB电缆:标准的USB电缆包括一对用于电源分配的20~28AWG规格的线对和一对28AWG规格的双绞线,并具有屏蔽和完整的保护层。

高速(480 Mb / s)和全速(12 Mb / s)要求使用带有两根电源导线和双绞线信号导线的屏蔽电缆。

低速(1.5 Mb / s)建议,但不要求使用带双绞线信号导线的电缆。

连接器设计为热插拔。 插头上的USB图标提供触觉反馈使其易于获得正确的方向。

因为电器特性和功能有关系,这里就需要学习一下了。

全速驱动器的特性(12Mb/s)

通过具有差分特性的屏蔽双绞线电缆实现全速USB连接阻抗(Z0)为90Ω±15%,共模阻抗(ZCM)为30Ω±30%,最大单向延迟(TFSCBL)为26 ns,最大长度5m。当全速驱动器不是高速收发器的一部分时,每个驱动器(ZDRV)的阻抗必须在28Ω和44Ω之间。数据信号上升和下降时间必须在4ns和20ns之间,平稳的上升或下降。

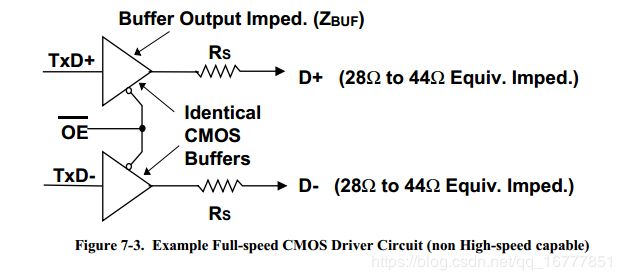

如果使用CMOS驱动器阻抗一般应由一个阻抗小于该阻抗值的CMOS驱动器,以及起补偿平衡作用的一系列离散电阻来实现。

下图给出了一个实例,使用完全两个相同的CMOS缓冲器,CMOS缓冲器的输出阻抗在3Ω到15Ω之间,导线的等效电阻在28Ω到44Ω之间。

低速驱动器的特性(1.5Mb/s)

低速设备必须在插头端带有带A系列连接器的固定电缆 的组合电缆和设备必须具有不低于200 pF且不超过450 pF的单端电容在D +或D-线上。低速电缆的传播延迟(TLSCBL)必须小于18 ns。 这是为了确保在信号上升/下降的前半部分发生反射,这允许电缆近似为a集总电容。

高速驱动器的特性(480Mb/s)

通过具有差分特性的屏蔽双绞线电缆实现高速USB连接阻抗(Z0)为90Ω±15%,共模阻抗(ZCM)为30Ω±30%,最大单向延迟26 ns(TFSCBL)。 D +和D-电路板走线在收发器及其相关的电路之间运行连接器还应具有90Ω的标称差分阻抗,并且它们可以一起添加额外的收发器之间有4 ns的延迟。 高速驱动器的差分输出阻抗要求为90Ω±10%。当D +或D-线被驱动为高电平时,VHSOH(驱动高速模式高电平输出电压对GND负载精度为45Ω的数据线必须为400 mV±10%。在一条未被驱动的线上由于收发器未发送或由于相反的线路被驱动为高电平,因此VHSOL(在带有45Ω负载的数据线上驱动的高速模式低电平输出电压)必须为0 V±10 mV。

注意:除非另有说明,否则所有电压测量都应相对于本地电路进行地面。

注意:此规范要求高速运行的收发器以全速或低速运行模式必须具有45Ω±10%的驱动器阻抗(ZHSDRV)。建议驱动器阻抗为在收发器内匹配到5Ω以内。对于不支持高速的上游面向收发器模式下,驱动器输出阻抗(ZDRV)必须在28Ω至44Ω的范围内。在面向下游的端口上,必须将RPD电阻(15kΩ±5%)从D +和D-连接到地。当高速收发器转换到高速模式时,通过实现高速空闲状态在链路的每端使用低速/全速驱动器驱动SE0(以便提供所需的终端),并通过断开面向上游的收发器中的D +上拉电阻器。在优选实施例中,收发器仅在发送高速信号时激活其高速电流驱动器。然而,这是一个潜在的设计挑战,因为信号幅度和时序规范即使在数据包中的第一个符号也必须满足。作为一种效率较低的替代方案,收发器可能会导致它高速电流源在高速模式下持续工作。当收发器不是在发射时,电流可以被引导到设备地而不是通过电流转向开关用于数据信令。在示例电路中,将电流转向接地是通过实现的设置HS_Drive_Enable为低。在CMOS实现中,驱动器阻抗通常将通过驱动器的组合来实现固有输出阻抗和RS。为了最佳地控制ZHSDRV并使寄生效应最小化,优选的是驱动器阻抗最小化(低于5Ω),45Ω的平衡应由RS提供零件。

当在高速模式下工作的收发器发射时,发射电流被导入D +或D-数据线。通过将电流引导到D +线来确定J,将其引导到D-线。当每条数据线端接45Ω电阻到器件地时,有效负载电阻每侧为22.5Ω。因此,驱动电流所指向的线路上升到17.78 ma *22.5Ω或400 mV(标称值)。另一条线保持在器件接地电压。当电流被指示时在相反的线上,这些电压是相反的。

驱动器的用法

面向上游的功能端口必须使用以下三种驱动程序配置中的一种且仅一种:

1.低速 - 仅限低速驱动

2.全速 - 仅限全速驱动

3.全速/高速 - 组合全速和高速驱动器。

面向上游的USB2.0集线器端口必须使用全速/高速驱动程序(面上主机)。一个高速的驱动器,既可以以高速,也可以以低速或全速传输数据。

面向下游的端口必须支持低速,全速和高速信令,并且必须能够以三种相关数据速率中的每一种传输数据。

将全速/高速设备连接到USB 2.0之前的集线器或高速禁用的集线器端口时,需要将其设置为全速设备。

当全速/高速设备连接到不高速禁用的USB 2.0集线器时,它必须以高速信令和数据速率运行。(优先使用最大速率)

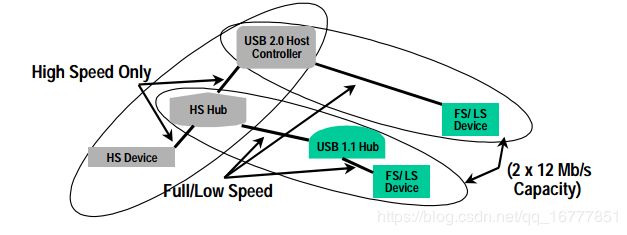

下图是一个USB2.0主机下可以接的设备示意图

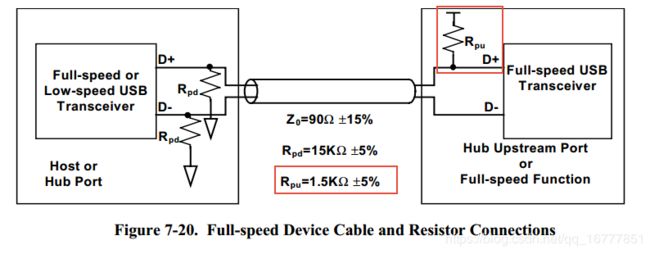

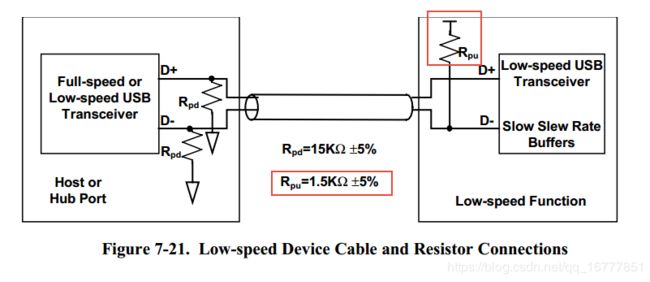

全速和低速器件的区别在于电缆下游端的上拉电阻的位置:

- 全速器件端接,如图7-20所示,D +线上有上拉电阻。

- 低速器件端接如图7-21所示,D-线上有上拉电阻。

- 下游端口上的下拉端接器是15kΩ±5%接地的电阻。

如图7-20和图7-21所示

主机通过设备在D+或D-上的1.5K上拉来检测设备的连接和断开事件,并由此判别设备的速度。

设备连上主机时(连接)

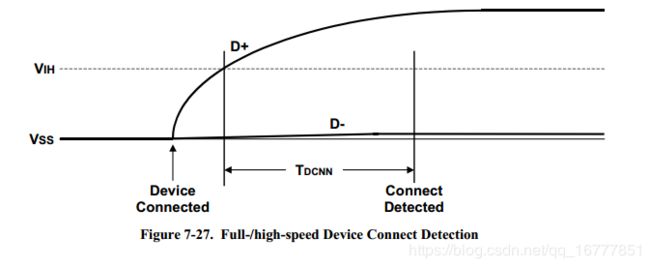

当主机检测到某一个数据线电平拉高并保持了一段时间,就认为有设备连上来了。

假如是低速设备连接上,则D-数据线被拉高。

假如是全速或高速设备,则D+数据线被拉高。

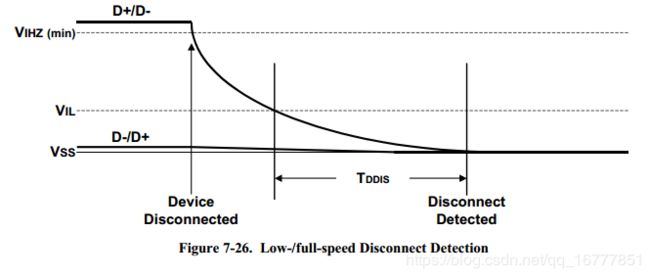

没有设备连上主机时(断开)

D+和D-数据线上主机端的的下拉电阻起作用,使得二者都在低电平;

同样地,当数据线上的低电平状态持续一段时间了,就被主机认为是断开状态

高速复位和检测机制遵循低速/全速的行为模型。

复位完成后,链路必须以适当的信令模式运行(低速,全速或高速,由前面的使用规则控制),端口状态寄存器中的速度指示位将正确报告这种模式。软件只需要在复位完成通知后启动复位断言并读取端口状态寄存器。

高速设备最初作为全速设备连接。这意味着对于具有高速能力的上游端口,RPU(1.5kΩ±5%)必须通过D +连接到3.3 V电源(和全速一样)。

在初始连接之后,具有高速能力的收发器在复位期间参与低级协议,以建立高速链路并在适当的端口状态寄存器中指示高速操作。

下图是我一块STM32开发板上的USB设备的原理图,从图上可以猜测该USB是一个全速的USB端口(因为主CPU控72M,所以不可能是高速)

供电

配电

每个USB段通过电缆提供有限的电量。主机供电,供直接连接的USB设备使用。此外,任何USB设备都可能有自己的电源。

完全依赖电缆供电的USB设备称为总线供电设备。相反,具有替代电源的那些被称为自供电设备。集线器还为其连接的USB设备供电。该架构允许在某些拓扑约束内使用总线供电的集线器。

电源管理

USB主机可以具有独立于USB的电源管理系统。 USB系统软件与主机的电源管理系统交互,以处理系统电源事件,如暂停或恢复。此外,USB设备通常实现额外的电源管理功能,允许它们由系统软件进行电源管理。

USB的配电和电源管理功能使其可以设计为功率敏感系统,如基于电池的笔记本电脑。

通过引入单位负载的概念,可以简化不同设备类别的电源和接收器要求。一个单位负载定义为100 mA。

- 根端口集线器:直接连接到USB主控制器。集线器电源来自与主机控制器相同的源。从外部获得工作电源(AC或DC)的系统必须为每个端口提供至少五个单元负载。这种端口称为高功率端口。电池供电系统可提供一个或五个单位负载。只能提供一个单位负载的端口称为低功率端口。

- 总线供电的集线器:从集线器上游端口上的VBUS为任何内部功能和下游端口抽取所有电源。总线供电的集线器在上电时最多可以吸收一个单元负载,在配置后可以吸收五个单元负载。

- 自供电集线器:内部功能和下游端口的电源不是来自VBUS。但是,集线器的USB接口可以从其上游端口上的VBUS吸取一个单元负载,以允许接口在集线器的其余部分断电时起作用。从外部获取工作电源的集线器(来自USB)必须为每个端口提供五个单元负载。电池供电的集线器可以为每个端口提供一个或五个单元负载。

- 低功耗总线供电功能:这些设备的所有电源均来自VBUS。他们可以随时抽取不超过一个单位负荷。

- 大功率总线供电功能:这些设备的所有电源均来自VBUS。它们在上电时必须承受不超过一个单位负载,并且在配置后可以最多抽取五个单位负载。

- 自供电功能:可以从VBUS吸取一个单位负载,以便在功能的其余部分断电时使USB接口正常工作。所有其他电源均来自外部(USB)电源。