ARM cortex-M4 软件复位设计

在嵌入式开发项目过程中,经常需要执行软件复位,基于ARM cortex-M4核的芯片,通过控制系统控制模块(System Control Block)的中断和复位寄存器可以实现设备的软件复位, 这种复位实现软件从开始运行,复位CPU的主要组件,除过调试模块。

寄存器介绍

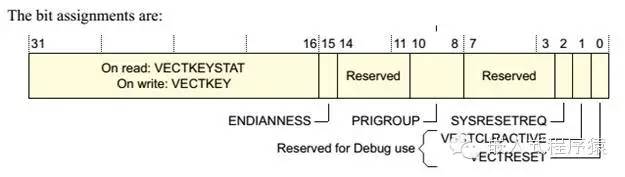

基于ARM cortex-M4内核的芯片软件复位功能的实现是通过应用中断和复位控制寄存器(AIRCR)实现的,复位只与寄存器中的第2位,16~31位有关。下图是寄存器位的详细描述。

如果想写这个寄存器,必须先给VECTKEY域写0x5FA,负责寄存器将忽略写操作。SYSRESETREQ位,为系统复位请求位,写0,无复位请求,写1请求复位。这一位是只写位,读为0。

实现方案

知道了寄存器的定义后,如何通过软件来实现复位这一功能呢,有两种方案。

一种是直接调用ARM公司提供的core_cm4.h文件中的复位函数。对照寄存器,这个函数应该很好理解,ARM公司提供的是内联函数。

/** \brief System Reset

The function initiates a system reset request to reset the MCU.

*/

__STATIC_INLINE void NVIC_SystemReset(void)

{

__DSB(); /* Ensure all outstanding memory accesses included

buffered write are completed before reset */

SCB->AIRCR = ((0x5FA << SCB_AIRCR_VECTKEY_Pos)|

(SCB->AIRCR & SCB_AIRCR_PRIGROUP_Msk) |

SCB_AIRCR_SYSRESETREQ_Msk); /* Keep priority group unchanged */

__DSB(); /* Ensure completion of memory access */

while(1); /* wait until reset */

}

这里主要说下__DSB(), DSB(Data Synchronization Barrier.)这里插入DSB的指令函数是为了确保内存操作访问的完成。

另一种方案是自己按照数据手册对寄存器的描述实现复位功能的函数。如果是自己写函数实现,建议也插入DSB指令函数确保内存访问安全。

#define SCB_AIRCR_VECTKEY_SHIFT 16

#define SCB_AIRCR_PRIGROUP_MASK 0x700u

#define SCB_AIRCR_SYSRESETREQ_MASK 0x4u

void System_vReset(void)

{

__DSB();/* Ensure all outstanding memory accesses included

buffered write are completed before reset */

SCB_AIRCR = ( (0x5FA << SCB_AIRCR_VECTKEY_SHIFT) |

SCB_AIRCR_PRIGROUP_MASK |

SCB_AIRCR_SYSRESETREQ_MASK);

__DSB(); /* Ensure completion of memory access */

while(1); /* wait until reset */

}

总结

由于芯片厂商的数据手册都是基于自己芯片的描述,涉及ARM内核的知识需要参考ARM官方文档,基于ARM cortex-M4内核的芯片,可以参考ARM官方文档DUI0553A_cortex_m4_dgug,飞思卡尔kv4xMCU的复位同样涉及到ARM cortex-M4内核的操作,在飞思卡尔参考手册上是没有详细信息的,需要参考ARM的官方文档,建议大家在学习ARM时候,需要熟悉下内核知识。

嵌入式

程序猿

嵌入式程序猿致力于打造程序猿工程师交流分享的精品移动平台,欢迎各位猿友加入和分享。微信搜索嵌入式程序猿添加关注,或者长按下方二维码,选择识别图中二维码添加关注。

![]()

![]()