浅谈ARM存储系统之cache

通常来讲,ARM处理器的主频为几十M甚至上百M,而一般的SDRAM的存储周期是很慢的,相对于CPU来说,这时,如果我们把程序和数据都存储在SDRAM中,那么CPU在读取指令和数据的时候,就会受到SDRAM速度的限制,大大地制约了整个系统的性能。那么有没有什么改善的办法呢?下面我们就来谈一下ARM的高速缓冲存储器(cache)。

一,Cache的概念及工作原理

1.1 概念

Cache 即高速缓冲存储器,是位于 CPU 与内存之间的高速存储器,它的容量比内存小但交换速度快。在 cache 存储系统中,把主存储器和 cache 都划分成相同大小的块。主存地址由块号 B和块内地址 W 两部分组成。同样, cache 的地址也由号 b和块内地址w 组成。然而 cache 是相连存储器,装入时,通过址变换部件把主存地址中的块号 B 变成 cache 的块号 b,W 保存在块号为 w的 cache 块的标记区,数据块装入 cache 缓冲区。它的出现是为了解决上面说的问题,当CPU在一段相邻的时间内反复访问相同的数据(时间局部性)或者CPU有很大概率访问相邻存储空间的数据(空间局部性)时,我们就可以使用Cache来优化CPU性能。

1.2 工作原理

当CPU 要访问 cache 时, CPU 送来主存地址,放到主存地址寄存器中。然后通过地址变换部件把主存地址中的块号 B 变成 cache 的块号b,并放到 cache 地址寄存器当中。同时将主存地址中的块内地址 W 直接作为 cache 的块内地址 w装入到 cache 地址寄存器中。如果地址变换成功(通常称为 cache 命中),就用得到的 cache 地址去访问 cache,从 cache 中取出数据送到 CPU 中。如果地址变换不成功,则产生 cache 失效信息,并且接着使用主存地址直接去访问主存储器 。

1.程序要读取内存中地址A数据,然后程序首先以地址A查找Cache,一开始Cache无数据,导致“cache miss”。

2.程序以地址A查找内存,读取数据后,把数据填入cache,称为”cache fill“。

3.程序再次读取内存中A地址数据,这次直接以地址A查找cache,读取数据后直接返回给CPU,不用再去操作内存。

4.重复步骤1,周而复始,直到把cache填满(cache容量一般很小)。此时CPU再访问,就要发生cache替换,即把一些数据替换出去,填充新数据。

二,Cache的分类

2.1统一/独立的指令cache和数据cache

2.2写通(write -through)cache和写回(write-back)cache

当CPU更新cache内容时,通常有两种方法,写通法和写回法。

写通法是指CPU在执行写操作时,必须把数据同时写入cache和内存。写回法是指被写的数据只写入cache而不写入内存,仅仅当需要时,才把已经修改的cache块写回到内存中。

三,协处理器指令介绍及开启icache

3.1协处理器指令介绍

先来看看协处理器是什么。

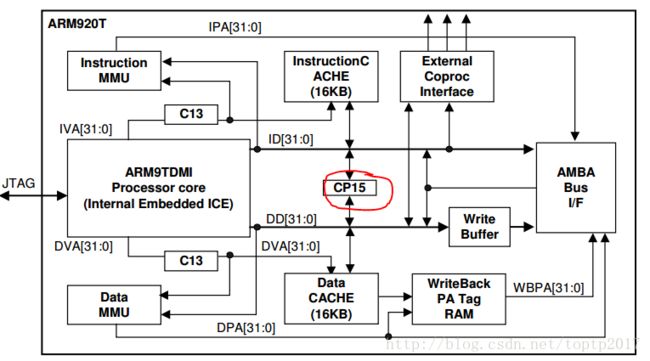

如图,这是ARM9的框图,红线标出的即为协处理器,ARM9的cache由协处理器CP15管理。顾明思义,协处理器就是协助CPU处理事件的处理器。下面是协处理器指令介绍:

如上图,有两条指令,MCR(从ARM寄存器到协处理器寄存器)和MRC(从协处理器寄存器到ARM寄存器)。

示例:从cp15的c1写入arm的r0------MRC p15,0,r0,c1,c0,0

3.2使用协处理指令开启icache

在S3C2440的启动代码start.s中,我们添加如下代码:

enable_icache:

/* 设置协处理器使能icache */

mrc p15, 0, r0, c1, c0, 0

orr r0, r0, #(1<<12) /* r0 = r0 or (1<<12) :设置c1 bit12 = 1,使能icache*/

mcr p15, 0, r0, c1, c0, 0

mov pc, lr这里我们只是开启了指令cache,可以明显感觉到程序的运行效率提高了,如果再同时开启数据cache,程序运行效率会更高。

欢迎交流:qq1257737697