NG Toolset开发笔记--5GNR Resource Grid(47)

1/26 update: recvSib1 is ok now.

monitorPdcch returns (hsfn, sfn, slot) indicating the detected DCI 1_0(with RNTI=SI-RNTI for SIB1 scheduling).

#receiving SSB

nrGrid.recvSsb(hsfn, sfn)

#monitoring PDCCH for SIB1

hsfn, sfn, slot = nrGrid.monitorPdcch(hsfn, sfn, dci='dci10', rnti='si-rnti')

if hsfn is not None and sfn is not None and slot is not None:

#receiving SIB1

nrGrid.recvSib1(hsfn, sfn, slot)For PDSCH VRB-to-PRB interleaved mapping procedure:

Note 1: 38.211 defines 3 cases for VRB-to-PRB interleaved mapping:

case#1: when DCI1_0 with SI-RNTI in Type0 CSS/Coreset0; for SIB1

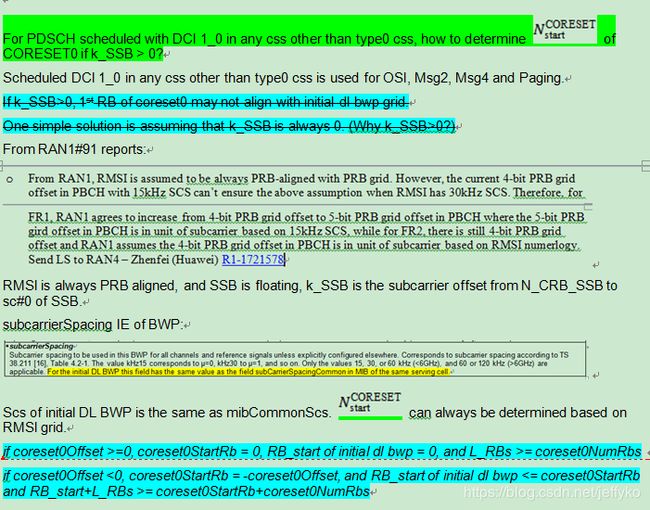

case#2: when DCI 1_0 in any CSS other than Type0 CSS; for OSI(Type0A CSS), Paging(Type2 CSS), Msg2/Msg4(Type1 CSS)

case#3: all other cases;

Note 2: there are 3 paramters for case#1 and case#2:

*![]() , which is coreset0Size in dci10CssVrb2PrbMapping

, which is coreset0Size in dci10CssVrb2PrbMapping

*![]() , which is iniDlBwpStart in dci10CssVrb2PrbMapping

, which is iniDlBwpStart in dci10CssVrb2PrbMapping

*![]() , which is coreset0Start in dci10CssVrb2PrbMapping

, which is coreset0Start in dci10CssVrb2PrbMapping

Note 3: case#1 is a special case of case#2 when iniDlBwpStart = coreset0Start = 0

Note 4: Further analysis on coreset0Start:

def dci10CssVrb2PrbMapping(self, coreset0Size=48, iniDlBwpStart=0, coreset0Start=0, L=2):

#FIXME The UE is not expected to be configured with Li=2 simultaneously with a PRG size of 4 as defined in [6, TS 38.214].

self.ngwin.logEdit.append('calling dci10CssVrb2PrbMapping: coreset0Size=%d,iniDlBwpStart=%d,coreset0Start=%d,L=%d' % (coreset0Size, iniDlBwpStart, coreset0Start, L))

numBundles = math.ceil((coreset0Size + (iniDlBwpStart + coreset0Start) % L) / L)

rbBundleSize = []

for i in range(numBundles):

if i == 0:

rbBundleSize.append(L - (iniDlBwpStart + coreset0Start) % L)

elif i == numBundles - 1:

rbBundleSize.append((coreset0Size + iniDlBwpStart + coreset0Start) % L if (coreset0Size + iniDlBwpStart + coreset0Start) % L > 0 else L)

else:

rbBundleSize.append(L)

vrbBundles = list(range(numBundles))

prbBundles = []

for j in range(numBundles):

if j == numBundles - 1:

prbBundles.append(j)

else:

R = 2

C = math.floor(numBundles / R)

c = j // R

r = j % R

fj = r * C + c

prbBundles.append(fj)

#indexing vrbs and prbs

prbs = []

for j in range(numBundles):

for k in range(rbBundleSize[j]):

prbs.append(sum(rbBundleSize[:prbBundles[j]]) + k)

#print info

self.ngwin.logEdit.append('contents of rbBundleSize: %s' % rbBundleSize)

self.ngwin.logEdit.append('contents of vrbBundles: %s' % vrbBundles)

self.ngwin.logEdit.append('contents of prbBundles: %s' % prbBundles)

self.ngwin.logEdit.append('contents of prbs: %s' % prbs)

return prbsFor DMRS for PDSCH determination:

Note 1: getDmrsPdschTdFdPattern returns (tdL, fdK) of DMRS-for-PDSCH, where tdL is time-domain symbols, fdK is freq-domain locations in a single PRB.

def getDmrsPdschTdFdPattern(self, dmrsType, tdMappingType, slivS, slivL, numFrontLoadSymbs, dmrsAddPos, cdmGroupsWoData):

if tdMappingType == 'Type A':

tdL0 = 3 if self.nrMibDmRsTypeAPosComb.currentText() == 'pos3' else 2

tdLd = slivS + slivL

else:

tdL0 = 0

tdLd = slivL

if numFrontLoadSymbs == 1:

tdLbar = self.nrDmrsPdschPosOneSymb['%s_%s_%s' % (tdLd, tdMappingType, dmrsAddPos)]

tdLap = [0] #ap for apostrophe, the (' or ’) character

else:

tdLbar = self.nrDmrsPdschPosTwoSymbs['%s_%s_%s' % (tdLd, tdMappingType, dmrsAddPos)]

tdLap = [0, 1] #ap for apostrophe, the (' or ’) character

tdLbar = list(tdLbar)

tdLbar[0] = tdL0

tdL = []

for i in tdLbar:

for j in tdLap:

tdL.append(i+j)

#freq-domain DM-RS pattern in a single PRB

if dmrsType == 'Type 1':

fdN = [0, 1, 2]

fdKap = [0, 1]

if cdmGroupsWoData == 1:

fdDelta = [0]

else:

fdDelta = [0, 1]

else:

fdN = [0, 1]

fdKap = [0, 1]

if cdmGroupsWoData == 1:

fdDelta = [0]

elif cdmGroupsWoData == 2:

fdDelta = [0, 2]

else:

fdDelta = [0, 2, 4]

fdK = [0] * self.numScPerPrb

for i in fdN:

for j in fdKap:

for k in fdDelta:

isc = 4*i+2*j+k if dmrsType == 'Type 1' else 6*i+j+k

fdK[isc] = 1

return (tdL, fdK)Example of recvSib1:

Configurations:

contents of ["freqBand"]: {'opBand': 'n77', 'duplexMode': 'TDD', 'maxDlFreq': 4200, 'freqRange': 'FR1'}

contents of ["ssbGrid"]: {'scs': '30KHz', 'pattern': 'Case C', 'minGuardBand240k': 'NA', 'kSsb': '0', 'nCrbSsb': '4'}

contents of ["ssbBurst"]: {'maxL': 8, 'inOneGroup': '11111111', 'groupPresence': 'NA', 'period': '20ms'}

contents of ["mib"]: {'sfn': '0', 'hrf': '0', 'dmrsTypeAPos': 'pos2', 'commonScs': '15KHz', 'rmsiCoreset0': '0', 'rmsiCss0': '0', 'coreset0MultiplexingPat': 1, 'coreset0NumRbs': 48, 'coreset0NumSymbs': 1, 'coreset0OffsetList': (2,), 'coreset0Offset': 2, 'coreset0StartRb': 0}

contents of ["carrierGrid"]: {'scs': '15KHz', 'bw': '10MHz', 'numRbs': '52', 'minGuardBand': '2'}

contents of ["pci"]: 0

contents of ["numUeAp"]: 4Tx

contents of ["tddCfg"]: {'refScs': '15KHz', 'pat1Period': '5ms', 'pat1NumDlSlots': '3', 'pat1NumDlSymbs': '10', 'pat1NumUlSymbs': '2', 'pat1NumUlSlots': '1', 'pat2Period': 'not used', 'pat2NumDlSlots': '', 'pat2NumDlSymbs': '', 'pat2NumUlSymbs': '', 'pat2NumUlSlots': ''}

contents of ["css0"]: {'aggLevel': '4', 'numCandidates': 'n4'}

contents of ["dci10Sib1"]: {'rnti': '0xFFFF', 'muPdcch': '0', 'muPdsch': '0', 'tdRa': '0', 'tdMappingType': 'Type A', 'tdK0': '0', 'tdSliv': '53', 'tdStartSymb': '2', 'tdNumSymbs': '12', 'fdRaType': 'RA Type1', 'fdRa': '00010010011', 'fdStartRb': '3', 'fdNumRbs': '4', 'fdVrbPrbMappingType': 'interleaved', 'fdBundleSize': 'n2', 'mcsCw0': '0', 'tbs': '120'}

contents of ["dmrsSib1"]: {'dmrsType': 'Type 1', 'dmrsAddPos': 'pos2', 'maxLength': 'len1', 'dmrsPorts': '0', 'cdmGroupsWoData': '2', 'numFrontLoadSymbs': '1'Debug info of getDmrsPdschTdFdPattern:

'tdL': [2, 7, 11], 'fdK': [1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1]

contents of sib1DmrsSymbs(w.r.t to slivS): [0, 5, 9]Debug info of dci10CssVrb2PrbMapping:

calling dci10CssVrb2PrbMapping: coreset0Size=48,iniDlBwpStart=0,coreset0Start=0,L=2

contents of rbBundleSize: [2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2, 2]

contents of vrbBundles: [0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23]

contents of prbBundles: [0, 12, 1, 13, 2, 14, 3, 15, 4, 16, 5, 17, 6, 18, 7, 19, 8, 20, 9, 21, 10, 22, 11, 23]

contents of prbs: [0, 1, 24, 25, 2, 3, 26, 27, 4, 5, 28, 29, 6, 7, 30, 31, 8, 9, 32, 33, 10, 11, 34, 35, 12, 13, 36, 37, 14, 15, 38, 39, 16, 17, 40, 41, 18, 19, 42, 43, 20, 21, 44, 45, 22, 23, 46, 47]