Cadence Design Entry HDL 使用教程

Cadence Design Entry HDL 使用教程

前言

cadence Design Entry HDL是cadence内部集成的一款板级的EDA设计工具,早期叫 concept HDL。其为cadence最早的原配板级电路图绘制工具,只不过由于后来cadence收购了orcad然后就将旗下的capture CIS收入其中,由于后者使用起来上手简单,所以后者更为大家所熟知。虽然大家对于EDA工具的使用主流是capture CIS, 但是concept HDL依然有着强大的软件特色和魅力。由于其实cadence最早的原理图绘制工具,因此此软件对于和allegro的配合也最为贴合,两个软件均支持stroke手势操作,同时原理图和PCB之间的交互也颇为密切,能够支持在原理图中选中器件后,PCB中能够实时的高亮该器件,对于原理图的查看非常便捷,此外对于工程设计,concept HDL非常适合于工程管理,每一个工程均为一个独立的文件夹,工程下面不可拆分,元件库也可独立被打包进来,因此管理起来更加的便利。此外由于此软件的元件库是高度封装的,原理图中只能调用器件不能修改器件的属性,因此其最大程度的从源头上来减少设计人员在设计过程中的错误,(前提是已经有一个已经设计好的完善的元件库,否则元件库建立的过程会非常痛苦,这也是此软件被大家诟病的地方)。

本文主要从以下几个方面介绍一下这个软件,一个是软件整体情况介绍,也就是介绍这个软件张啥样,然后怎么打开,第二就是介绍如何建立工程和打开工程,第三就是原理图绘制细节,包括走线,放置器件等相关操作,第四就说明一下完成绘制后的一些操作,包括DRC检查,PCB映射之类的,还有打印输出PDF,产生BOM。最后再简单描述下原理图库的建库方法,不一定正确。

目前先讲这么多,后续补充 PCB设计的一些操作。仿真,包括信号完整性仿真和电源完整性仿真。以及一个用来帮助FPGA前期设计用的 FPGA planner,可以用来在设计前就给分配好管脚,可以简化后续的操作。

目录

- Cadence Design Entry HDL 使用教程

- 前言

- 目录

- 第一章 Design entry HDL原理图绘制

- 1、创建工程

- 1.1、打开软件

- 1.2、建立工程

- 1.3、主界面介绍

- 1.4、设置元件库

- 2、绘制原理图

- 2.1 原理图绘制窗口简介

- 2.2 绘制前环境的修改适配等

- 原理图字体的修改设定

- 修改颜色

- 修改栅格点

- 修改层次查看器 hierarchy viewer

- 常规

- 2.3开始绘制前快捷操作的设置

- stroke

- 快捷键操作

- 2.4 添加和修改页面边界

- 添加页边界

- 修改或建立新的page border

- 2.5 放置元器件与互联

- 放置器件

- 走线

- 放置总线

- 走线命名

- 放置vcc,port端口等

- 放置VCC gnd

- 放置offpage

- 放置 replicate 位宽变换符号

- 添加文字备注

- 注意事项

- 3、原理图修改与检查

- 3.1 基础移动、复制、修改、替换

- 移动

- 建立group

- 复制操作

- 器件替换

- 电路图旋转,镜像

- 文本和属性的修改

- 显示和隐藏操作

- 显示管脚序号

- 3.2 全局修改替换

- global update 修改

- part manager 修改

- 命令行修改操作

- 3.3 原理图页的删除移动

- 3.4 原理图检查

- 3.1 基础移动、复制、修改、替换

- 4、原理图导出文件、交叉索引,打包,归档

- 4.1 导出bom

- 4.2 交叉索引

- 4.3 工程打包

- 4.4 工程归档

- 5、附录

- 1、创建工程

- 第二章 建立元件库

- 建立库工程

- 创建元件

- 第三章 allegro PCB 绘制

- 第四章 PCB仿真

- 第五章 FPGA planner

- 参考文献

第一章 Design entry HDL原理图绘制

1、创建工程

1.1、打开软件

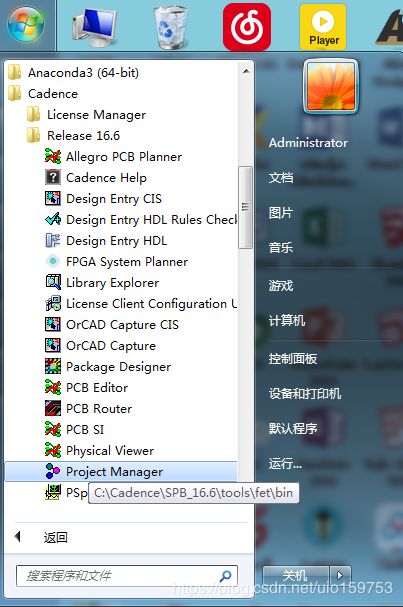

通过开始菜单,找到cadence的目录,然后找到其中的project manager 此工具就是整个软件后续的打开的窗口,原理图和layout都是从这里操作,

打开之后需要选择工具,图中圈出的是一般常用的两个,一个是原理图工程选项,还有一个是原理图库工程选项,注意:原理图工程是不能够创建元件的,即便是进入了元件库也不能看到元件的symbol

通过选择原理图工程之后进入到如下的界面![]()

三个选项,一个是创建工程,一个是打开工程,还有一个是建立库工程,这里现在只介绍前两个。

1.2、建立工程

点击建立工程之后见到如下界面,按照上面的输入工程名字和地址就行,注意工程名不能有大写![]()

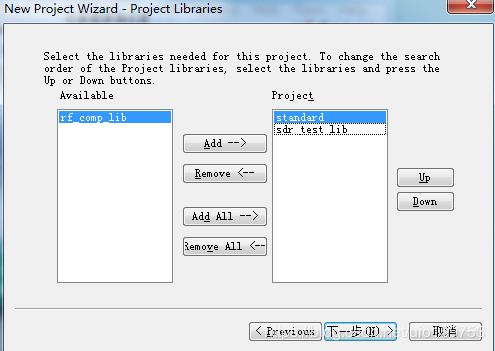

然后就下一步添加元件库,元件库的添加下面会讲,这里也可以预先添加一部分全局库里头的库,看需求

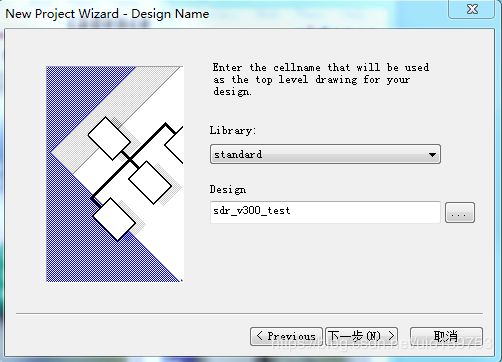

然后下一步设置原理图的名字,按照逻辑一个工程里面可以有几个design,也就是原理图。同样,不能有大写

然后就成功了

1.3、主界面介绍

整体的软件的工程架构如上图所示包含原理图入口,design entry ,PCB入口layout,以及将PCB与schematic进行关联的design sync,进行layout仿真的floor planner和一个设置按键,

1.4、设置元件库

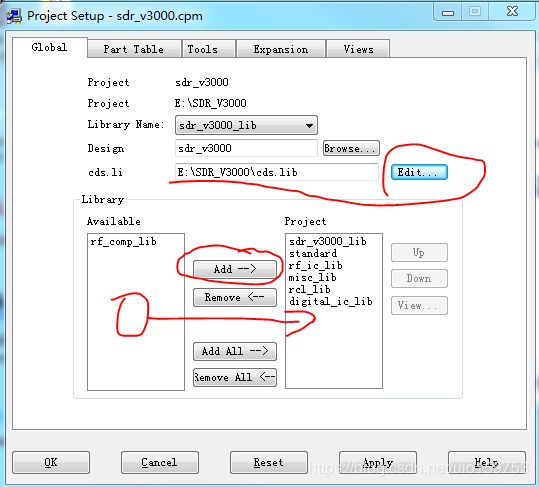

此界面一个比较重要的是setup按键,此处决定可以用来添加原理图库,进去后的界面如下

点击图中的edit可以进入一个文本页面进行对原理图库的地址的编辑,具体界面如下,

DEFINE sdr_v3000_lib worklib

INCLUDE $CONCEPT_INST_DIR/share/cdssetup/cds.lib

DEFINE rf_ic_lib component_lib/rf_ic_lib

DEFINE digital_ic_lib component_lib/digital_ic_lib

DEFINE rcl_lib component_lib/rcl_lib

DEFINE misc_lib component_lib/misc_lib

元件库的添加均是通过命令行来操作,具体的格式为:define+元件库名+元件库文件夹地址;

一般的文件夹地址默认为工程文件夹目录,自己可以如参考所示建立一个大的文件夹来放库。另外还有一种方式建库就是全局的库,具体如include这行所示,此库统一放置在软件安装目录下的share文件夹下,具体想添加啥可以在哪个cds.lib文件里面编辑(后续对工程打包的时候这个用到的库会被打包进入工程里头,)。注意器件库的名字不能出现大写,不然会出错,认不出库。

编辑完成库之后需要照图示将需要的库逐一添加进工程里面。此处提示那个worklib是原理图的库,cadence将原理图也打包成了一个元件的样子,还有那种原理图的block也是一样也被封成一个元件的样子,这两个都是在这个库里头,不能删掉,还有一个是rf_comp_lib,这个库不要添加,这个就是个元器件示意图的库,没有啥具体的参考价值,如果要layout这个库用不上,另一个就是strand_lib,这个库是一些原理图页面边界,电源,地,总线入口等杂七杂八的库的集合,这个要添加。

至此,元件库就添加完成了,(其他的就不要动了)

另: 如果全部的库都放在全局库里头,那这一步就直接跳过,不设置就行。

2、绘制原理图

2.1 原理图绘制窗口简介

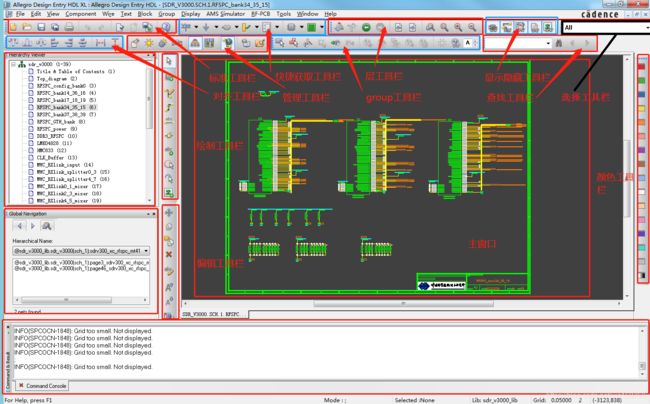

这个软件的窗口就是如上所示,

这个软件的窗口就是如上所示,

原理图页面导航窗口是显示页面目录的地方,

全局导航,这个主要是在相同网络查找的时候有用,将鼠标选中一根信号线,相同网络名称的信号线变回显示在这里,可以任意点击进行跳转,

命令行窗口主要是输入命令行用的,有些操作可以通过输入命令行代码的形式来实现便捷的操作,具体后面介绍

主窗口就是绘制原理图页面的地方,

以上时全部主要要用到的窗口,工具栏的情况如下图所示

绘制工具栏主要是用来绘制连接线以及放置器件之类的,

管理工具栏主要是一些器件和信号的高亮查看,元器件的管理,约束规则的设置等,

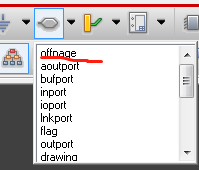

快速获取工具栏主要是用来放置一些standard库下的器件,包括常用的VCC。GND,还有offpage,以及原理图页面和总线入口,还有就是总线接口转单端的辅助元件,

group工具栏主要是对器件做一个group(组)的操作,可以对一堆的器件进行复制、删除、移动等操作,同时也可以对一类相同属性的东西进行统一的修改,例如,修改颜色,字体大小等。

显示工具栏主要是对部分的器件进行显示和隐藏的操作,在框选器件或者信号线的时候贼有用,

查找工具栏主要是用来查找器件等的工具栏,后面具体讲。

颜色工具栏主要是对信号线和文字类的属性改变颜色用的

编辑工具栏 主要是对一些需要图中的元素进行旋转复制删除等操作,

对齐工具栏 主要是一些对齐操作的工具包括左对齐,右对齐,居中对齐啥的

标准工具栏 这个主要是一些打开,保存啥的,还有就是新建页面之类的操作,

层工具栏,主要是用在层次化原理图中的上下层电路的跳转,当然此工具栏还可以用来通过此工具栏来进行一些元件的修改,后续会讲到,主要是原理图页面的编辑。

选择工具栏选择工具栏可以用来选择框选的时候特定框选某一个特定类型的东西,例如选择note的时候就只框选note,

2.2 绘制前环境的修改适配等

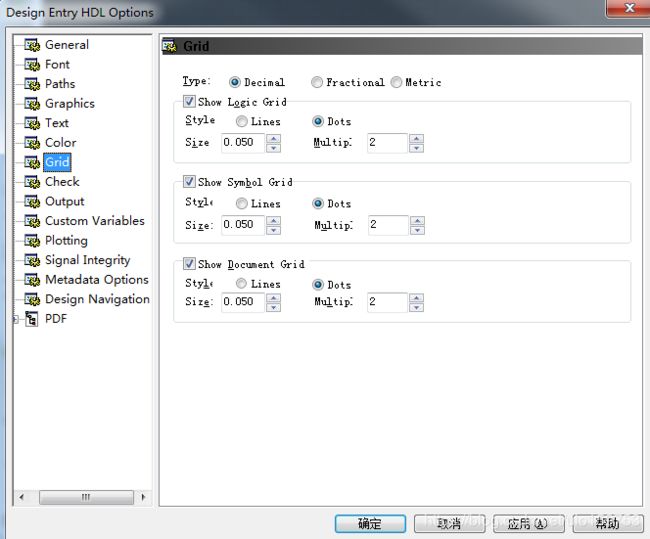

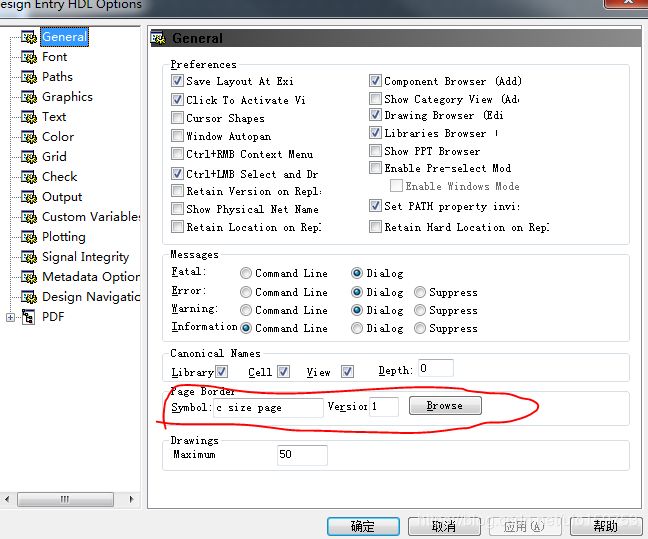

tool -> options 可见到如下的页面![]()

可以看到弹出窗口可以修改的内容大致如左列所示,包括字体,栅格点,颜色,以及设计导航(这块修改后可以改pagename)。

原理图字体的修改设定

点击front就可以修改了,具体如下图所示,没啥特别要注意的,想改啥改啥,要觉得默认字体比较大改小也可以,默认的字体颜色兼容适配黑色背景,就是不改的话,不管白色背景还是黑色背景都可以看,对黑色背景更友好些,唯一要注意的是原理图中备注文字需要的note的字体在最下头看不见,要在哪个custom text下面一点点点一下他就会蹦出来。还有一点就是这些字体颜色都没有那种mono色,就是黑白色,如果想弄这种可以原理图里头自己改,也行。

修改颜色

这里头的颜色都是全局的颜色显示,包括图形的显示颜色,走线,连接点,元件的图形,元件属性高亮操作等,还有一个就是背景颜色,前面那些一般都不动,一般就是改个背景颜色,业内比较喜欢的是黑色背景,个人觉得太黑了有些显示看的不舒服,所以我一般调成dark_gray 黑灰色。

修改栅格点

改栅格点就按照下面的来改就行,软件默认的栅格点不大好用,太大了,就都改成0.05就行,别改太小,太小会很崩溃的,很容易就给画错来多出一截线,元器件的管脚间距一般都是0.1的。这样正好合适。

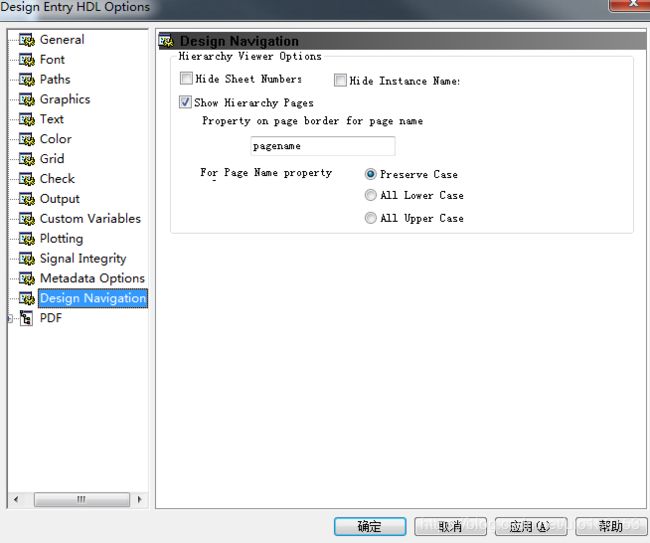

修改层次查看器 hierarchy viewer

这个主要就是主界面的那个层次化的窗口的显示设置,比较重要的一个是如果想要能够像上面的那个图片一样显示的是每一个页面的名字而不是page1之类的话要按照下面的样子,把show hierarchy pages 给勾上,同时为页面边界的属性命一个名字,这个名字随意,可以不跟下面的一样,随便起。

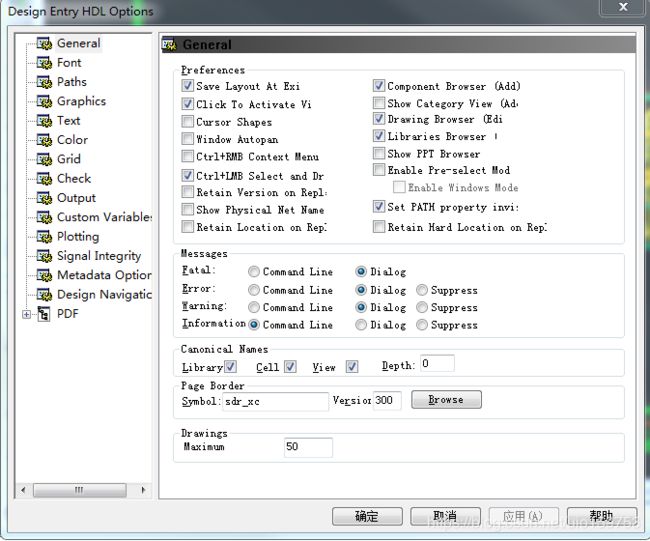

常规

这个选项主要是一些比较杂的选项,包括操作按键的,显示之类的,

-

一般主要修改的话有 set path property invisible,这个勾上就不会显示那些path的属性了,这个通常意义上不太关注,

-

还有一个就是ctrl + LMB select and Dr... 这个就是说是如果你不喜欢ctrl 加左键进行框选器件的话,可以把这个勾去掉,去掉之后,ctrl加左键就变成了stroke的手势,我个人比较喜欢默认的操作,别去掉勾,因为这样操作手势很方便。

-

建议勾上 enable Pre-select mode ,这可勾上之后可以旋转电路,省不少事儿。否则只能旋转器件。

目前基本上来说就这些了,其余没啥要改的了。

2.3开始绘制前快捷操作的设置

软件主要的快捷操作有两方面, 一个是stroke的手势,还有一个就是快捷按键

这两个配合使用会极大提升工作效率,比Altium designer ,capture CIS之类的还要方便,

stroke

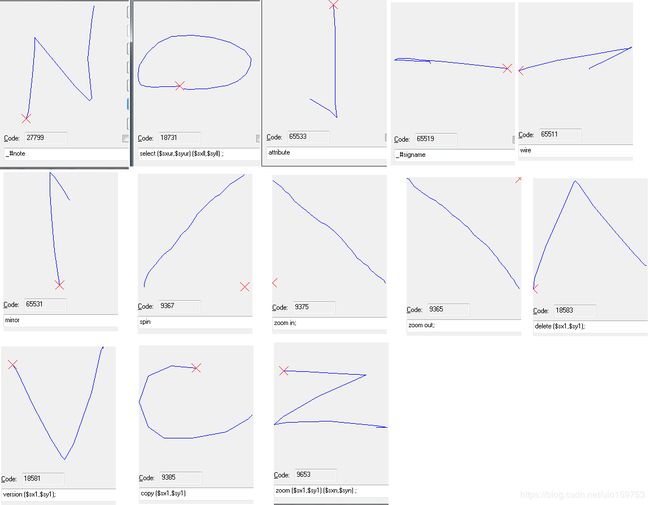

手势操作的使用就是,如果默认没有改过设置的话,按住鼠标左键就是画手势,默认有一套手势,大概是画"R"是route,画“C”是复制 ,画“^”是删除,画“Z”是zoom fit 。但是这些操作还是不够,除了这些还算比较好记的,其他的手势就不太好用了,所以为了使用常常需要自己备一套自己的手势,

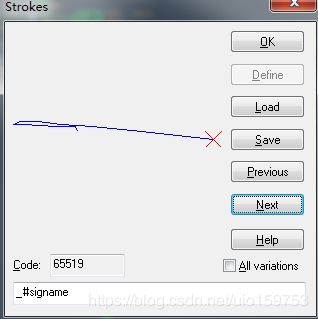

进入手势没有按键或菜单选择,只能通过命令行输入 stroke 然后会弹出如下的窗口

可以通过next 来进行查看,下一个是啥,如果想要重新建立一个手势的话就直接画就行,然后下面对应想要执行的命令,设置完了之后点define,然后就关联成功了,具体如下所示:

这个就是关联了一个手势用来输入信号名,这些命令都可以自己画图的时候留意,因为每执行一个操作,都会有对应的手势的,还有一点就是,手势的命令里头如果末尾有分号就表示单次操作,如果没有分号就表示可以多次操作,要右键done之后才能结束。

如果全部都定义完了之后记住一定要保存,就是点save,然后会把手势给保留成一个文件,然后每次打开软件之后加载一次就行。

如果直接加载的话其命令为 loadstroke,之前我通过使用快捷键来操作,也挺方便。

还有一个一劳永逸的办法,就是改软件默认的stroke,在软件安装目录下

C:\Cadence\SPB_16.6\tools\fet\concept,

里面的concept.stroke文件,就是默认的stroke,只要把我们自己定义的手势改成这个名字替换掉就行。

快捷键操作

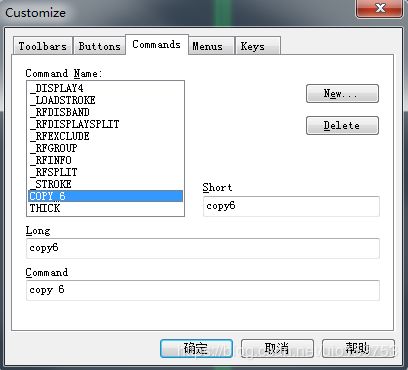

快捷键操作需要设置两个一般,一个是设置命令名,一个是设置按键,

操作为 tool -> customize,

上图的下面两个就是我自己定义的命令,主要要注意的是命令对了就行,其他的short long啥的都不太重要,

然后就是去设定对应的按键,具体如下图所示:

需要注意的就是在press new这里按下自己想要的快捷按键,然后点add key。然后确认就行了 。

2.4 添加和修改页面边界

添加页边界

通过上述的操作大环境就整好了

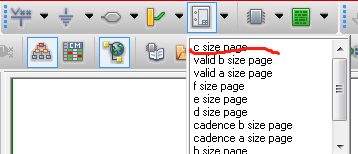

然后需要添加页面边界才可以画图,具体操作如下图

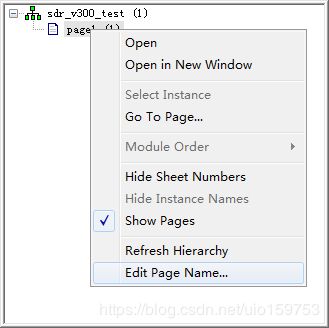

cadence默认提供多种的样式的页边界,一般选C就可以,差不多跟A3大小,添加进来之后保存,然后修改page名,具体如下:

点击Edit Page Name,注意,不要使用类似windows的重命名方式直接修改,那样是没有用的,再打开还是没有,另外,这块可以编辑的前提是已经在上一步改了那个 design navigation,添加了属性名称,否则这块是灰色的改不了。

做到上面这步就可以直接添加器件画图了,

另外,如果想要每次新建页面就可以直接有page border的话需要在tool -> options - > general 的page border 框里选择每次要自动加载的page border 还有版本号,具体如下图

修改或建立新的page border

这种情况下可以自己随意修改线条,还有添加字符之类的

一般主要修改的是表头,具体如下图所示

上述事例中的粉色字体是note,在正常的原理图中会是绿色的不能够选择和修改,只能在这里进行修改,然后还有一个常规操作是添加自定义的文本

可以添加如图的页码,设计名,还有原理图目录列表等,

具体列出以下几个:

con_design_name : 当前设计名

con_page_num :当前页码

con_total_pages :总页码

current_design_sheet :当前页码

total_design_sheets : 总页码

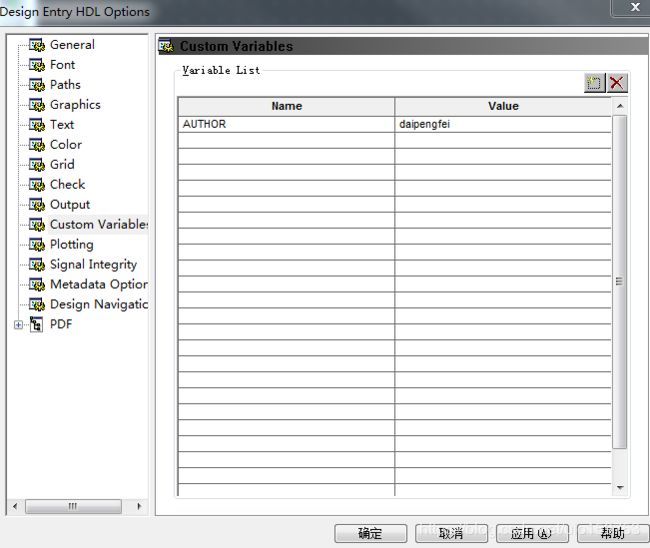

除了上述几个我用过的,其他的自定义文本可以去官方的帮助文档里头找,比较详细,除了上面的几个官方给的默认的变量外,还可以自己定义一些变量,用来显示,比如author ,这些自己定义的需要在 tool -> option-> custom Variable是,里面添加,注意这块的vaule不能为空,否则就没有用。

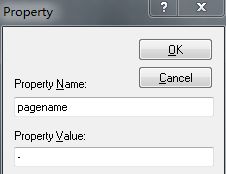

当然除了这些之外还可以显示一些属性,比如pagename,就是之前添加的那个page的属性,这里的property value是填了就是默认值

上述方法只是通过修改官方的库来操作,另外还有一种办法就是重新建一个原理图边界的库

新建一个工程,然后在part manager界面下通过点击 tool -> design entry HDL 进入原理图绘制界面通过输入如下的命令

edit

.sym.1.1

注意这个要被替换成实际的名字

然后放置原点 ORIGIN ,

选择 text -gt; attributes 然后点在origin上,添加一个属性 comment_Body,value 是ture然后ok就行,接下来就是画线就行,然后添加一些文字,costom text 然后就定义区域就可以了

具体参考官方帮助文档

2.5 放置元器件与互联

放置器件

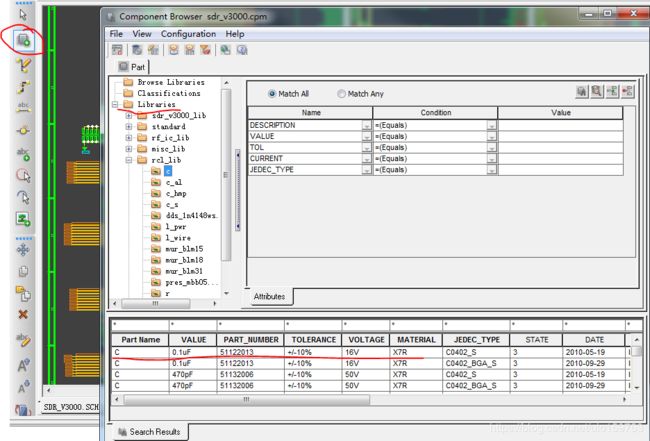

放置完成边界后,添加器件的操作为 绘制工具栏里头的这个按键添加器件,然后选择libraries,然后就是自己添加的各个库了,选择特定的器件之后需要选择part table里头的具体的器件,

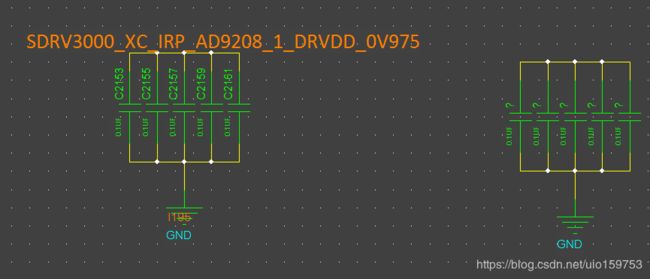

每一个器件可以有多种的参数,这些参数都是固定的不能够修改, 只能够通过建库的时候添加part table来设定,例如图中的电容,就是,不能够自己设置电容值,只能选择建立好的电容,里面有具体的参数包括容差,耐压,材料等等,如果想要添加电容值,简单的办法就是在电容的库文件夹里头找到part table,找到.ptf文件然后按照格式进行添加就行。

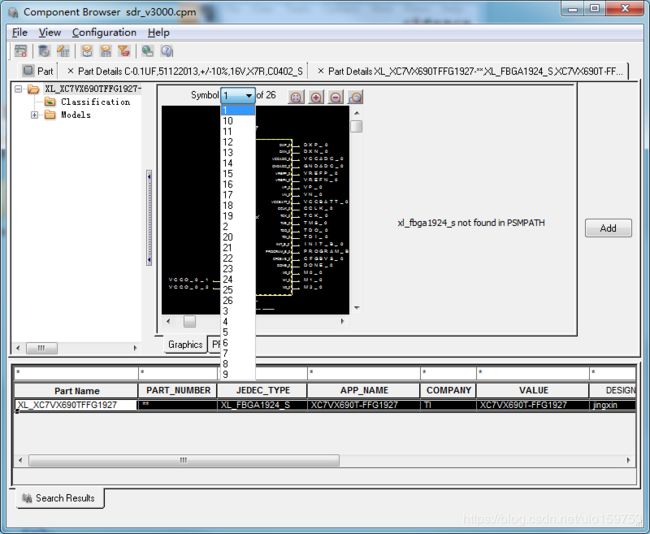

另外对于类似FPGA之类的器件被分成好几块的器件需要在这选择不同的symbol

然后点add加进去就行。

放置器件还可以通过画手势来操作,具体自己可以设置,也可以输入命令add来操作,

器件放置之后的移动是通过ctrl +鼠标左键拖动来移动,旋转有两种,一个是spin,一个rotate,目前还没有用出区别来,操作的话右键spin也行或者左键画手势,个人偏好画手势,后面附录放上手势旋转的图例。

另外,不要对器件进行双击操作,不会跟AD和CIS一样弹出属性修改界面,只会出现一个黑白的元件符号的修改界面,这个时候不要方,直接在工具栏按这个按键 ascend

返回上一层就行

下图是双击后的界面效果,原理图编辑啥的可以直接双击边界进去。

走线

器件的互联需要注意的是有两种走线命令,一个是wire,一个是route,wire是这个![]() ;route是这个

;route是这个![]()

route是自动布线,点一下起点,一下终点,自动转弯设置,wire是手动决定转弯的地儿。但是个人一般用wire来布线,这样走线可以可控。

-

走线的颜色可以通过右边的颜色工具栏来进行更换,

-

走线的粗细可以通过右键thick来变粗,也可通过thin变细,另外也可通过自行设定快捷键来操作,具体变粗的命令是: display heavy ; 变细的命令是display thin ;

-

走线可以通过按住ctrl 之后框选走线一端 左键双击之后可以挪开器件。然后就可以松开ctrl键了

-

走线放置之后想要变更长度,按住ctrl 框选走线之后,然后一直按住鼠标左键拖动

-

器件的管脚有热点,管脚与管脚之间之间互怼,按照上面的操作也可以直接拖出一条走线。

放置总线

concept HDL没有特定的总线走线方式,就是普通的走线,如果命名成总线的形式就是

一般的操作有signame[7:0] , signame<7:0>, signame[7..0] . 两个点和冒号是等效的操作,

更详细的操作是这样的,可以设置步长;

总线的整体样式是这样的

图中总线的入口样式为默认的样式,为c-tap,可以通过wire -> bus tap 添加。另外一种方式就是通过快捷获取工具栏里头的taps来获取,具体如图,![]()

总线分支入口当然还要其他的样式,不过我没有用过,

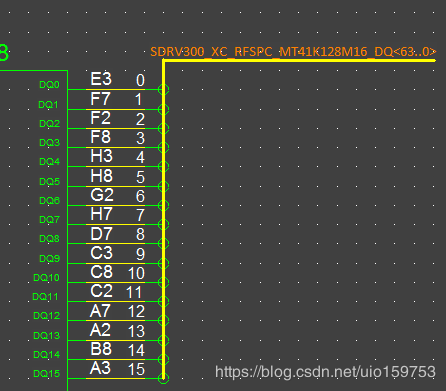

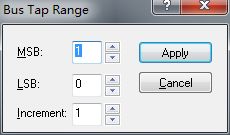

总线分支的序号的设定是通过如下的方式来进行的

选择 wire -> bus tap values

然后照着填高位低位,还有增量值就行。

走线命名

当然也可以通过 _#signame 命令来执行,或者自己定义的手势来操作,

信号名可以自己用Excel啥的编辑然后一起全粘过来,方便省事儿,具体如下所示

放置vcc,port端口等

放置VCC gnd

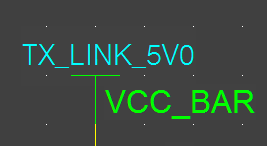

全局操作原理图需要放置VCC ,GND,input output 等,

cadence 添加 VCC和GND一样,什么形状无所谓,主要是属性中的,HDL_power, 这个名字是网络名,

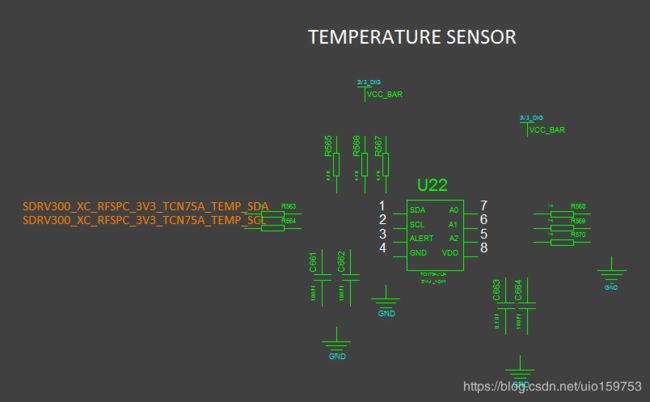

具体效果如图所示;

放置offpage

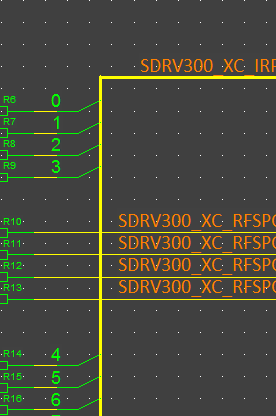

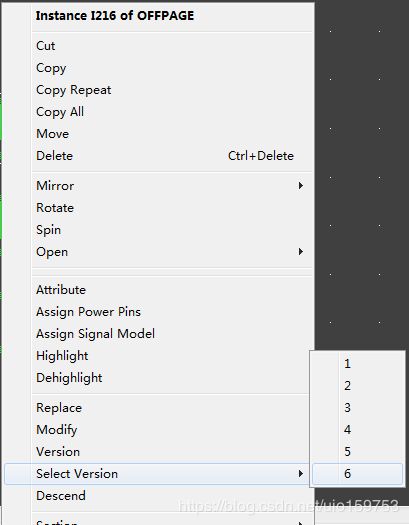

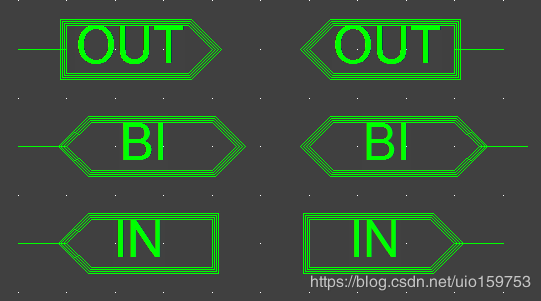

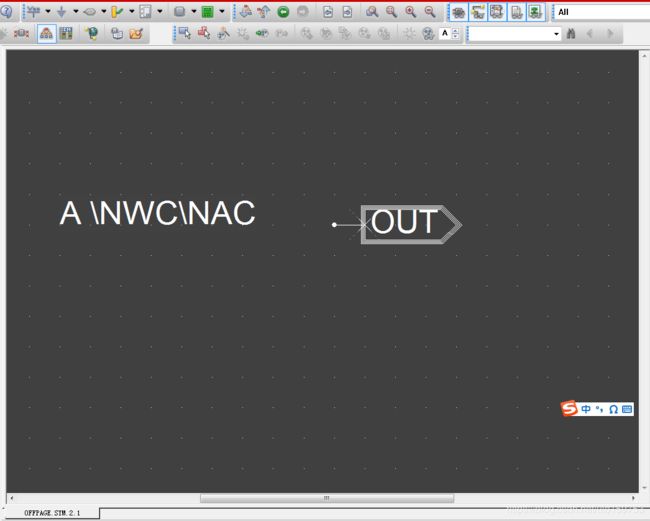

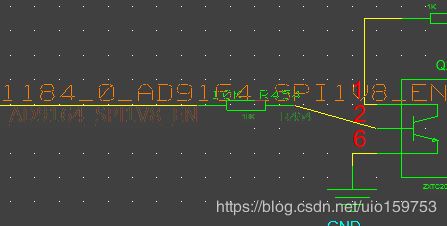

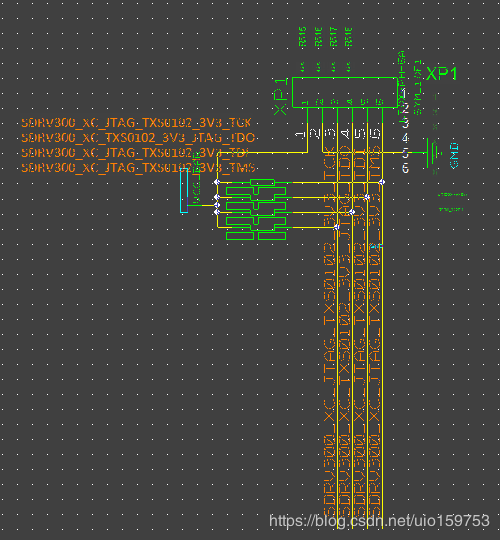

design entry HDL 支持跨页的符号为 offpage,虽然也有inport和outport,但是他们主要用于block的电路中,用在直接跨页的电路图中会有问题,报错。虽然添加offpage和不添加没啥区别,但是为了电路图的可读性建议添加,具体添加方法如下

offpage只有一个symbol,通过不同的version来区分,右键进行选择,具体选择如下图所示

还有一种办法就是直接画stroke ,画V 就可以直接更换。

放置 replicate 位宽变换符号

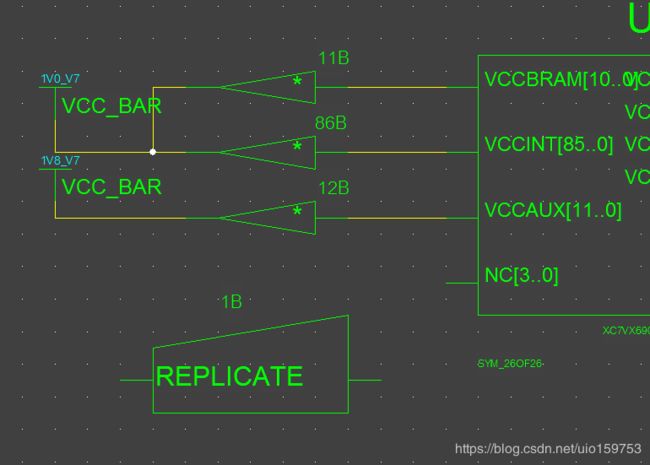

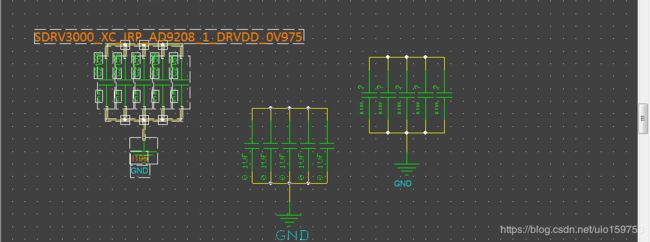

HDL 提供一种总线的管脚,可以将一类具有相同功能的管脚聚拢在一起,这样对于FPGA之类的器件非常友好,可以将一堆的GND和电源VCC只用一个总线管脚来表示,但这样会有一个问题,就是如果想要用这个总线管脚连一个器件,比如磁珠,这样就会出现位宽不匹配,报错,因此需要这样的一个位宽变换的符号,来表征这对总线管脚连接到同一处,具体的用法和效果如下图所示

replicate 符号有两种version,功能上没啥区别,看个人喜好添加就行,然后那个位宽可以直接对位宽的 1B进行change 操作,直接修改位宽,还有一个是右键attribute在里面修改size值就行。

另 : 总线接口直接连接VCC和GND的符号没有问题,不用添加该符号,直接连就行,上图的情况可以加也可以不加。

添加文字备注

文字备注主要有以下几种方式来操作,常规的就是直接工具栏里头的这个按键![]()

还有一种就是stroke 画 “N”,或者命令窗口输入 _#note 。

然后,如果想要修改字体的大小 有3种方法,一个是直接按快捷键 F8增大字体,F9减小字体,

F8的一次按键的步进是1.25倍大小,F9是0.8倍大小。另一种办法就是直接菜单栏,text ->set size 。这里主要的是直接设置字体大小。

具体可以仔细去观察两者的命令行,命令行是不同的,一个是display ; 一个是textsize ; 个人觉得如果想要批量修改某一类文本的大小的话,textsize更合适。

注意事项

- 注意画

Ccopy note 容易崩溃 ,切记切记,一崩就全没了。会在工程文件夹下留下一个多出来的文件夹,可以把这个文件夹删了,没啥用 - note备注最好不要有中文,否则导出PDF会出错乱码

- 如果变更了字体和字体大小在修改和移动的时候可能会出现光标跟显示的位置不一致的地方,

3、原理图修改与检查

绘制原理图的过程中需要反复的对原理图进行检查,和修改,有些改动比较小,有些改动相对较大,因此,这边主要介绍一些在完成了一些基础操作之后的修改和检查部分的操作,修改主要是基于对整块或者整页的原理图的修改,cadence也提供了一些错误的检查手段,可以方便大家查阅错误。这边也做一个梳理

3.1 基础移动、复制、修改、替换

移动

对于原理图器件和电路的移动均是一样的,如果是默认的设置就是ctrl +LMB 是框选,和移动的操作,如果是电路块或者器件有连接需要断开连接的,可以通过以下操作,

按住鼠标左键,框选住器件之后,然后去拖动器件的同时单击以下(就是拖动电路或者器件,然后松开鼠标左键),便得到如下的样子

可以看到连接变成了直线,并随着器件的移动而移动,这时如果再单击以下就变成了这样

然后器件都断开了连接,就可以任意拖动器件或者电路了。

上述的操作简单来说就是电路拖动的时候按住ctrl双击左键。

如果没有连接需要断开就随便了,直接ctrl +LMB,随便拖。

另外,如果将鼠标左键的默认操作给改了,改成直接就可以选择了,stroke就会变成ctrl + LMB。这个时候不能进行鼠标左键然后双击的操作,因为操作逻辑上已经不允许了,这个时候就需要用到group来进行操作。

建立group

这里简单介绍一下group的工具栏,group的意思大概就跟office里面的组的意思一样,就是对一堆的元素或者器件进行统一操作的意思,group的建立主要有以下两种方式,一个是通过工具栏进行选择, 一个是通过输入命令来操作,这边先讲一下工具栏中的操作,下一节修改属性之类的时候再说一下命令行,工具栏如下![]()

group主要有三种方式来选择,第一个是通过矩形框进行框选,第二个是通过任意多边形进行框选,第三个是通过表达式来进行选择, 表达式选择的话可输入一些类似property, note之类

选择原理图主要用上前两个,多边形选择如下图所示

上面依次是移动,复制group, 复制所有的group和删除group,

注意,这个时候想要对group只能通过工具栏来操作,不能够通过手势直接来操作移动和复制group,在通过点击工具栏之后,电路开始随着光标移动,这个时候按下ctrl 然后进行双击之后,就可以断开group电路与其他电路的互联。

复制操作

design entry HDL 有4种复制命令 分别是 copy, copy all,copy repeat, array。

分别介绍一下 copy是单次复制,复制之后的器件的位号会被抹掉,信号线的网络名不会被复制上去,具体如下图所示

copy all 也是单次复制,但是是全部复制,信号的网络名和位号都会保留。具体如下图所示

copy repeat 是重复复制,可以多次复制,每次放置完之后光标上还会有一个复制体,但这是copy操作,位号和信号名会被抹掉,具体如下图

array 是等间距的复制多个,特别适合复制一堆的电阻电容的操作,其具体的命令是copy 具体如下图所示

上图的复制就是复制10个,具体的命令为copy 10,用户也可将这个命令给定义成一个快捷键,例如copy 7,每次直接复制七个。

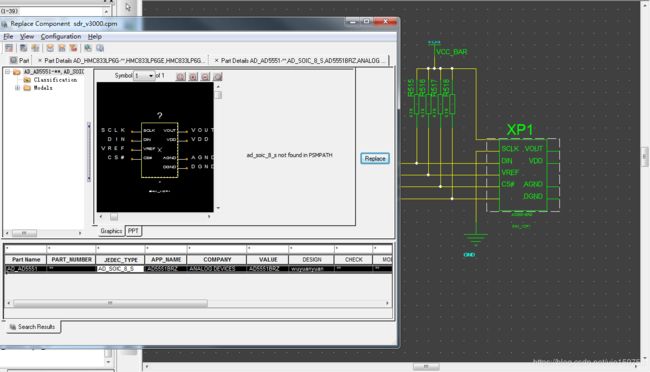

器件替换

如果想要对器件进行更换, 软件支持的有两种,一种是replace,一种是modify,这两种操作都不会变更位号,因此多用来作为打包后的原理图修改。通过鼠标右键进行操作,具体如下图所示

modify 的替换只能是同一个器件,然后更换不同的part table,具体的修改的样子如下图所示,这种操作主要可以用来电阻电容的值,但是又不想变更位号的状况下操作

replace 则是不限制,任何的器件都可以替换,同样位号也不变,例如下图所示,接插件换成了小的ADC,依然可以操作,甚至位号也是之前连接器的位号,替换也是跟添加器件的操作一样,不同的是窗口的ADD按键变成了replace。

电路图旋转,镜像

想要对某一块电路图进行旋转镜像,就需要打开pre-select mode 这个设置,具体在tool -> options -> general 里面,如下图所示

注意如果开了这个模式,就会出现一个bug,软件在下次打开的时候,鼠标左键的模式变成了直接选择了,而不是手势,要再次把左边的ctrl+LMB关掉以此,再勾上,才可以恢复,另外有个问题如果恢复了鼠标左键默认是手势操作的时候,就会出现手势的旋转和镜像的手势不能对整块电路起作用,因此这块大家使用的时候需要做取舍,

对电路的操作旋转有两种办法,一个就是在菜单栏的edit->spin 或者mirror 。还有一种就是在默认左键是选择操作的时候,通过手势进行旋转和镜像,旋转操作如下图所示,左键单击之后就可以了,图中都是操作中途的截图

文本和属性的修改

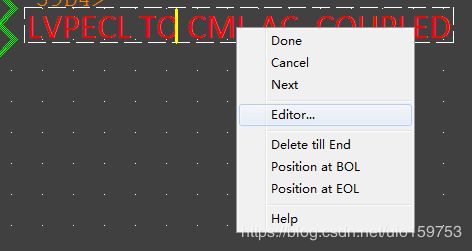

文本或者属性的修改主要有以下三种方式,,一个是直接鼠标右键change ,一个是通过手势画e进行修改,或者是在进入change状态后再鼠标右键 edit ,具体如下图所示

这个操作对于修改信号名和 vcc GND 的hdl_power 属性一样管用。

显示和隐藏操作

显示和隐藏在工具栏可以找到,英文名字叫layer 工具栏。![]()

从左到右是 显示/隐藏器件本体,显示/隐藏信号线,显示/隐藏属性,显示/隐藏note,显示/隐藏图片,具体显示效果如下图所示 可以通过这些设置来进行对于特定类型的信号线,进行修改或者对齐之类的操作。

显示管脚序号

显示管脚序号一般的操作是对于单个器件右键 multiple section,对于批量的处理,打包的时候会back annotation出来。

至于multiple section调出是在鼠标右键菜单里头,具体如图

3.2 全局修改替换

上面简单说到了几种单个替换的方式,同样,HDL依然支持批量的修改,主要有两个入口,一个是菜单栏tool -> global update ,一个是管理工具栏的 part manager

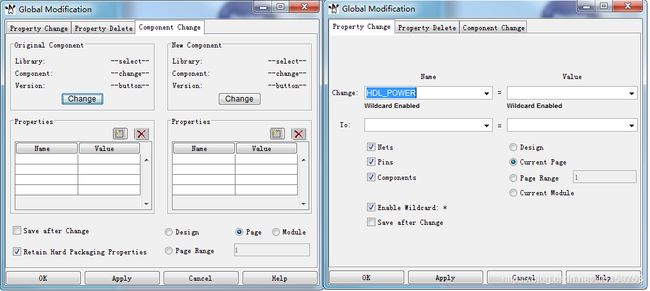

global update 修改

global update 可以通过搜索的方式对一类的器件进行整体的替换,例如电阻换成电容,或者磁珠啥的,还可以更换网络的名称等等,具体的入口如下图所示

然后打开后是这样子的

左边是器件替换的,右边是属性替换的

一般默认选择就行,没啥需要注意的,器件替换,可以选择其中一些属性不被替换,具体可以自行摸索。

part manager 修改

part manager这个很适合原理图绘制完成之后的操作,做一些阻容物料的合并,还有就是器件如果变更了,然后part status会变成 ×,可以直接通过这里进行更新。具体操作如下图所示,通过update and apply来进行更新和替换,

也是这种只能选择一个器件的不同的part table 。很适合替换阻容,

命令行修改操作

命令行也可以进行一些批处理的操作,不过我目前主要用来处理的是一些替换文本颜色,字体的操作,还有就是删掉path属性的显示。主要的法子就是用group来进行操作,

下面给出官方的示例

set nextgroup A ------- 设定所要建立的group的名字

find sig_name ------- 选定当前页面所有的信号名

include properties ------- 选定页面内部所有的属性文本

exclude notes ------- 排除选定的note文本

exclude bodies ------- 排除器件本体

textsize 0.104 A ------- 设定group A的文本尺寸大小

write

具体的操作也是如上所示,先设定group名称, 然后选择特定的内容,对group进行操作,

一下列举出我目前用过的几个操作

设定电源字符的颜色为天空蓝

set nextgroup A

find HDL_POWER

paint skyblue A

删除path属性

set nextgroup B

find path

delete B

设定管脚的num的颜色为黑白色

set nextgroup A

find $PN

paint MONO A

设定信号名的颜色为橘色

set nextgroup A

find SIG_NAME

paint ORANGE A

3.3 原理图页的删除移动

原理图在修改完成后,可能会出现一些原理图顺序的调整和删减,挪顺序的话直接在页面导航窗口直接拖动页面就行,如果是删除原理图页面这是如下图所示的操作,在file ->edit page里面的delete page操作,会直接删除当前页面。

3.4 原理图检查

原理图对于错误的报告主要有三个地方,一个是每次保存的时候如果有一些基础的互联逻辑上的错误会报错,

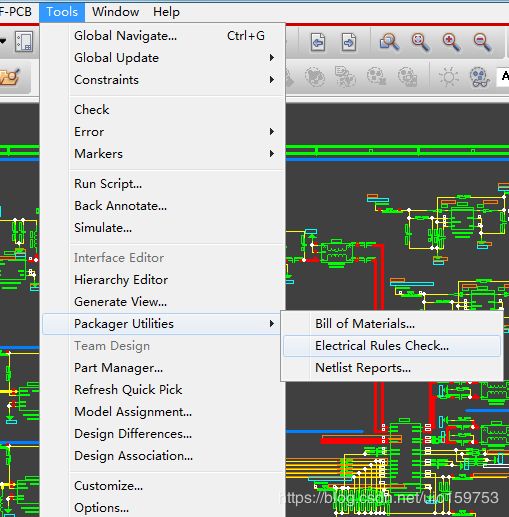

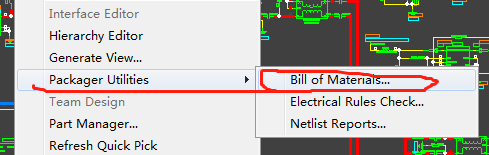

第二个地方是在tool ->;packager utilities里面的ERC检测,具体入口如下

此步可以检测一个比较重要的是单点网络,会产生一个文档,然后挨个查就行

还有一个地方是在打包的时候,打包的时候如果没有成功会显示一个报告,具体可以看提示,一般在 原理图工程文件夹下 worklib->;packaged里面

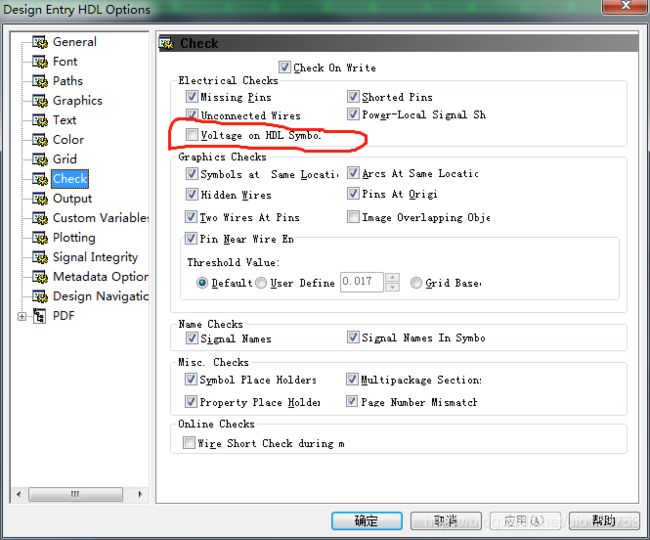

另: 如果原理图检查有类似HDL power没有电压值之类的报错,可能是因为这个设置没关掉导致的,如下图所示勾去掉就行。

4、原理图导出文件、交叉索引,打包,归档

原理在修改完成之后需要有一些相应的报告生成,比如生成bom还有跟导出到pcb.

4.1 导出bom

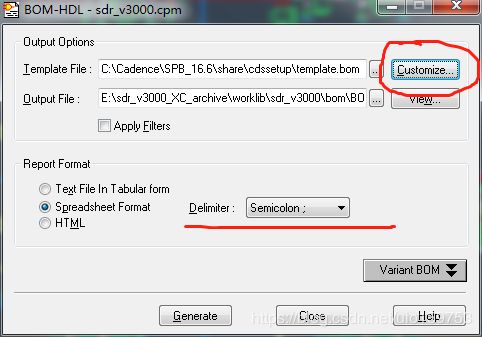

HDL生成bom只有文本格式,可以自行选择需要导出的属性。

具体入口如下, tool -> packager utilities ,

进入后如下所示,主要需要注意的地方如下所示,一个是template可以设置需要报告的内容,一个是报告格式,属性之间的分隔符号选择,照着图上的设置就行,选分号,其他的导入到excel里面不方便。

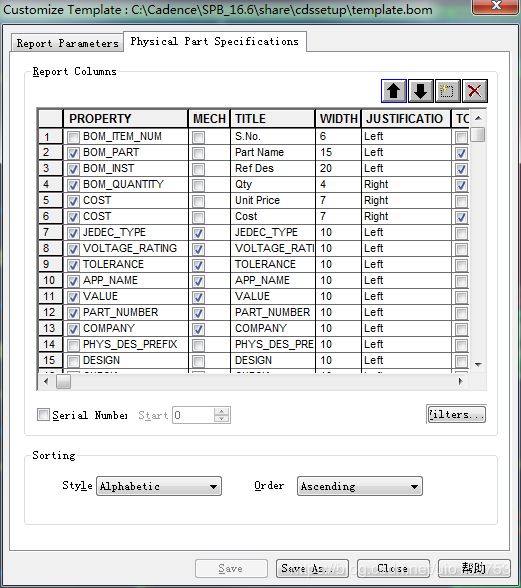

对于报告内容的选择,则是如下图所示,具体勾选想要报告的属性就行

4.2 交叉索引

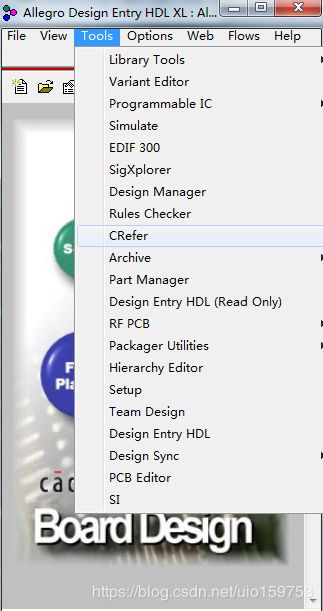

交叉索引用来原理图跨页之间的快速访问,直接按住ctrl+LMB就可以直接跳转到互联的另一个网络上,比较方便查看,而且导出到PDF也可以用。具体入口在project manager 里面的tool -> Crefer

进去之后的如下图所示,没啥具体操作,但是可以通过option进行设置,一般默认也行。

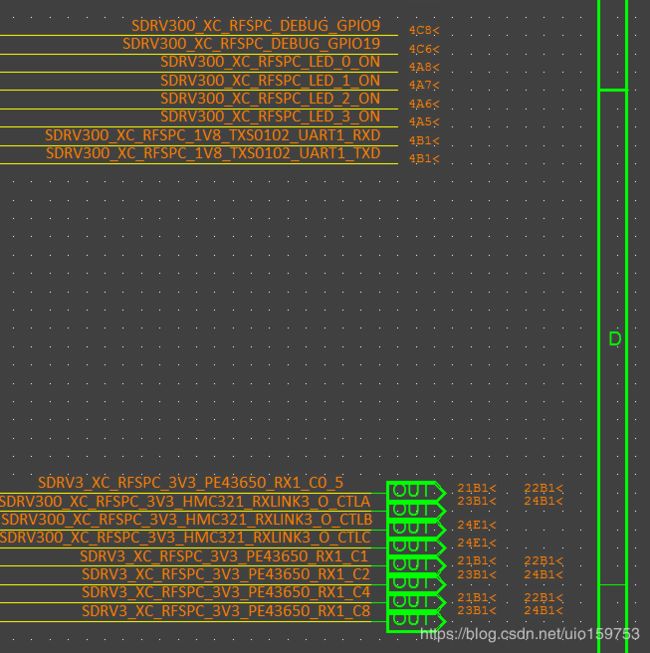

添加交叉索引之后的样子如下图所示

交叉索引默认的格式是: 页码+图片区域+>

要注意的一点是添加索引并不一定都能成功,它需要原理图中有一定的空间来放置这些索引标签,如果信预留的位置不够,或者刚好在原理图页面边界上,就不会显示,还有一点就是这些标记是放置在信号名的后面,但注意,是默认的字体和字体大小的样式的前提下的后面,否则总会看起来隔了一段距离。

4.3 工程打包

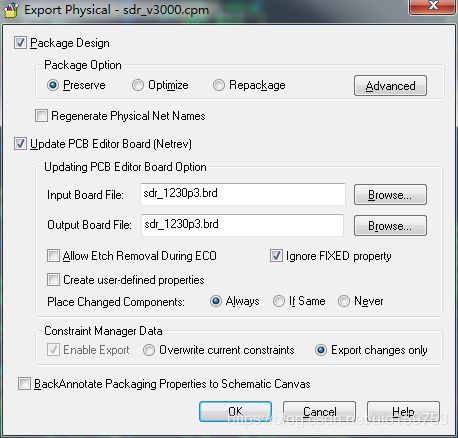

打包是用来生成和导出到PCB的操作,这一步可以生成器件的位号,pin num显示等一系列的操作,具体入口为file -> export physical ; 或者在project manager界面 design sync 也可以![]()

具体的操作如下,主要就是这三个部分,一个是打包选项,目前选择的是保留之前的打包结果,一般选这个就行,选了重新打包会重新生成一遍位号,如果已经画了PCB这样操作会很崩溃

第二个是更新和链接到PCB上,如果目前没有PCB就把这个勾去掉就行,有的话也是默认就行

第三个是反向标注,不过好像没啥用途,勾不勾新添加的器件都会生成新的位号

如果操作了这一步之后,PCB和原理图就关联了,如果在原理图中高亮某一个器件或者信号线,PCB中的信号线也会随之高亮(PCB中的高亮命令是激活状态的时候),互操作性非常好。

另:打包之后的PCB文件就在工程文件夹下头的worklib -> physical文件夹里头

4.4 工程归档

工程的归档是HDL的一个特色,归档操作可以将整个工程所需要的库全部拷到工程文件夹下(主要是一些全局的库里头的东西),使得整个工程能够以一个完整的文件夹存在,可以随便拷贝到任何有cadence的电脑里头打开,不受各种设置的限制。非常方便

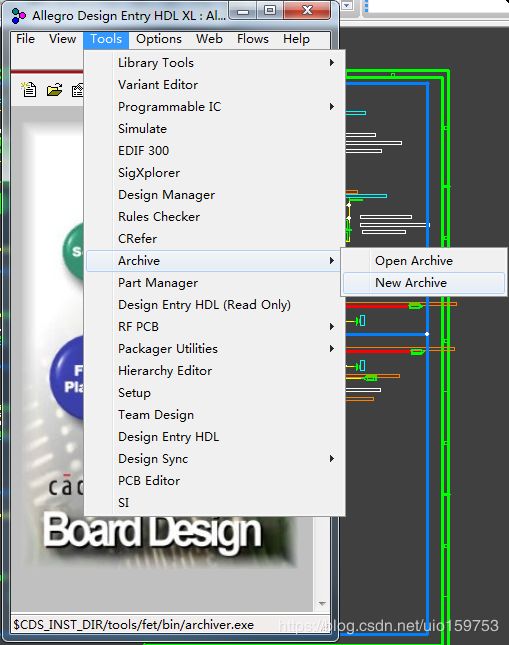

具体的入口如下图所示,是archive操作

进去之后默认操作就行,唯一可能需要改变的就是输出文件夹的目录,自己想存哪里就随便,默认也行

5、附录

手势操作说明,附录简单介绍下我个人设定的一些操作的手势,仅供参考,其中有些是官方的操作,比较实用

参考文献

[1]. Cadence Concept HDL & Allegro原理图与PCB设计 .EDA先锋工作室

[2]. allegro design entry HDL user guide