IC芯片版图实现第一步:数据导入(import)

数据导入(import)

- 工具简介

- 后端版图设计流程简介

- 数据导入步骤

- 输入数据的检查

- timing 的QoR

- 综合的check_timing的报告

- 等效性检查(EC)

- 面积信息

- UPF

- 时序约束的读入(sdc)

- 基础环境的设定

- 库(library)的准备

- 技术文件(technology file )

- 其他

- 结语&关注

工具简介

版图工具向来都是各家EDA大厂的必争之地,毕竟一个要卖3MUS$啊!艾思从开始使用的Apollo,、Astro、blastfusion、 talus 直到现的icc/icc2工具,很明显,整个业界的版图工具数量呈现一个逐渐减少的收敛状态。就像EDA公司数量一样,向高度聚合方向发展。事实证明,以前那种百花齐放的日子已经不复反了,只有真正的资本大鳄才可以在金山银水里屹立不倒。毕竟开发layout工具真心费钱啊!

后端版图设计流程简介

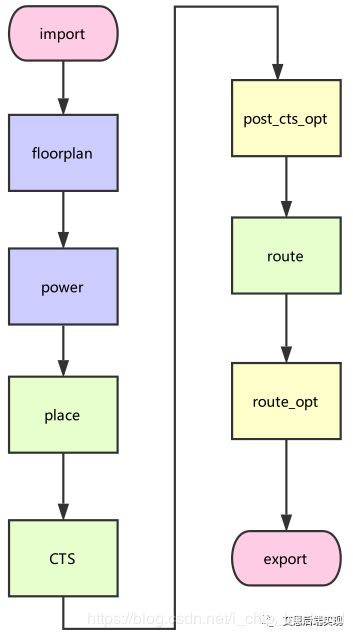

经过不断地演进,现在在IC的芯片版图市场就剩下了两家独大的局面:Synopsys 的 icc/icc2和Cadence 的Innovus,不论使用哪种工具,大致的版图实现流程都是相似的,因为知识,都是增量、递进式发展的。从流程讲,一般都无外乎以下几大步骤

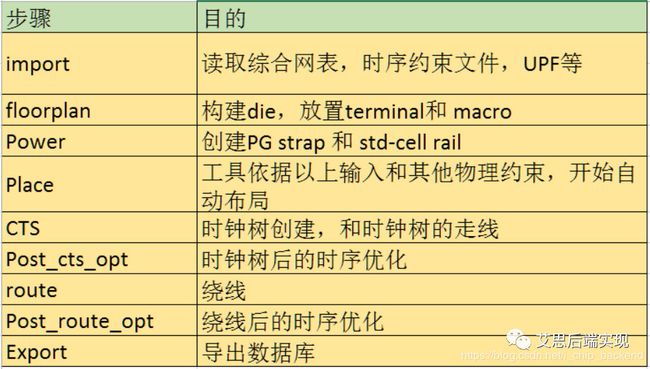

具体对应每个步骤的工作目标,见下表

后端的工作的数据量是非常庞大的,动辄就是一百多万的器件数量,和几百万的连线关系,工具这时候就会帮助用户来完成这些复杂的工作,但是,这些都是基于用户的指导和干预的。

APR的全称就是 Auto Place and Route (自动布局布线),后端工程师基于工具提供的命令接口、选项、配置来操作,这些都是工具细节,更重要的是要知道每一步骤的目地。要保证质量,就必须保证每一个分解步骤是收敛的。这点很重要,很多同学问艾思,为什么layout的timing不好,short太多,不好修,怎么解决呢?用蝴蝶效应,来比喻后端版图实现是最恰当不过了:任何一点微小的改变都可能最引起最终的结果。

作为一个后端工程师,一定要多自己的数据库有认识:你的版图的特点是什么?你的瓶颈是什么?什么样的方向调整是可以导致数据收敛?始终铭记:只有你自己,才是最了解你的模块的。

跟着艾思,一步步来,后端的工作其实也是容易的,只要每次都能保证数据朝着期望的方向发展和收敛,一定会事半功倍的!

俗话说的好,好习惯能养人。OK ,跟着艾思一起,来开启一段职业的工程师旅途吧!

数据导入步骤

今天就来讲讲第一步:数据的导入和初始化

这个步骤可能是所有步骤里边最快的,也是最容易被忽视的。从艾思的经验来看,这一步骤其实是要好好注意的,常言说得好,万事开头难啊!

输入数据的检查

做过综合的人一般都知道,综合的结果一般都不是非常真实的,但不真实并不代表虚假,首先,我们需要严格检查输入数据库的QoR,以下几个检查点是需要layout工程师仔细注意的

timing 的QoR

在所有的综合数据库里边,所有的clock都是ideal的,无论综合器是不是带floorplan信息,都要关注综合器的setup timing结果。因为setup timing 是跟频率相关的,能不能跑到某个频率,都可以在综合这边看到一些端倪。加之clock是ideal的,综合数据库里边数据通路(data-path)上的时延就决定了这个数据库的timing的结果。至于interface timing 问题,可以先在这里的检查里忽略掉,具体后面会说到。

综合的check_timing的报告

这个报告里边包含了综合器对design的timing相关的检查结果。这里需要说的是unconstrained_endpoints的结果要看好一下,这里列出来的点都是没有被时钟约束的节点,这会导致工具在整个优化过程中忽略这个点的优化,所有的这类问题都要在timing_constraint或者设计里边解决或者确认,如果遗留到后边都是很危险的。所有的timing loop也要和前端的同学确认一下,看看需不需要改code来打断loop。

等效性检查(EC)

开始layout工作的时候,一定要拿到这个结果,如果EC的runtime 比较久,可以并行做,但是一定要拿到结果来决定下一步怎么走,使用一个功能错误的网表是不可取的

面积信息

- macro/memory 的数量和面积的信息,如果是第一版layout,这个信息心里有个数就好了,floorplan的时候会真正的使用他们。如果是增量式的数据版本,一定要留意下每一版本的变化。任何变化应该都要和前端或者综合的同学确认一下,因为,这里边变化都会影响到已有的macro 发loorplan,算是版图的大变化了,必须要提前声明和确认

- std-cell的面积和类型

如果面积变化很大,设计又没怎么变,要小心看一下,可能综合的QoR在某些方面有意外。面积变化大,也意味着layout的压力变大,这里也需要好好和前端人确认。

如果buffer/invert 变化很多,最好看一下timing-path,是不是DCT输入的floorplan的不是layouter期望的

UPF

现在的设计都是支持UPF流程的,如果你有UPF作为输入量,那你一定要有对应的voltage来设定你的library,在import步骤结束时,一定要看一下你的check_mv的报告,每一个error都要看一下,这里边的问题一般都会导致place无法正确完成等问题。这点有时候很让人头疼。为了后边的QoR,所以艾思建议,这里一点更要检查一下UPF的质量

时序约束的读入(sdc)

一般来讲,layout需要读入sdc格式的时序约束文件,来作为时序优化的基础。但有时候会有很多error和warning,艾思建议大家把这个过程导出为日志文件,单独过一下,任何文件格式、版本匹配问题可能会导致数据库无法被正确使用。尽管综合的check_timing 结果是正常的,但是layout由于读入sdc出错的原因,无法复现synthesis的结果是很遗憾的

基础环境的设定

在确认了数据的质量后,我们要开始设定一些初始环境来支持

库(library)的准备

- timing library: 和综合保持一致,除非layout需要额外的corner,scenarios

- physical library: 每一个实体的cell必须要有physical library,一个cell都没有形状,你怎么用啊!

不过在icc2工具里边,已经将上边两个大神合二为一了,这下子用起来就更容易了

技术文件(technology file )

这个文件定义了你所用的工艺里边的相关物理信息:版层、VIA定义,绕线方向、unit tile等等,你的模块库创建的时候一定要用到这个文件,否则你会和别人做出来的不一样。虽然这种情况不常发生,但艾思在工作中,还真的碰到过一次,导致整个数据库无法在顶层集成使用,最后模块只好重新做layout,带来额外的很多工作。

其他

scenarios、MCMM、derating等设定应该来自于项目总体规划,一般这些都不用干预,留心不要漏掉就好了,因为某些scenarios是一定要在layout里打开的,否则你的STA一致性就会差很多。

结语&关注

到这里,import步骤就差不多了。良好的开头就是成功的一半!只要按照上边要求,做到仔细和完备,就给后面的步骤上了个保险,坐稳了,layout要起飞啦!