【ZYNQ学习之FPGA开发】一、点亮PL端LED,熟悉PL端开发流程

文章目录

- 一、PL端开发流程简介

- 1.1、创建LED工程

- 1.2、创建设计源文件

- 1.3、RTL分析,进行引脚绑定

- 1.4、synthesis - 综合

- 1.5、时序约束

- 1.6、生成比特流文件

- 1.7、下载验证PL设计

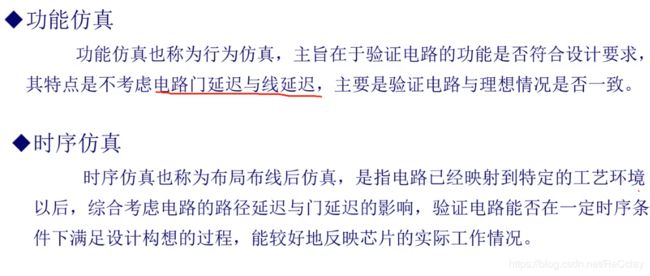

- 二、仿真

- 2.1、软件仿真

- 2.2、硬件仿真

- 2.2.1、ILA核添加

- 2.2.2、方法一

- 2.2.3、方法二

- 2.2.4、硬件仿真操作

一、PL端开发流程简介

- 设计输入:使用Verilog进行设计

- 分析:检查语法错误 ;综合:转换为门级电路网表

- 约束输入:低速设计主要指IO约束(管脚绑定);高速设计指IO约束和时钟约束

- 设计实现:布局布线

需要注意的是:上面的<分析与综合>和约束输入是可以调换的!

1.1、创建LED工程

打开位于桌面的vivado 2017.4快捷方式

出现下图所示界面,直接Next即可

选择工程名字和位置,注意勾选创建子文件夹。

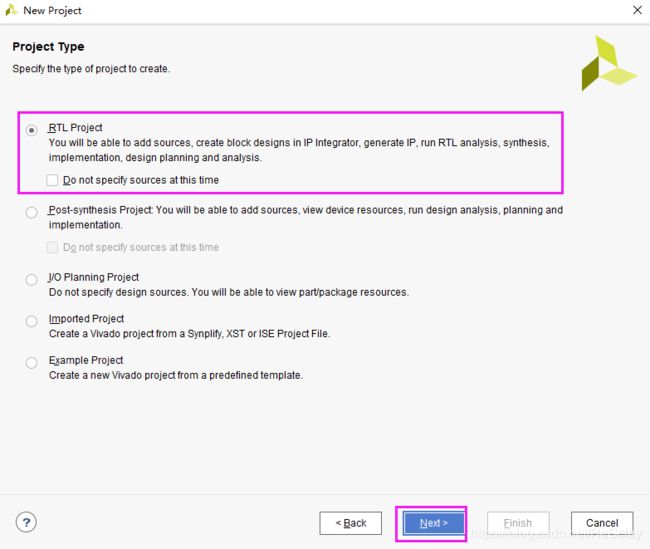

然后选择工程类型,选择RTL Project

当然这里也可以直接勾选“Do not specify sources at this time”,这样就可以省略接下来的两步!

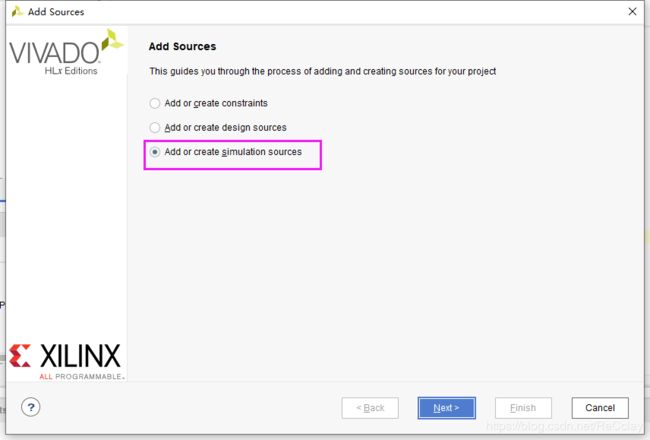

接着设置目标语言Verilog,仿真语言选择Mixed

最后选择芯片型号

设置完毕后,出现设置预览,确认无误后点击Finish即可。

1.2、创建设计源文件

源文件分为好多种,这里我们要创建的是设计源文件。

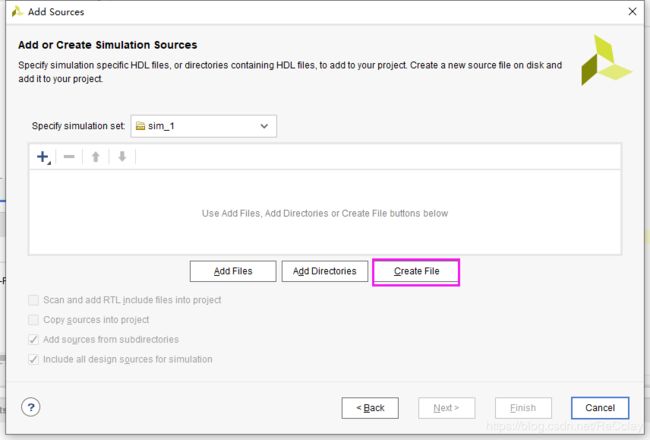

接着点击Create File

设置文件名称

接着我们便可以看到我们创建的led设计源文件啦

在led.v中,添加如下源代码,实现LED灯的一秒反转。

FPGA基础可参考下节,<传送门>

module led(

input sys_clk,

input rst_n,

output reg [3:0] led

);

reg[31:0] timer_cnt;

always@(posedge sys_clk or negedge rst_n)

begin

if (!rst_n)

begin

led <= 4'd0 ;

timer_cnt <= 32'd0 ;

end

else if(timer_cnt >= 32'd49_999_999)

begin

led <= ~led;

timer_cnt <= 32'd0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;

end

end

endmodule

这里稍微解释以下49_999_999含义,我们PL端的时钟频率是50M即20ns,我们想要定时1s的话,需要计50_000_000个数,但是计数又是从0开始的,所以要减一了。

一点小提示:

1、在编辑led.v源文件时,右上角有语法错误指示,如果语法没有错误,会持续绿灯,如果有语法错误则会显示红灯。

2、默认编辑器里面的字体较小,如果想要更改,方法如下:

这里我字体大小改成15(20有点太大了)

1.3、RTL分析,进行引脚绑定

点击左侧RTL ANALYSIS下的Open Elaborated Design

接着选择OK

点开Open Elaborated Design,可看到下面的Schematic(将Verilog翻译成了原理图)

接着vivado的下方打印的地方会有I/O ports窗口出现,如下图

当然,如果没有自动出现的话也不要紧,可以使用如下方法让其出现

方法一:在windows菜单栏下拉列表中选择

方法二:直接在工具栏搜索框搜索

方法三:选择vivado右上角的I/O Planning

方法四:在Layout下拉菜单中选择I/O planning

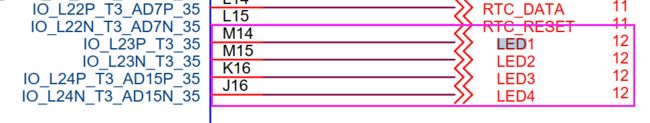

接着,我们进行引脚绑定,绑定时可查看原理图进行引脚确定。

以PL端4个LED为例,可通过原理图知道分别对应:M14/M15/K16/J16

将其填充到,I/O Ports对应的Package Pin一栏(复位和时钟的引脚确定方法同上),填充好之后如下图所示

除了进行引脚绑定之外,还需要设置引脚电平(根据原理图设置),通过查阅可知4个LED以及复位和时钟均是3.3V,故设置为LVCMOS33即可【其实PL部分的电平均是3.3V的】,如下图所示。

至此,RTL分析便进行完毕。但是别忘了文件还没有保存呢,保存文件也有两种方法:

方法二:直接ctrl+s即可

点击保存按钮或者ctrl+s操作后跳出如下所示窗口,这里我们需要设置保存的约束文件名。

注意:

上面进行了RTL分析和约束,按照流程我们接下来应该综合,然后实现,最后生成比特流文件。

但是,我们也可以直接点击生成比特流,他会自动进行综合和实现,最后再生成比特流。

当然,这个知识点知道就行了,还是要跟着教程继续往下走咯,先通一遍流程!

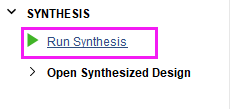

1.4、synthesis - 综合

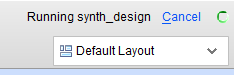

点击vivado左侧SYNTHESIS下面的Run Synthesis

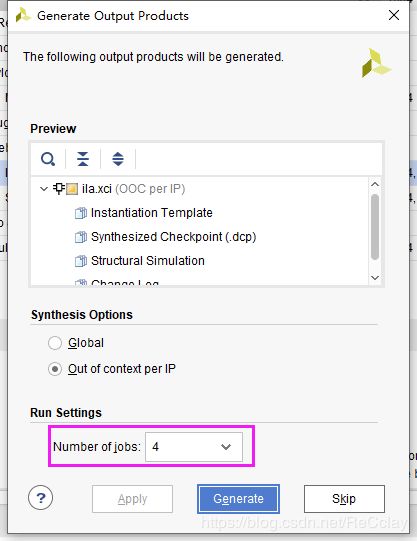

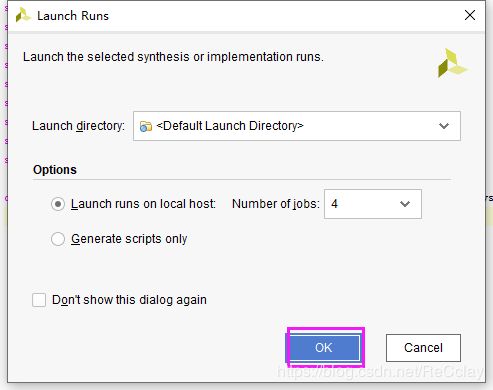

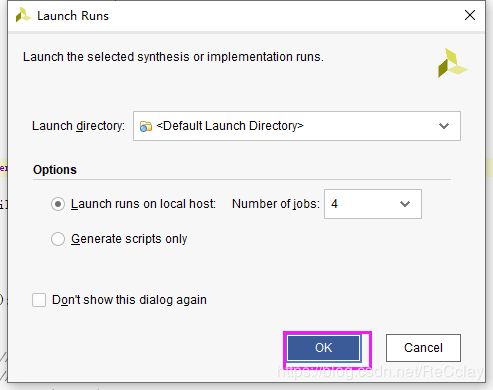

设置综合处理器个数,这里选择4。(选的越多,在综合时电脑会越卡,当然综合的速度也会越快!)

接着在vivado的右上角可以看到正在运行综合设计。

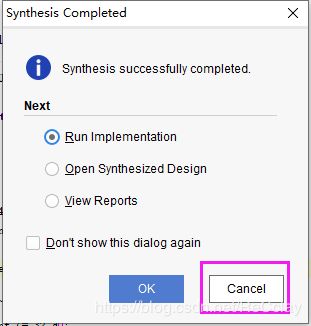

综合完成后,会自动弹出如下窗口。

第一个表示运行布局布线,第二个表示打开综合后的设计,第三个表示查看report。

这里选择cancel,因为我们下一步要进行一个时序约束,FPGA很重要的一个环节!

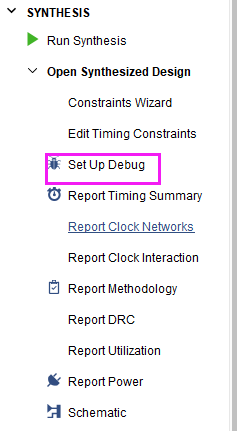

1.5、时序约束

点开vivado左侧SYNTHESIS下的Open Synthesis Design,然后点击其中的Constraints Wizard。

![]()

弹出如下窗口,直接Next即可。

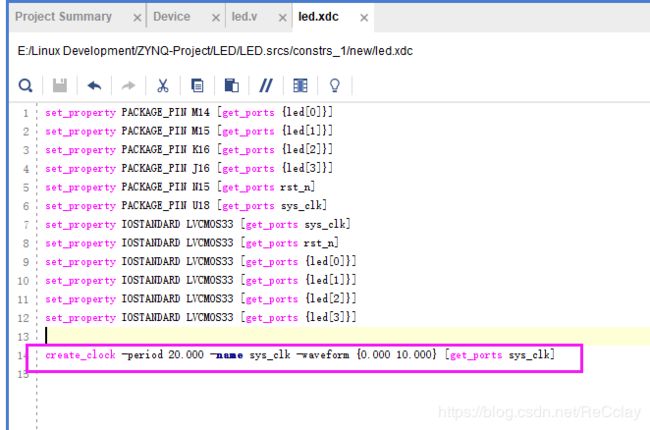

接着进入下图所示界面,在这里我们只进行一个时钟约束,在频率一栏填入50(表示50MHz)即可。然后直接点击“Skip to Finish”

接着弹出summary界面,点击Finish即可

时序约束完毕后,可以打开led.xdc文件中,并点击重新Reload

1.6、生成比特流文件

点击vivado左侧PROGRAM AND DEBUG下面的Generate Bitstream,生成比特流文件(最后下载到板子的文件)。

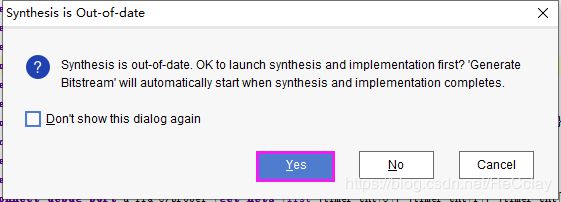

弹出如下窗口,直接选择Yes即可!

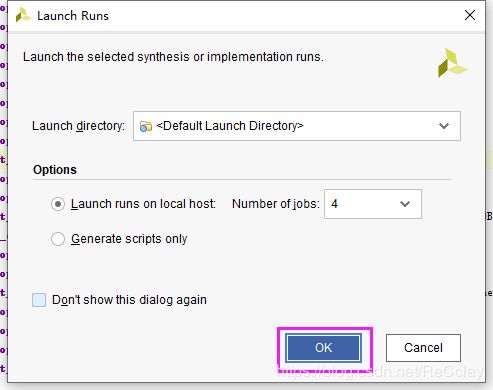

同样设置内核数,还是选择4即可。

可以看到vivado右上角正在运行。

运行完毕后,弹出如下所示界面。

第一个是打开布局布线设计,第二个是打开报告,第三个是打开硬件管理器(下载程序用),第四个是生成内存配置文件。

这里我们可以先点击cancel!

接下来我们可以下载比特流文件到FPGA开发板看一下运行效果了,具体操作见下节。

1.7、下载验证PL设计

先连接好开发板的电源和JTAG口,然后点击vivado左侧PROGRAM AND DEBUG下的Open Hardware Manage

![]()

然后在vivado上面可以看到有个Open target的提示信息,点击它然后再点击弹出的 Auto Connect,进行连接!

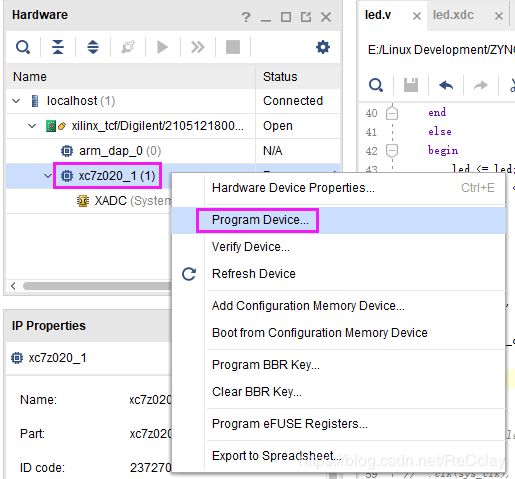

连接成功后,会有如下图所示界面,分别对应PS端的ARM、PL端的FPGA、XADC

右键xc7z020_1然后选择Program Device

下载比特流文件(默认会填充),然后选择Porgram进行下载

下载完成后,可观察到板子PL端的4个LED灯在1s为间隔同时闪烁!

二、仿真

2.1、软件仿真

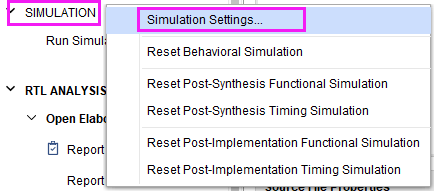

在vivado左侧,右键SIMULATION,然后选择Simulation Settings

主要设置xsim.simulation.runtime为50ms

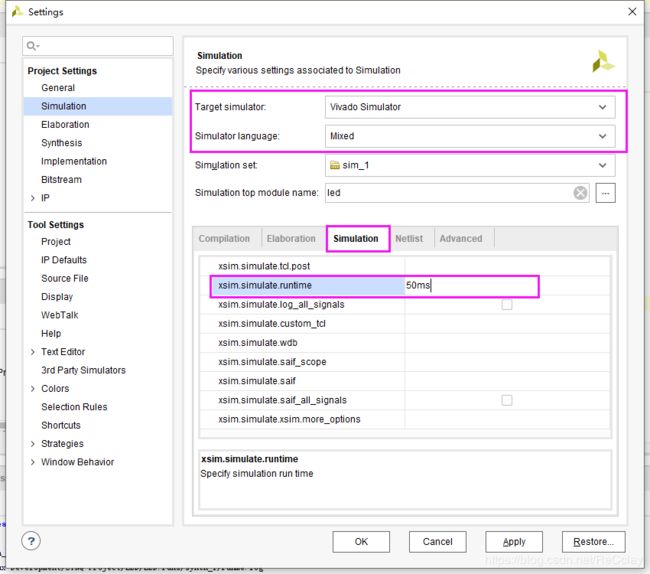

接着添加仿真源文件(同添加设计源文件方法一样)

取名为:vtf_led_test

需要说明的是,一般仿真文件的命名为:tb_xxx,这里仅仅是做实验而已,没有按照规范起名。

在vtf_led_test.v中添加如下代码,主要作用是产生时钟信号和复位信号,因为在实际硬件调试时有板载的时钟信号和复位信号,而仿真没有所以需要我们自己创建一个,改文件又称为激励文件!

module vtf_led_test;

// Inputs

reg sys_clk;

reg rst_n ;

// Outputs

wire [3:0] led;

// Instantiate the Unit Under Test (UUT)

led uut (

.sys_clk(sys_clk),

.rst_n(rst_n),

.led(led)

);

initial

begin

// Initialize Inputs

sys_clk = 0;

rst_n = 0 ;

#1000 ;

rst_n = 1;

end

//Create clock

always #10 sys_clk = ~ sys_clk;

endmodule

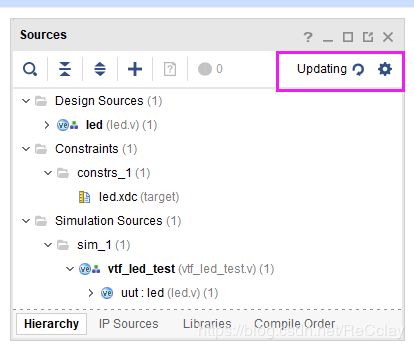

保存后,可以看到层级关系发生了变化。

鼠标左键点击vivado左侧的Run Simulation 然后选择第一个:行为级仿真。

在现有仿真界面中没有计数器变量,我们将计数器变量拖曳到仿真界面中,如下图

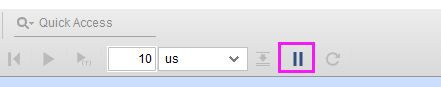

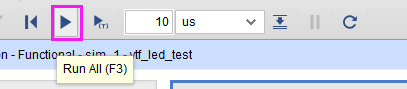

再点击run all

仿真时,以9ms为步长步进,而我们的LED灯翻转时1s翻转,所以要经过较为漫长的等待

注意:

仿真时间越长,led.sim文件夹里面占用的空间也会越来越大!

可以在vivado关闭后,将led.sim里面较大的那个文件删除

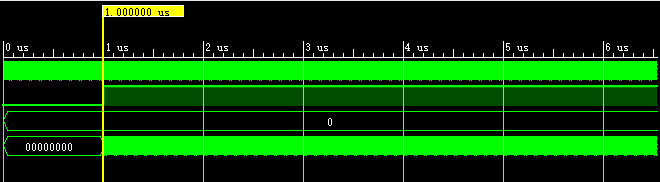

1s到了以后,左键单击定位到1s的位置

![]()

然后ctrl+滚轮放大,在1s位置可以看到LED值从0变成了F(取反)

可以看到翻转也不是严格的1s钟的位置,因为前面还有复位的时间。

计数器的值默认显示的是16进制的,可以右键timer_cnt变量,然后选择Radix,然后将其改为无符号十进制

进而可以观察到该变量在1s位置从49999999变为了0

上面仿真结束后,可以保存相应的波形,当然也可以不保存,这里直接不保存了。

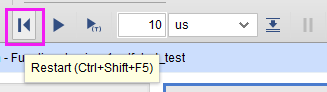

当我们修改了源文件,想要再仿真的时候,可以重新操作上面的步骤,进行Run Simulation,但是也可以直接点击下图所示按钮。

2.2、硬件仿真

内嵌逻辑分析仪是FPGA硬件仿真的重要工具,帮助我们观察内部信号的变化,方便调试。下面介绍两种内嵌逻辑分析仪的方法:

方法一、设计ILA核,修改设计源文件,例化ILA核,进行信号与探针的连接。然后重新生成比特流文件,最后下载到开发板。

方法二、设计ILA核,修改列表和原理图,本质也是修改设计源文件,在要仿真的变量前加入(* MARK_DEBUG="true" *)。然后重新进行综合,再生成比特流文件,最后下载到开发板。

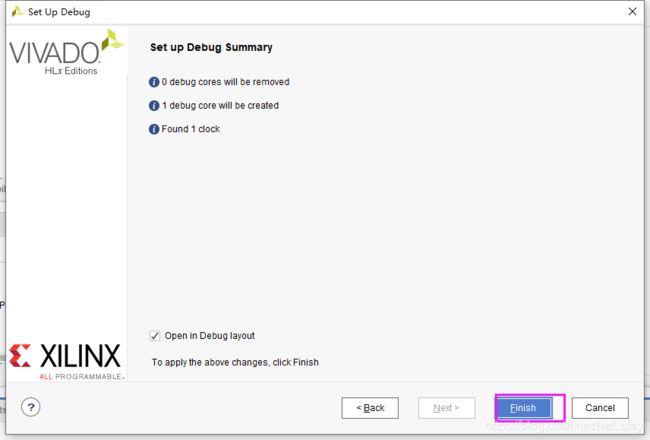

方法一和方法二有一个共同点那就是设计ILA核,接下来看看如何添加ILA核。

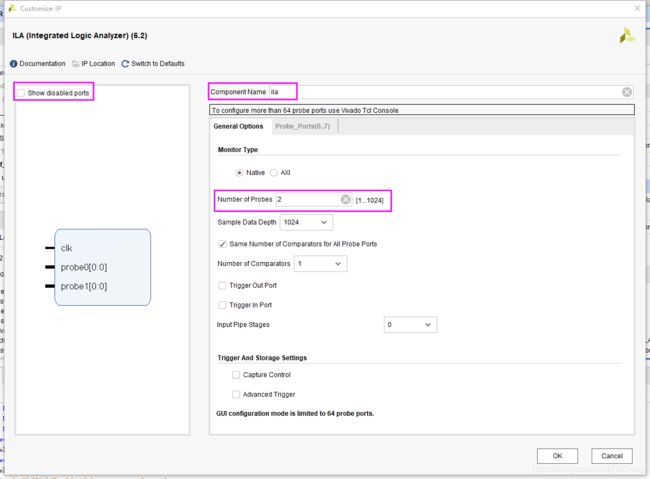

2.2.1、ILA核添加

点击vivado左侧PROJECT MANAGER下的 IP Catalog

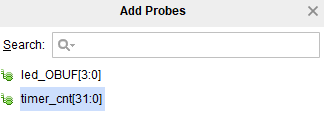

设置探针(探针可以连接我们的信号,1个探针连接1个信号)

然后设置探针宽度,这个要根据探针连接的信号确定。

本次要探测的信号有timer_cnt和led,计数器是32位宽,那么对应连接它的探针也应该是32位宽。LED是4位,那么LED对应的探针应该为4位宽。

打开之后可以看到如下层级关系(注意,ila和led是同一层级的,画的框容易让人误解led在ila下!)

2.2.2、方法一

【注意,该种方法需要设计ILA核,然后在设计源文件中例化ILA核】

下一步就是要进行例化,复制ila.v中的定义到led.v中,然后修改如下。

ila ila_inst(

.clk(sys_clk),

.probe0(timer_cnt),

.probe1(led)

);

需要说明的是,一般例化的时候命名为:u_xxx,这里仅仅是做实验而已,没有按照规范起名。

注意clk和probe前面要加点!!!

而后保存一下,会在Sources中看到Updating,表示正在更新。

更新完成后,层级关系发生了变化,把ila.v包含到了led.v中

再次生成比特流文件

完成后,注意这次点击Open HardWare Manager,进行下载程序!

注意这里较之前多了一个ltx文件,里面描述了逻辑分析仪与哪些信号进行了链接。

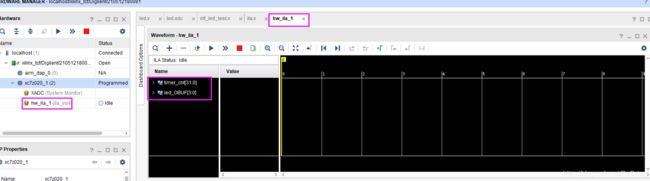

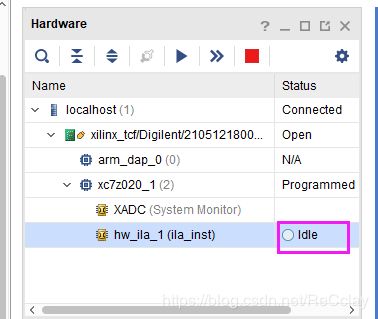

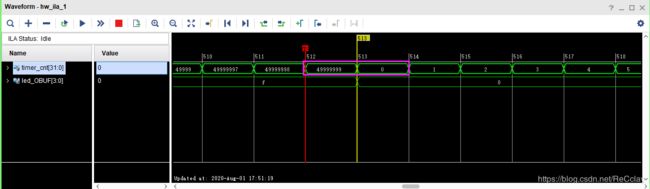

点击Program后,看到生成了hw_ila_1文件,然后也有对应的信号

2.2.3、方法二

【注意,该种方法需要在要查看的变量前添加(* MARK_DEBUG="true" *),然后重新综合(更新网表),会自动在led.xdc文件中添加内容】

点击vivado左侧PROJECT MANAGER下的 Language Templates

![]()

(* MARK_DEBUG="true" *)

然后保存,可以看到,改完之后的层级关系也变了

完成之后,保存一下设计或者ctrl+s【一定要注意,这一步也很重要!!!】

![]()

![]()

再去约束文件中,点击reload,然后保存。

下一步还是生成比特流文件

下载调试方法和前面的ila方法一的一样,这里也就直接复制了。

完成后,注意这次点击Open HardWare Manager,进行下载程序!

注意这里较之前多了一个ltx文件,里面描述了逻辑分析仪与哪些信号进行了链接。

点击Program后,看到生成了hw_ila_1文件,然后也有对应的信号

2.2.4、硬件仿真操作

仿真的话看到的不是实际的情况,而通过逻辑分析仪这种方式看到的是实际的运行

在这一栏我们可以设置一些触发条件

选择timer_cnt

触发条件设置为等于49999999时

然后再点击触发

可明显看到这次是从f到0的转变

放大来看

其中这个红色的T表示在此处进行了触发

另一个触发的设置,默认设置的是512,即T在0-1023的中间位置。如果我们想更多看后面数据,可以将其设置小一点,比如100.

设置好之后再次触发

触发旁边还有一个按钮,表示循环触发,选中它,再点击触发,循环进行触发。【关掉的话再点击一下该按钮即可】

可以从这边看逻辑分析仪(ila)的运行状态

最后硬件调试完毕后,可以在led.xdc文件中生成的硬件调试约束给删除就OK!

当然了,再次下载的时候注意清空Debug probes file文件!