TQ210——S5PV210中断体系

TQ210——S5PV210中断体系

中断是指 CPU 在执行程序的过程中,遇到异常情况需要处理, CPU停 止当前程序的运行,保存当前程序运行处的必要参数,转去处理这些异常情况, 处理结束后再返回当前程序的间断处,继续执行原程序。

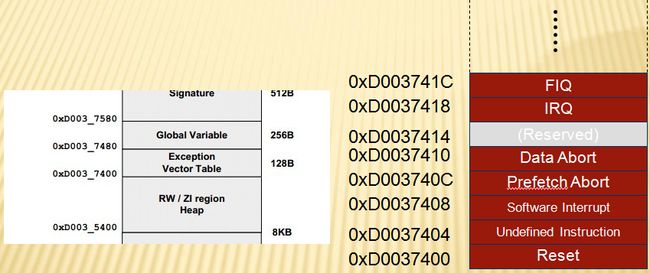

1、异常向量表

2、一级异常处理

#define pExceptionIRQ ( *((volatile unsigned long *)(0xD0037418)) )

pExceptionIRQ = (unsigned long)IRQ_handle;

IRQ_handle:

sub lr, lr, #4 // 保存现场

stmfdsp!, {r0-r12, lr}

bl irq_handler // 跳转到中断处理函数

ldmfd sp!, {r0-r12,pc}^ // 恢复现场3、VICX

S5PV210共有4个VIC(Vectored Interrupt Controller,向量中断控制器),以菊花链的方式互连共同支持了多达93个中断源。

这些中断源分别为系统DMA、定时器、外设、多媒体、音频、安全等模块提供中断服务

中断种类有IRQ和FIQ可选配,在中断处理级别上都属于二级。

菊链方式的4个TZIC和4个VIC是为了能支持93个中断源。在可信域设计里,TZIC为安全中断系统提供一个软中断。它提供nFIQ中断的安全控制和在没安全边际的系统(vic)上,中断控制器掩盖中断源。用后者来生成nIRQ信号。

菊链:一种沿总线传输信号的方法,其中设备串联,而信号则从一台设备传向下一台设备。菊花链连接方法可根据设备在总线上的电气地位分配其优先级

4、寄存器

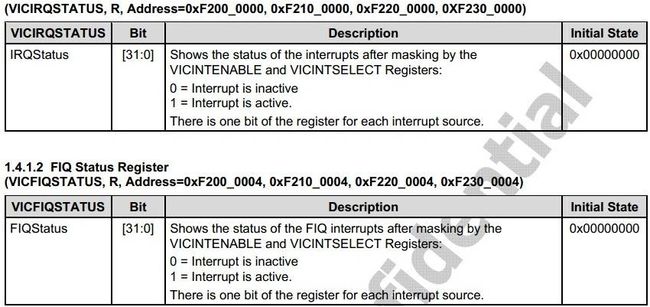

(1)IRQSTATUS 中断状态

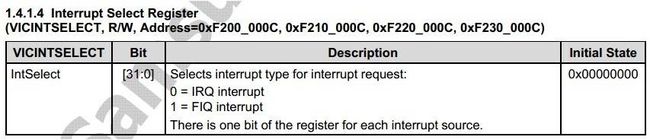

(2)VICINTSELECT(中断类型选择:irq或者fiq)

如何保证FIQ具有最佳的中断响应速度?

<1>、FIQmode具有更多的banked register,因此进入FIQ的ISR后可以避免因保存寄存器而浪费的时间。

<2>、FIQ在异常向量表中处于末端,因此ISR可以不用跳转到别处而直接在向量表末端开始ISR。

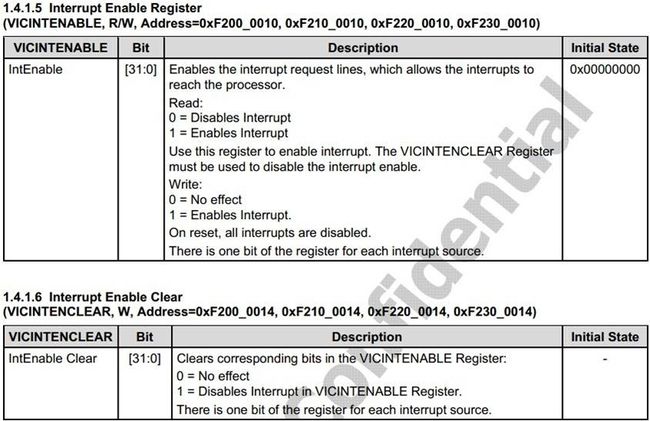

(3)VICINTENABLE/VICINTENCLEAR(中断使能/失能设置)

中断允许寄存器中,每个bit代表一个中断源。向VICINTENABLE寄存器中相应bit写1可以使能该中断(写0无效,读取时若该中断允许则返回1,若未允许则返回0),而向VICINTENCLEAR寄存器相应bit写1可以禁止该中断(写0无效)。

在另一些CPU中,只有一个INTENABLE寄存器。写1可以使能中断,写0则会禁止中断。

(4)ISR相关

ISR如何设置:

S5PV210的中断体系采用如下的ISR确定策略

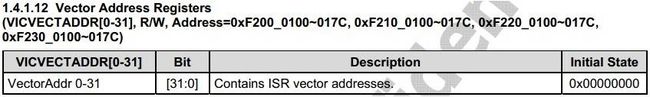

<1>、将93个中断源分为4组,每组的ISR组成一个数组,以中断号为数组索引。

<2>、4组ISR数组的首地址分别存放在VICVECTADDR0~VICVECTADDR3中。

绑定ISR时,只需将用户自己编写的ISR地址放入ISR数组中以中断号为索引的位置即可

ISR如何获得:

当中断发生,并且在一级异常向量表中跳转入IRQ后,首先要保护现场,然后转入相应的ISR执行。

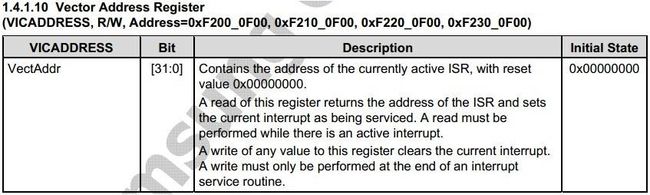

获取相应的ISR时只需读取VICADDRESS寄存器即可。因为S5PV210的中断系统会自动将当前发生的中断对应的ISR从ICVECTADDRx中推入VICADDRESSx中。这省去了我们使用查询方式确认中断号的麻烦,提高了IRQ的响应速度。

5、中断处理

中断处理过程

<1>、硬件事件发生,SRCPENDING位响应挂起

<2>、根据中断允许设置决定是否产生中断挂起INTPENDING,并根据INTSELECT决定中断种类为IRQ还是FIQ

<3>、响应中断,CPU根据一级异常向量表自动跳转到IRQ或FIQ异常入口

<4>、对于IRQ,在二级中断表中,根据INTNUM进行判断,跳转入相应的ISR执行

<5>、中断返回,本次中断事件结束

如何使用中断:

<1>、全局性设置。包括设置一级异常向量表、清理所有中断挂起、禁止所有中断源等。

<2>、针对要使用的中断进行具体设置。包括设置中断种类为IRQ/FIQ,中断允许、优先级等。

<3>、绑定中断处理程序。以便在二级中断处理时能够跳转到正确的ISR。

<4>、设置中断允许位以允许中断发生。

不同平台中断处理差异:有些平台是置1允许中断,而另一些平台是清0允许中断;二级中断时获取中断号(意味着获取中断ISR)的方式不同。这些不同会影响平台的中断响应速度。

6、外部中断

外部中断意为来自(SoC)外部的中断,是相对于内部中断(来自SoC内部,即各种内部外设产生的中断,譬如定时器中断)来说的。

S5PV210共支持32个通道的外部中断,每个外部中断有对应的GPIO接收来自外部的中断信号。中断触发方式有电平(高、低)、边沿(上升沿、下降沿、Both)等5种方式可选配。

(1)EXT_INT_0_CON外部中断控制寄存器

EXT_INT_x_CON(x= 0~3)用来配置32个外部中断通道的触发模式。

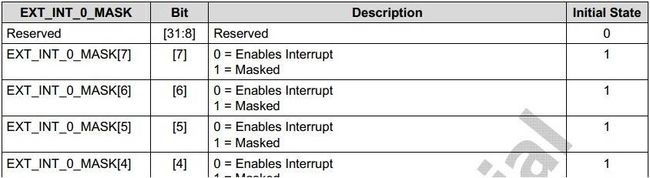

(2)EXT_INT_0_MASK外部中断允许/禁止

EXT_INT_x_MASK(x=0~3)用来使能/禁止相应的外部中断通道

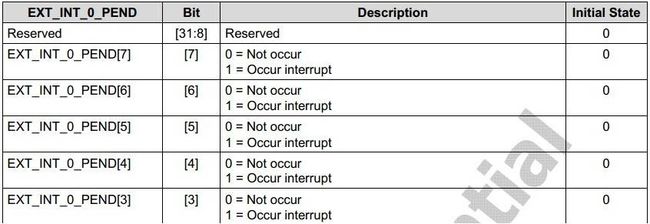

(3)EXT_INT_0_PEND外部中断挂起寄存器

EXT_INT_xPEND(x=0~3)用来标识外部中断挂起。向相应bit写1可以清除中断挂起

6、外部中断设置流程

<1>、全局的中断初始化

<2>、设置相应的GPIO为XEINTx

<3>、绑定中断处理程序

<4>、设置EXT_INT_x_CON以配置触发方式

<5>、写EXT_INT_x_PEND清中断

<6>、设置EXT_INT_x_MASK以使能相应通道

<7>、最后使能相应外部中断通道

分析:

1、中断挂起产生,CPU自动跳转到一级异常向量表中IRQ入口地址中。

2、由IRQSTATUS和VICADDRESS机制得到相应ISR地址并进入执行。

3、ISR内部内容应该包含三部分:

(1)、有效isr,处理按键对应的任务

(2)、向VICxADDR写入任意值清中断

(3)、向EXT_INT_x_PEND写1清除相应中断