嵌入式软硬件协同设计概念篇

JTAG

JTAG 是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路 TAP ( Test Access Port ,测试访问口),通过专用的 JTAG 测试工具对内部节点进行测试。CPU可通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC。

标准的 JTAG 接口是 4 线: TMS 、 TCK 、 TDI 、 TDO ,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。如今 JTAG 接口的连接有两种标准,即 14 针接口和 20 针接口,其定义分别如下所示。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程后再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对DSP芯片内部的所有部件进行编程。

通用异步收发传输器(Universal Asynchronous Receiver/Transmitter)UART

计算机内部采用并行数据,不能直接把数据发到Modem,必须经过UART整理才能进行异步传输,其过程为:CPU先把准备写入串行设备的数据放到UART的寄存器(临时内存块)中,再通过FIFO(First Input First Output,先入先出队列)传送到串行设备,若是没有FIFO,信息将变得杂乱无章,不可能传送到Modem。

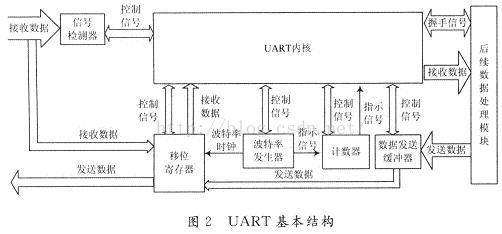

UART芯片基本结构

⑴输出缓冲寄存器,它接收CPU从数据总线上送来的并行数据,并加以保存。

⑵ 输出移位寄存器,它接收从输出缓冲器送来的并行数据,以发送时钟的速率把数据逐位移出,即将并行数据转换为串行数据输出。

⑶ 输入移位寄存器,它以接收时钟的速率把出现在串行数据输入线上的数据逐位移入,当数据装满后,并行送往输入缓冲寄存器,即将串行数据转换成并行数据。

⑷ 输入缓冲寄存器,它从输入移位寄存器中接收并行数据,然后由CPU取走。

⑸控制寄存器,它接收CPU送来的控制字,由控制字的内容,决定通信时的传输方式以及数据格式等。例如采用异步方式还是同步方式,数据字符的位数,有无奇偶校验,是奇校验还是偶校验,停止位的位数等参数。

⑹状态寄存器。状态寄存器中存放着接口的各种状态信息,例如输出缓冲区是否空,输入字符是否准备好等。在通信过程中,当符合某种状态时,接口中的状态检测逻辑将状态寄存器的相应位置“1”,以便让CPU查询。

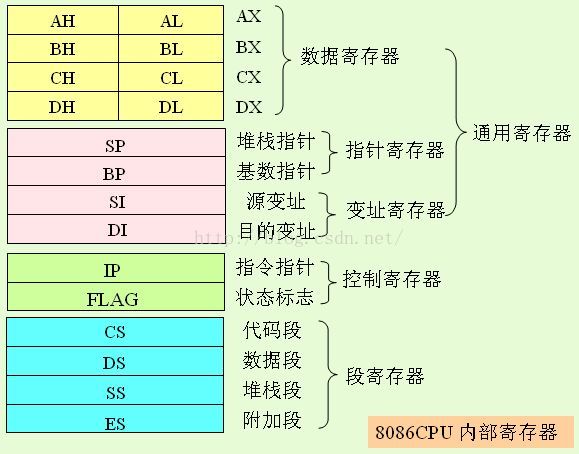

寄存器

寄存器(Register),是中央处理器内的其中组成部分。寄存器通常由触发器组成,它们可用来暂存指令、数据和地址。在中央处理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器。在中央处理器的算术及逻辑部件中,包含的寄存器有累加器。

寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。(这才是重点,有没有!!!)

寄存器通常都是以他们可以保存的比特数量来估量,举例来说,一个8位寄存器或32位寄存器。寄存器现在都以寄存器数组的方式来实现,但是他们也可能使用单独的触发器、高速的核心内存、薄膜内存以及在数种机器上的其他方式来实现出来。

锁存器

锁存器(英语:latch),是数字电路中异步时序逻辑电路系统中用来储存资讯的一种电子电路。一个锁存器可以储存一比特的资讯,通常会有多个一起出现,有些会有特别的名称,像是 “4位锁存器”(可以储存四个比特)或“8位锁存器”(可以储存八个比特)等等。

锁存,就是把信号暂存以维持某种电平状态,在数字电路中则可以记录二进制数字信号“0”和“1”。

所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化(说到了点子上,有没有啊!!!),仅在有锁存信号时输入的状态才被保存到输出,直到下一个锁存信号到来时才改变。

在某些应用中,单片机的I/O 口上需要外接锁存器。例如,当单片机连接片外存储器时,要接上锁存器,这是为了实现地址的复用。假设,MCU端口其中的 8 路的 I/O 管脚既要用于地址信号又要用于数据信号,这时就可以用锁存器先将地址锁存起来。

并不是一定要接锁存器,要看其地址线和数据线的安排,只有数据和地址线复用的情况下才会需要锁存器,其目的是防止在传数据时,地址线被数据所影响! 这是由单片机数据与地址总线复用造成的,接 RAM 时加锁存器是为了锁存地址信号。

如果单片机的总线接口只作一种用途,不需要接锁存器;如果单片机的总线接口要作两种用途,就要用两个锁存器。例如:一个口要控制两个 LED,对第一个 LED 送数据时,“打开”第一个锁存器而“锁住”第二个锁存器,使第二个 LED 上的数据不变。对第二个 LED 送数据时,“打开”第二个锁存器而“锁住”第一个锁存器,使第一个 LED 上的数据不变。如果单片机的一个口要做三种用途,则可用三个锁存器,操作过程相似。然而在实际应用中,我们并不这样做,只用一个锁存器就可以了(这不逗我吗?!),并用一根 I/O 口线作为对锁存器的控制之用(接 74373 的LE,而OE可恒接地)。所以,就这一种用法而言,可以把锁存器视为单片机的 I/O 口的扩展器。

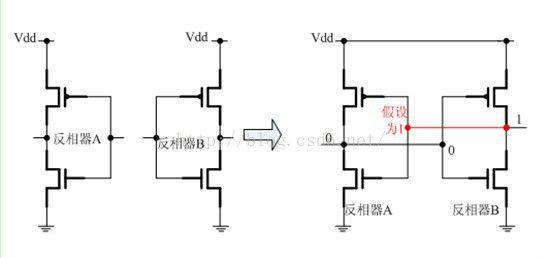

锁存器工作原理(反正我能看懂)

CMOS反相器的功能是可以使输出获得跟输入相反的逻辑值,那如果把两个反相器的输入跟输出连接在一起会出现什么情况呢?我们来看下图,假设某个时刻反向器A的输入是1,那么其输出会是0;因为A的输出连接到B的输入端,即反相器B的输入为0,那么其输出会变为1;又因为B的输出连接到A的输入端,即B输出的1反馈回A的输入,对刚才假设的“A的输入为1”进行了确认和加强。此时A的输入确实为1,按A和B的输入输出连接关系,又走了一遍刚才的路程,如此循环,结果是反相器A的输出稳定为0,反相器B的输出稳定为1。这个结构的电路有两个稳定的状态,一般称之为双稳态电路。可见类似的双稳态电路可以稳定地保持其节点中的值(数据),具有记忆功能,这就是锁存器工作的原理。

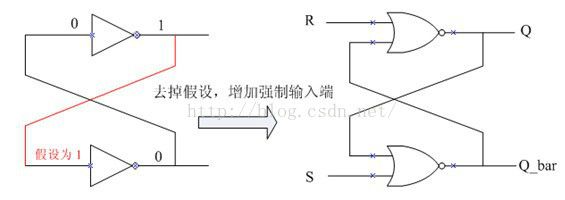

从上面介绍可看出,首尾相接的两个反相器构成了互相反馈耦合的形态,这就是锁存器的基本电路结构。但是这里是基于一个假设,假设反相器A的输入为1,那么它的输出为0,两个反相器连在一起通过互相反馈加强,则能保持0和1两个值。如果没有这个假设,它能保存的值将是不确定的。这类似于“鸡生蛋还是蛋生鸡”的谜局(你瞅瞅,多形象啊),要将此电路当锁存器使用,就必须打破这个“是输入先有0,还是输出先反馈回1”的僵局。于是给它加了两个输入端,由于反相器只有1个输入,因此改用或非门来代替。电路结构如下图,根据或非门“只要有一个输入为1,其输出就为0”的特性(我想了一下,确实有道理),当R为1时,虽然有反馈存在,也可以强制输出Q=0;当S为1时,则强制输出Q=1。这就是R-S锁存器,R意为Reset,清零的意思;S意为Set,置1的意思。

什么,你说你还是不懂,那好,我们换个方式复习一遍,重新讲一下注意,现在换成了与非门。

一般来说,在存储模式中,输入{\displaystyle {\bar {S}}}及{\displaystyle {\bar {R}}}的电压都是高的,逻辑上的1,(换句话说,S及R的电压应该是低的,逻辑上的0,而输出{\displaystyle Q}及{\displaystyle {\bar {Q}}}则维持其原有的数值,其中{\displaystyle {\bar {Q}}}为{\displaystyle Q}的相反。但当{\displaystyle {\bar {S}}}(设定)被设定为逻辑0而{\displaystyle {\bar {R}}}是逻辑1的时候,输出{\displaystyle Q}就会变成逻辑1(因为0与任何逻辑都是0然后取反一定是1)。之后无论{\displaystyle {\bar {S}}}是否回复到逻辑1,{\displaystyle Q}亦会维持逻辑1的状态(因为Q的反相作为一个输入,始终为0)。另一方面,如果{\displaystyle {\bar {R}}}(重设)被设定为逻辑0而{\displaystyle {\bar {S}}}是逻辑1的时候(R设定为0则一定为1,又因为是1,所以经过与非门到达Q的时候为0),输出{\displaystyle Q}就会变成逻辑零。同样地,无论{\displaystyle {\bar {R}}}是否恢复到逻辑1(因为Q作为一个输入0导致一定为1,又因为是1,所以Q维持逻辑0),{\displaystyle Q}亦会维持逻辑零的状态。要注意一点就是{\displaystyle {\bar {S}}}及{\displaystyle {\bar {R}}}都不可以同一时间为逻辑上的0,故我们要在设计上避免这一个情况出现。

| SR锁存器真值表 (注意:这里用的是S及R,而非文中的{\displaystyle {\bar {S}}}及{\displaystyle {\bar {R}}}) |

||||

| S | R | Q | Qnext | 解释 |

| 0 | 0 | 0 | 0 | 维持 |

| 0 | 0 | 1 | 1 | 维持 |

| 0 | 1 | 0 | 0 | 重设 |

| 0 | 1 | 1 | 0 | 重设 |

| 1 | 0 | 0 | 1 | 设定 |

| 1 | 0 | 1 | 1 | 设定 |

| 1 | 1 | 0 | - | 不允许 |

| 1 | 1 | 1 | - | 不允许 |

触发器

触发器的线路图由逻辑门组合而成,其结构均由SR锁存器派生而来(广义的触发器包括锁存器)。触发器可以处理输入、输出信号和时钟频率之间的相互影响。

在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态。把这种在时钟信号触发时才能动作的存储单元电路称为触发器,以区别没有时钟信号控制的锁存器。

D触发器有一个输入、一个输出和一个时钟频率输入,当时钟频率由0转为1时,输出的值会和输入的值相等。此类触发器可用于防止因为噪声所带来的错误,以及通过管道增加处理数据的数量。

在R-S锁存器的前面加一个由两个与门和一个非门构成的附加电路,则构成D触发器。当时钟脉冲CP为1时,读入输入端D的数据并传至输出端;当CP为0时,根据与门“只要有一个输入端为0则输出为0”的特性,输入端D的数据被与门屏蔽了,无法到达输出端,不管输入D怎样变化,Q端输出值都保持不变,只有等到下一个CP高电平到来时,才会把当前的D值送出。这样就实现了延迟输出即暂时保存的功能。从电路的动作可以看出,时钟输入端起到控制的作用,CP为1时,能触发后面的锁存器把D的值暂时锁存起来,这也正是触发器名词中“触发”的含义,这正是触发器与锁存器的联系与区别:触发器利用了锁存器的保存原理,但是加上了触发功能,可以控制保存的时间。

存储器

存储元是存储器中最小存储单元,它的作用是用来存放一位二进制代码0或1。任何具有两个稳定状态(双稳态)的物理器件都可以来做存储元。例如,一个双稳态半导体电路或一个CMOS晶体管或磁性材料的存储元,均可以存储一个二进制代码。

CPU不能像访问内存那样,直接访问外存,外存要与CPU或I/O设备进行数据传输,必须通过内存进行。

由若干个存储元组成一个存储单元。一个存储器包含许多存储单元,每个存储单元可存放一个字节(按字节编址)。每个存储单元的位置都有一个编号,即地址,一般用十六进制表示。一个存储器中所有存储单元可存放数据的总和称为它的存储容量。假设一个存储器的地址码由20位二进制数(即5位十六进制数)组成,则可表示2的20次方,即1M个存储单元地址。每个存储单元存放一个字节,则该存储器的存储容量为1MB。

CMOS(Complementary Metal Oxide Semiconductor),互补金属氧化物半导体,电压控制的一种放大器件,是组成CMOS数字集成电路的基本单元。CMOS由PMOS管和NMOS管共同构成,它的特点是低功耗。由于CMOS中一对MOS组成的门电路在瞬间要么PMOS导通、要么NMOS导通、要么都截止,比线性的三极管(BJT)效率要高得多,因此功耗很低,因此,计算机里一个纽扣电池就可以给它长时间地提供电力。

ZYNQ的启动与配置

ZYNQ有两种启动模式:从BootROM主动启动,从JTAG被动启动。

与Xilinx7系列的器件不同的是,ZYNQ-7000 AP SOC并不支持从PL端直接进行启动配置。

ZYNQ-7000 AP SOC启动配置通常按照如下三个阶段进行:

1、BootROM,BootROM中的代码是固化的,处理器核在上电或者热启动时自动执行这部分代码。

2、第一阶段启动加载器FSBL,可由用户代码控制。(完成PS端的初始化,使用比特流文件对PL进行配置,跳转到SSBL执行)

3、由用户PS端设计代码控制,也可以是第二阶段启动加载器SSBL,这个阶段完全由用户控制,是可选的。(初始化CPU,并将操作系统加载到内存当中,对于运行在ZYNQ上的Linux系统而言,U-boot就是SSBL,是一个开源的引导程序,u_boot最后会把系统控制权交给Linux内核)