关于DM814x系统学习

一、DM814x体系架构

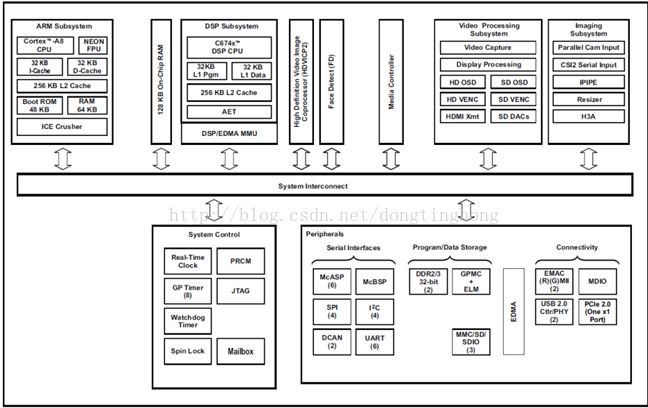

4核心:A8(arm) + M3 VIDEO + M3 VPSS + DSP(c674x)

A8:图片码流收发,网络服务,消息控制,其他应用等,LINUX 1.0GHZ;

M3 VIDEO:图片H264、MJPEG编解码等,BIOS6 280MHZ;

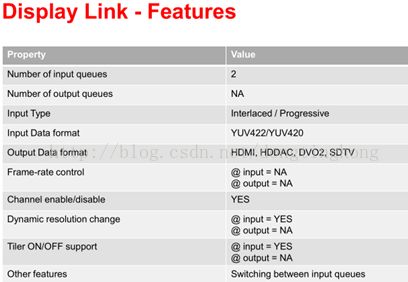

M3 VPSS:Camera采集,Capture采集,ISP,SIMCOP,Display(HDMI,SDO,HDO),MJPEG编码,SCALAR,NSF,FD等,BIOS6 280MHZ;

DSP:alg图像智能处理算法等,BIOS6 700MHZ;

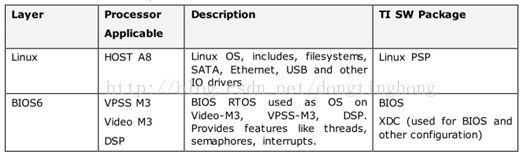

操作系统:

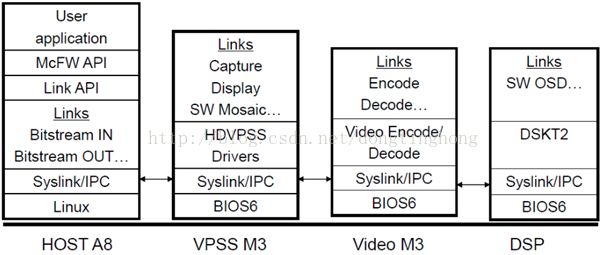

二、软件架构(syslink)

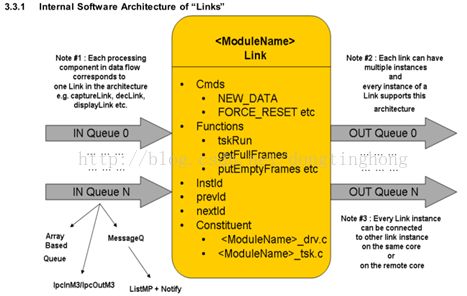

系统通过syslink的link机制来进行数据流的搭建,核与核之间是通过syslink的ipc通信机制进行通信的,syslink是建立于操作系统之上的集任务和消息通信于一身的软件架构,故每个核须跑操作系统。通过编写一个link来完成特定的任务,一个link相当于一个特殊的线程,link内部必须完成对数据流的控制和消息的通信。Syslink软件架构如下图:

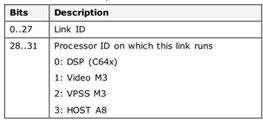

LINK ID:每个link都包含一个唯一的32位的link ID,高4位是处理器的ID,低28位是link id号:

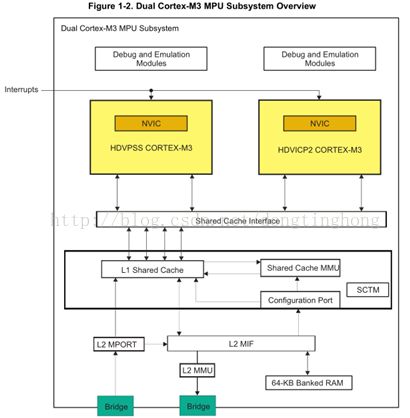

关于syslink详情见TI提供的介绍文档。SDK已集成的links如下,可以自己编写添加别的link:

MPSCALAR: YUV422I/YUV420->YUV422I,mpW*mpH->1920*1080 (mpW*mpH>=1080p)

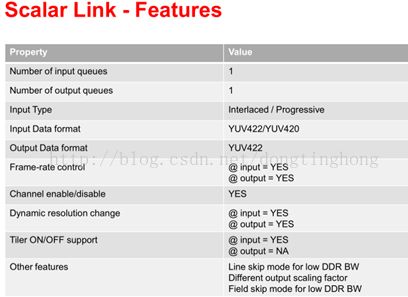

SCALAR: YUV422I/YUV420SP->YUV422I,W*H->scW*scH (W*H<=1080p,scW*scH<=1080p)

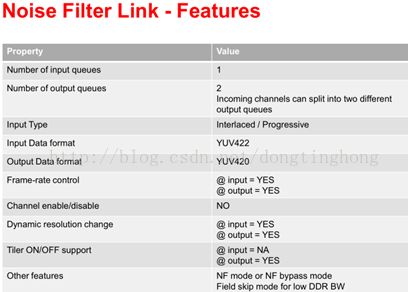

NSF: YUV422I->YUV420SP

Syslink API:

| API |

Description |

| System_linkCreate |

Creates a link- allocates driver, codec, memory resources. |

| System_linkGetInfo |

Getinformation about a link like number of channels, properties ofeach channel. MUST be called after System_linkCreate() for a link |

| System_linkStart |

Start the link- starts the driver or codec |

| System_linkControl |

Send a linkspecific control command with optional arguments |

| System_linkStop |

Stop the link- stops the driver or codec |

| System_linkDelete |

Deletes a link- free‟s driver, codec, memory resources |

Link的建立:

1.在link_api目录下添加相应的link头文件;

2.在system_linkId.h中添加相应的id定义;

3.在相应模块中添加_priv.h和_tsk.c;

4.在src_bios6\links_common\system\system_priv_common.h中添加相应的优先级定义,添加栈大小的定义;

5.在System_xxx.c(如在dsp中是System_c6xdsp.c)中调用相应的init接deInit接口;

6.在ipnc_mcfw\mcfw\src_linux\mcfw_api\ti_vsys_priv.h中添加相应的头文件;

7.在链路搭建中使用link.

Link内部必须完成任务的初始化和反初始化:xxxLink_init(), xxxLink_deInit()。

Link内部必须完成create时候的初始化:xxxLink_create(),在System_linkCreate()的时候会调用到这里来。

Link内部必须完成数据流的控制:定义取buffer(xxxLink_getFullFrame)、还buffer(xxxLink_putEmptyFrame)和取linkInfo(xxxLink_getLinkInfo)的接口并在init接口中注册这这些接口(回调函数)。

Link的消息的通信:定义相应的消息ID,定义相应的消息处理函数,在xxxLink_tskMain任务主函数循环内部添加相应消息ID处理函数的调用。

Chain的搭建:

根据应用的需求我们需要把数据的处理流程先整理出来,然后把每个数据处理的关键环节写成link,因为Link内部已经完成了对数据流的控制,然后我们只要把这些link按照流程链接起来就完成了,chain就是把link链接起来搭建成完整的数据流链路的过程。需要注意的是,chain的搭建(create)需要从数据源link开始搭建,并且要正确的按照数据流顺序来搭建;chain的停止(stop)也需要从数据源link开始停止;而chain的销毁(delete)则要反过来,从数据流的末端开始销毁。

关于link的搭建的几点注意事项:

(1)ipcFrameInLink 后面必须接dupLink(如果链路还要继续走),否则会出错,原因是ipcFrameInLink使用了帧头的一些信息,后面的link(一般的link)会将这些信息丢掉,而dupLink会先保存帧头信息,等还buffer的时候再重新拷贝回去。

(2)对于核间交互的link即带有ipc头的link,需要特别注意prevLinkQueId,前后2个ipcLink都不需要注意prevLinkQueId(除非是最后一个link了),但是ipcInLink的下一个link的prevLinkQueId必须跟ipcOutLink的前一个link的queId匹配链路才能搭建成功,例如:

ispCreatePrms.numOutQueue = 2;

ispCreatePrms.outQueuePrm[0].nextLink = xxx;

ispCreatePrms.outQueuePrm[1].nextLink = ipcM3OutVpssLinkId;

ipcM3OutVpssPrms.inQueParams.prevLinkId = ispLinkId;

ipcM3OutVpssPrms.inQueParams.prevLinkQueId = 0/1; //0 or 1 or other may work

ipcM3OutVpssPrms.outQueParams.nextLink = ipcM3InVideoLinkId;

ipcM3InVideoPrms.inQueParams.prevLinkId = ipcM3OutVpssLinkId;

ipcM3InVideoPrms.inQueParams.prevLinkQueId = 0/1; //or other may work, don’t care

ipcM3InVideoPrms.outQueParams.nextLink = encLinkId;

encLinkPrms.inQueParams.preLinkId = ipcM3InVideoLinkId;

encLinkPrms.inQueParams.preLinkQueId = 1; //should be 1, only care ispLink out queid

这是因为ipcM3Out或ipcM3In纯粹是将前一个link的所有linkInfo拷贝给下一个link,而不会按照queid只读取que的信息给下一个link。

(3)mergeLink是多进一出,进来的que都被merge到channel上,merge的过程是按顺序merge的,如进来有3个que,que0本身有2个通道,que1有一个通道,que2有2个通道,则merge后的通道0和1分别对应于que0的通道0和1,通道2对应于que1的通道0,通道3和4分别对应于que2的通道0和1。mergeLink可以和selectLink一起使用,selectLink是选择某一个通道转成que。

三、A8核

略。

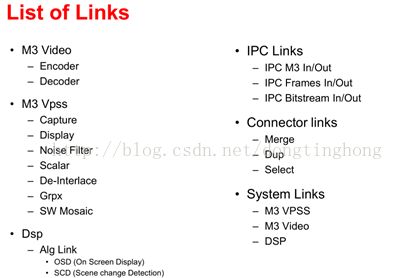

四、VIDEO M3核

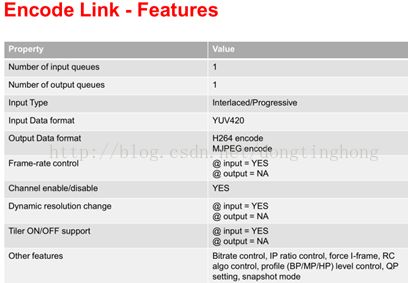

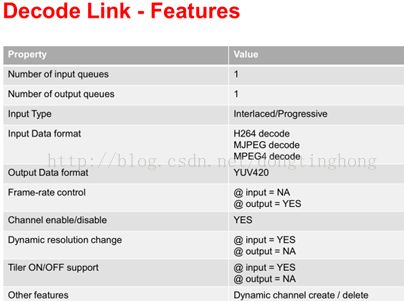

也叫HDVICP2,与VPSS M3共用一个媒体控制器,共享cache。有视频编解码的硬件模块,完成H264、MJPEG的编解码。

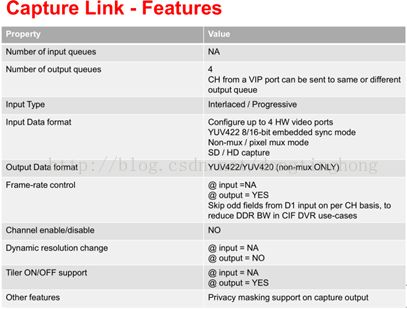

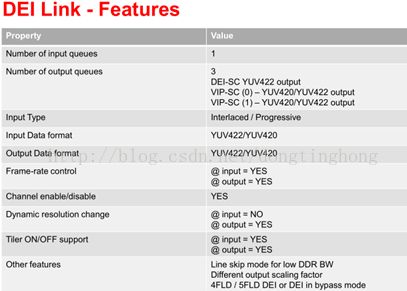

五、VPSS M3核

与VIDEO M3共用一个媒体控制器。有Camera,Capture,ISP5,SIMCOP,Display(HDMI,SDO,HDO),MJPEG,SCALAR,NSF,FD等视频采集处理模块。其中Camera、ISP5与SIMCOP集成在ISS中,而MJPEG用SIMCOP来做的,TI SDK已经编成相应的库。Capture、Display、SCALAR和NSF集成在HDVPSS中。这些模块均有硬件来完成。

左边黄色框为SIMCOP模块,右边为Camera采集模块(CSI2串行采集口和CPI并行采集口)和ISP5。Camera ISP数据流:(1)CPI -> IPIPEIF -> ISIF -> DDR; (2)CPI -> IPIPEIF -> ISIF -> H3A -> DDR; (3)CPI -> IPIPEIF -> IPIPE -> DDR; (4)CPI -> IPIPEIF -> IPIPE -> RSZ -> DDR.

SIMCOP叫做静态图像协处理器(still image coprocessor),功能有图像编解码(如MJPEG)和图像数据处理(如直方图统计等),是基于微块内存到内存(M2M)的图像处理引擎,有单独的cpu,可编程。硬件模块有DMA、LDC(畸变矫正)、DCT(离散余弦变换)、VLCDJ(JPEG编解码)、NSF2(二维时域降噪)、NSF3(三维时空降噪)、ROT(块旋转)、IMX A&B(可编程图像处理引擎),时钟由ISS提供。该模块的开发需要TI提供相关的文档。

做图像的可能都会用到缩放,ISP里面有一个缩放模块RESIZER,由RSZ A和RSZ B组成。A和B可以同时工作,也可以只使用A,分别实现2种或1种分辨率的输出,可以放大也可以缩小。需要注意的是RSZ A和RSZ B,输出的分辨率和倍数有限制,RSZ A缩放后的图像宽度必须小于等于5376,RSZ B缩放后的图像宽度必须小于等于2336,高度都没有特别的限制;放大倍数也有限制,Normal模式下最大放大20倍和最小缩小1/16倍,如果是DownScaling模式(需要修改底层寄存器的配置)则只能用于缩小,最小到1/4096倍。另外,RSZ A和RSZ B是同源同时钟工作的,即它们的数据源必须相同(不能同时配不同的图像,一张给A缩放另一张给B缩放),也共用一个时钟,故它们的步伐是一致的,所以缩放的快慢取决于输出的最大分辨率。ISP的时钟配置是这样的,ISP的时钟是基于ISS的分频,其实是先倍频后分频,从ispLink参数配置可以看出(clkDivM倍频和clkDivN分频),相应一个是读时钟ISS_FCLK*clkDivM/clkDivN(IPIPE或IPIPEIF时钟,不知道内部是否还有时钟细分不得而知),一个是写时钟ISS_FCLK,这是因为读时钟是将数据从内存读到fifo里面和数据处理的时钟,写时钟相当于数据写入内存的时钟,根据图像输出的分辨率读时钟必须小于写时钟,故这2个时钟必须正确配置才能良好工作,否则会发生溢出(resz overflow)的情况。故ISP的时钟配置必须符合以下条件:

ISS_FCLK*(clkDivM/clkDivN) / ISS_FCLK <= input resolution / max output resolution

即:clkDivN/clkDivM >= max output resolution / input resolution (M2M)

关于ISP时钟可能我理解的有偏差,最好参考ISS文档,但是经过测试的确是需要符合以上的条件的。

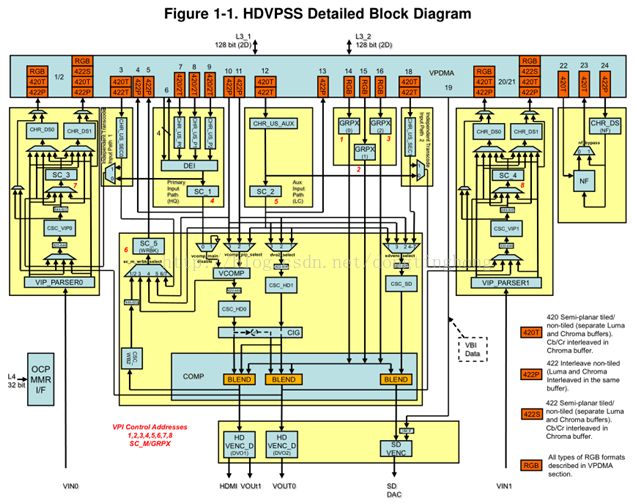

2. HDVPSS架构

HDVPSS有2个采集口,VIN0和VIN1,支持进来的数据有YUV422P、YUV444I、RGB,可以转换为YUV420SP、YUV422I、YUV422SP、RGB等数据格式存储到DDR中。

数据流:

VIN0 -> VIP_PARSER0 -> ..... -> CHR_DS0 -> VPDMA -> DDR3。

其他参见Capture图像采集总结.doc.

六、DSP核

DSP库的添加:

在ipnc_rdk\ipnc_mcfw\mcfw\src_bios6\links_c6xdsp目录下新建一个目录/libs,将编好的dsp库放到这个目录下,然后在ipnc_rdk\ipnc_mcfw\makerules\rules_c674.mk文件中变量LIB_PATHS后面添加库的绝对路径和库名,在link里面包含库头文件后就可以调用库的接口了。

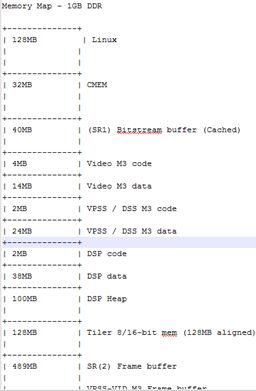

七、内存分配

系统内存分配是在一个.bld文件中修改的,该文件位于ipnc_rdk\ipnc_mcfw\mcfw\src_bios6\cfg\ti814x目录下:

M3、DSP和A8的配置都是在这个目录下相关的文件进行配置的,如DSP cache的配置(FC_RMAN_IRES_c6xdsp.cfg)。