FPGA开发之综合选项整理

本文介绍了fpga开发工具综合选项的功能与应用,EDA工具版本为vivado17.4

\quad\enspace

1、 -flatten_hierarchy

full:

\quad\enspace 综合时将原始设计打平,只保留顶层层次,执行边界优化

none:

\quad\enspace 综合时完全保留原始设计层次,不执行边界优化。综合的输出与原始RTL有相同的层次化结构。

rebuilt::

\quad\enspace 设置后,rebuild允许合成工具将层次结构扁平化。执行综合,然后基于原始RTL重建层次结构。这个值允许QoR受益于跨边界优化,最终的层次结构类似于RTL,便于分析。

当-flatten_hierarchy为none时消耗的寄存器最多,建议其设定为默认值rebuilt。

2、 -gated_clock_conversion

Off:禁止门控时钟转化

On:如果在RTL代码中设置了门控时钟属性就会执行门控时钟转化

Auto:在以下两种情况发生的情况下执行门控时钟转化:

1) 门控时钟属性设置为真。

2) 综合工具检测到了门控时钟并且有有效的时钟约束设置。

例:

(* gated_clock = “true” *) input clk;

3、 -bufg

\quad\enspace 控制工具在设计中推断出多少bug。当设计网络列表中的其他BUFGs对合成过程不可见时,Vivado设计工具就会使用此选项。

4、 -fanout_limit

\quad\enspace 在开始复制逻辑之前指定必须驱动的负载信号总量。这个全局限制是一个通用的指南,当工具确定有必要时,它可以忽略这个选项。如下:可手动设置信号的扇出大小。

例:

(* max_fanout = 50 *) reg sig;

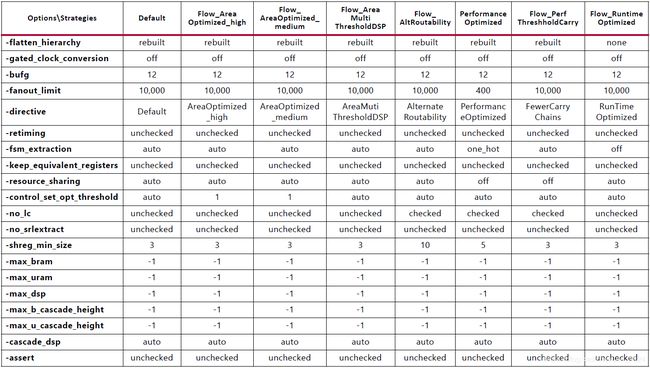

5、 -Directive

\quad\enspace 取代了–effort_leve选项。当指定时,综合工具以不同的优化运行综合。

\quad\enspace 具体选项参见本文末尾表格

6、 -retiming

\quad\enspace 这是一个布尔选项,通过自动移动寄存器(寄存器平衡)、交叉组合门电路或lut提高内部时钟顺序路径的电路性能。它保持了电路的原始行为和延迟,不需要改变RTL源。默认是关闭的。

7、 -fsm_extraction

\quad\enspace 用于设定状态机的编码方式,默认值为auto。

例:

(* fsm_encoding = “one_hot” *)reg [7:0] state;

8、 -keep_equivalent_registers

\quad\enspace 共享同源寄存器,勾选时不共享,不勾选时共享。

module equivalent(

input clk,

input dataIn_a,

input dataIn_b,

output result_a,

output result_b

);

reg oper_a1;

reg oper_a2;

reg oper_b;

reg result_a;

reg result_b;

always @(posedge clk)

begin

oper_a1 <= dataIn_a;

oper_a2 <= dataIn_a;

oper_b <= dataIn_b;

result_a <= oper_a1 && oper_b;

result_b <= oper_a2 || oper_b;

end

endmodle

不勾选:

勾选:

9、 -resource_sharing

其目的是对算术运算通过资源共享优化设计资源

10、 -control_set_opt_threshold

\quad\enspace 触发器的控制集由时钟信号、复位/置位信号和使能信号构成,通常只有{clk,set/rst,ce}均相同的触发器才可以被放置在一个SLICE中。

\quad\enspace control_set_opt_threshold的值为控制信号(不包括时钟和数据)的扇出个数,表明对小于此值的同步信号进行优化,显然此值越大,被优化的触发器越多,但占用的查找表也越多。

\quad\enspace control_set_opt_threshold的值为0,不进行优化。

auto:默认值

11、 -no_lc

\quad\enspace 对于一个x输入布尔表达式和一个y输入的布尔表达式,只要满足x + y ≤5(相同变量只算一次),这两个布尔表达式就可以放置在一个LUT6中实现。

\quad\enspace 当-no_lc被勾选时,则不允许出现LUT整合。

\quad\enspace 通过LUT整合可以降低LUT的资源消耗率,但也可能导致布线拥塞。因此,xilinx建议,当整合的LUT超过了LUT总量的15%时,应考虑勾选-no_lc,关掉LUT整合。

12、 -no_srlextract

\quad\enspace 当被选中时,此选项将关闭完整设计的SRL提取,以便它们被实现为简单的寄存器。

13、 -shreg_min_size

\quad\enspace shreg_min_size决定了当VHDL代码描述的移位寄存器深度大于此设定值时,将采用“触发器+SRL+触发器”的方式实现。

14、 -max_bram

\quad\enspace 描述设计中允许的块RAM的最大数目。通常这是在设计中有黑盒子或第三方网络列表时使用的,并允许设计者为这些网络列表保留空间。

15、 -max_uram

\quad\enspace 设置设计中允许的最大UltraRAM (UltraScale+™设备块ram)块数。默认设置为-1表示工具选择指定器件允许的最大数量。

16、 -max_dsp

\quad\enspace 描述了在设计中允许的块DSP的最大数量。通常在设计中有黑盒子或第三方网络列表时使用,并为这些网络列表留出空间。默认设置为-1表示工具选择指定器件允许的最大数量。

17、 -max_bram_cascade_height

\quad\enspace 控制工具可以级联的最大BRAM数量。默认设置为-1表示工具选择指定器件允许的最大数量。

例:

(* cascade_height=4 *) reg [31:0] ram[(2**15) - 1:0];

18、 -max_uram_cascade_height

\quad\enspace 控制工具可以级联的最大UltraRAM数量。默认设置为-1表示工具选择指定器件允许的最大数量。

19、 -cascade_dsp

\quad\enspace 控制加法器和DSP块输出是如何实现的。默认情况下,DSP输出的和使用块内置加法器链计算。取值为tree时强制在fabric中实现求和。默认值是auto。

20、 -assert

\quad\enspace 使能VHDL生成状态信息去评估。严重级别的失败或错误将停止综合流程并产生一个错误。严重级别的警告产生一个警告。