[转载自 SI-list【中国】http://mp.weixin.qq.com/s/qsdfzQwIVjvwHXuCdvrPXA ]

本篇对2017年初版Cadence的全套所有EDA工具的技术特性特点做一深入的分析,并与EDA其它主流厂商的对应工具进行比较。也为在校学习集成电路设计的学生们做一简单的科普,因为在学校学到的东西与在商业上做实际芯片设计是有很大区别的。

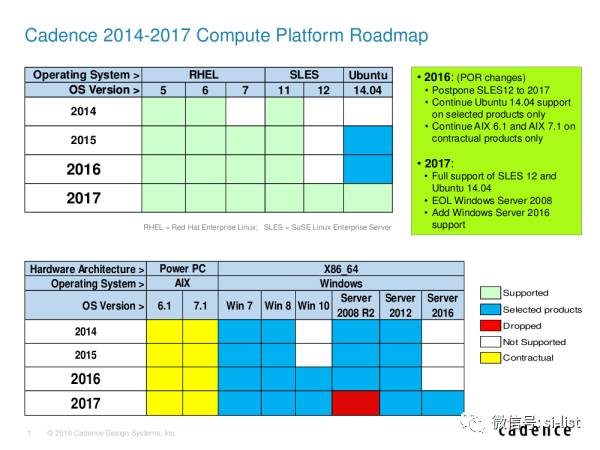

先来回答一个在国内经常被问到的问题:为何大部分EDA工具都是使用Linux平台而不是普通的Windows平台?这其实很好理解,因为多数工程及科技软件原先都是在UNIX平台上首先开发和使用的。这些工具出现的时候还没有微软的Windows呢。一些工程和科技软件被移植到Windows上去还是在上世纪九十年代末期和2000年以后的事。若读者在2000年之前或更早去米国研究型大学工学院中的计算中心和实验室访问或学习工作的话,见到的都是一排排的UNIX工作站,根本没有PC。虽然Windows在办公等日常工具上后来居上占据了主导地位,但像EDA工具这样的工程软件依然继续延续在UNIX及后来的Linux平台上开发和应用,多数并未被移植到Windows平台上。因为UNIX及后来的Linux所具有的真正多用户分布式系统(微软Windows不是真正的多用户系统!)等特点特别适合工程及科技软件。而随着Linux系统逐步取代UNIX系统,EDA工具现在也基本上全面移植转移到了Linux平台上。例如Cadence的计算平台路线图的规划所示,除了原先收购进的OrCAD还在使用Windows外,其他工具都已经移植转移到了Linux平台,而以前的UNIX平台如HPUX、Solaris、SunOS等现在都已经终止使用,IBM的AIX平台也只在某些合同下继续开发某些特定EDA工具。从这里也可以为在校学习集成电路设计的学生们指明一条路,即若准备将来在集成电路行业中开拓职业事业的话,就必须熟练掌握Linux这个必备的系统工具。现实是Linux(Andoid)和UNIX(iOS)已经在移动设备上占据了主导地位,所以即便不准备在集成电路这个行业开辟职业事业,熟练掌握Linux也会在其他行业中取得职业事业的发展机会。

下面将2017年初版Cadence全套EDA工具按照Cadence的官方分类共六大类EDA完整列表如下。

工具列出的格式为:工具全名称:工具代号及版本号 (当前的安装版本)。

Custom IC Design:

-

Integrated Circuit (Virtuoso): IC 6.1.7 (IC06.17.708_Hotfix)

-

Integrated Circuit (Advanced Node Virtuoso): ICADV 12.3 (ICADV12.30.700_Base)

-

Spectre Circuit Simulators: SPECTRE 16.1 (SPECTRE16.10.187-ISR1_Hotfix)

-

Virtuoso IP Foundation Characterization: LIBERATE 15.1(LIBERATE15.15.070_Hotfix)

Design for Manufacturing:

-

Assura Physical Verification: ASSURA 4.1 (ASSURA04.15.108-617_Hotfix)

-

Extraction Tools (Quantus QRC): EXT 16.1 (EXT16.10.000_Base)

-

Physical Verification Systems: PVS 15.2 (PVS15.21.000_Hotfix)

-

Manufacturability and Variability Sign-Off: MVS 16.2 (MVS16.20.000_Base)

Digital IC Design:

-

Encounter Conformal: CONFRML 16.2 (CONFRML16.20.140_Hotfix)

-

Genus Synthesis Solution: Genus 16.2 (GENUS16.20.000_Base)

-

Innovus Implementation System: Innovus 16.2 (INNOVUS16.20.000_Base)

-

Joules RTL Power Analysis: Joules 16.1 (JLS16.15.000-ISR5_Hotfix)

-

Modus Test Solution: Modus 16.2 (MODUS16.20.000_Base)

-

Silicon Signoff and Verification (Tempus/Voltus IC):SSV 16.2 (SSV16.20.000_Base)

-

Stratus High-Level Synthesis: STRATUS 16.1 (STRATUS16.16.100_Update)

Functional Verification:

-

Indago Debug Platform: INDAGO 2016.11 (INDAGOMAIN2016.11.001_Base)

-

JasperGold Apps: JASPERGOLD 16.0 (JASPERGOLD16.12.000-INCISIVE1520_Base)

-

Metric-Driven Verification: MDV 20161.11 (MDVMAIN2016.11.003_Hotfix)

-

RocketSim Parallel Simulation Engine: RockSim 16.1 (ROCKSIM02.00.021_Update)

-

Verification IP: VIPCAT 11.3 (VIPCAT11.30.045_Update)

-

Xcelium Verification Platform: XCELIUM 2016.11 (XCELIUMMAIN2016.11.001_Base)

Silicon-Package-Board Co-Design:

-

Allegro ECAD-MCAD Library Creator: SPBS 17.2 (SPBS17.21.000_Base)

-

Allegro Sigrity: SIGRITY 2017 (SIG17.00.000_Base)

-

OpenPOWER Compliance Kits in Sigrity2017: (SIG17.00.000-MODEL_OpenPOWER_Library)

-

Silicon-Package-Board Co-Design: SPB 17.2 (SPB17.20.009_Hotfix)

Verification Accelerator and Emulator:

-

Memory Model Portfolio: MMP 16.1 (MMP16.10.000_Base)

-

Palladium Applications: PDAPP 16.1 (PDAPP16.10.000_Base)

-

Protium Rapid Prototyping Platform. Protium 16.1 (PTM16.10.000_Base)

-

Palladium XP (Unified Xccelerator Emulator): UXE 15.1 (UXE15.10.000_Base)

-

Palladium Z1 (Verification Xccelerator Emulator): VXE 16.1 (VXE16.10.000_Base)

Cadence Help Tools: (CADENCEHELP02.30.006_Tools)

现在对2017年初最新版Cadence全套工具各个工具的功用和技术性能特点做一概略分析,并与其他主流EDA厂商的对应产品做比较。众所周知,Cadence是EDA(Electronics Design Automation电子设计自动化)产业界的头号厂商,EDA三巨头(Cadence,Synopsys和Mentor Graphics)中的老大(国内用户似乎对Synopsys更熟悉)。它的众多EDA工具在IC集成电路芯片和PCB电路版的设计与验证流程中在业界占据领先地位,其他厂商的EDA工具产品在与其竞争中有成功也有失败。下面也是按照Cadence的官方六大分类分别对其中的各个EDA工具进行分析比较。

Custom IC Design定制芯片设计

-

Integrated Circuit (Virtuoso): IC 6.1.7 (IC06.17.708_Hotfix)

IC617是Cadence知名的Virtuoso定制芯片设计工具套件,在定制芯片设计中占据统治地位——Virtuoso在全定制芯片(Full Custom)和AMS(Analog Mixed Signal)混合信号芯片/版图(Layout)工具市场上占据接近80%的市场份额!Virtuoso是绝大多数定制芯片设计用户所寻求的工具(EDA of Choice)。Cadence在定制芯片设计市场上的影响如此之大,以至于各个主流芯片代工厂商Foundries基本上都专门为其开发PDK供给芯片设计客户使用。有许多人将IC Virtuoso这工具套件用作纯粹模拟/射频设计用途,这其实只用到了其中的一部分能力。Virtuoso最大的功用还是在混合信号(数字模拟——即Mixed Signal)芯片设计上,但也可以用作全定制数字(Full Custom Digital)芯片设计(是的,Virtuoso可以用来设计全定制数字芯片!——这就是为何Virtuoso包含了Verilog/VHDL以及Digital Implemantion等工具/功能在内。国内芯片设计业似乎大都对此并不是很清楚)!Virtuoso包括了前端到后端的全流程设计功能。与其他工具如多模仿真工具和物理验证工具等结合在一起使用构成了完整的定制芯片设计流程。需要指出的是Cadence每月都对其EDA工具中的某些工具进行升级,包括程序中的错误修正(bug fixings)和功能改进(很多都是用户建议的改进)等。大部分新功能的增加或旧功能的去除都是逐步渐进式(incremental)通过Hotfix版完成的。对Virtuoso来说通常是二至三个月出版一个Hotfix版进行升级。

IC617 Virtuoso的最大改变是引进了ADE(Analog Design Environment模拟设计环境)全新的三个工具:ADE Explorer,ADE Assembler,和ADE Verifier,用来替换以前版本中的ADE-L,ADE-XL和ADE-GXL。这里ADE Explorer和ADE Assembler取代了ADE-L,ADE-XL和ADE-GXL,而ADE Verifier则实际上可以称为ADE Planner,是一个模拟设计项目的规划管理工具。Cadence在此实际上将原来旧版本中的ADE-L和ADE-XL整合为ADE Explorer,而ADE Assembler则整合了原来的ADE-GXL。新版Virtuoso的其他主要部分(包括schematic,layout,AMS等工具)与之前的版本基本没有做巨大的更改(但小变动在每个Hotfix升级中则是经常发生的)。

Virtuoso的ADE是模拟设计和SPICE仿真图形界面事实上的业界标准。正因为如此,Cadence采取了不少手段以从中赚取更多利润。例如Cadence从IC6.1版起,将“标称值”SPICE仿真任务(单一特定条件与排错)与“多重”SPICE仿真任务(corners,sweeps,Monte Carlo)分离开来,形成一个三重价格体系模型再加上一个以每日每次使用记价的令牌(token)系统,让用户从ADE-L到ADE-XL再到ADE-GXL一级一级地支付更多的license许可证费用。而这一切nominal/corners/sweeps/monte carlo在旧版IC5.1.41中用户是一同完成的,并且还没有令牌系统在其中跟你玩。这个L-XL-GXL分离自然而然地惹恼了不少用户,给了竞争对手在定制芯片设计EDA上一个翻身的机会。只可惜其主要竞争对手不给力,基本没有拿出过硬的EDA产品来翻盘。例如Synopsys多年前发布的对应竞争工具Custom Designer就是一个不折不扣的失败尝试,虽然Custom Designer做得看上去像一个Virtuoso超级集合,但并没有因此赢得多少用户。现在Synopsys经过几年的收购(包括SpringSoft的Laker全套定制工具家族,Ciranova的Helix placer,和Magma的整套东西)后,将所有这些购进的东西打包整合在一起成为它新的Custom Compiler工具。所以Custom Compiler就是一个Laker加上Helix加上其他一些东西的重新包装,要用这样产品来吸引原本就异常稳固的Virtuoso庞大用户群基本盘恐怕是非常艰难的搏斗。在Mentor Graphics方面,也是通过收购诸如Pyxis,Tanner和Berkeley Design Automation(BDA)来试图渗透进定制芯片设计市场,但这些工具都缺乏类似Virtuoso中的ADE和layout版图等工具相似且完整的功能。Pyxis现在的方向基本上是做MEMS。而Tanner虽然给Mentor Graphics带来了一些客户,但绝大多数是低端设计或者是那些要便宜EDA工具的小公司。BDA的ACE看上去有希望,但还缺少类似Virtuoso的ADE那样的完整性能。总之,在定制芯片设计EDA市场上Cadence的Virtuoso基本盘非常稳固,其竞争对手都比较弱。而且新版ADE将旧版ADE中分离的标称值/corners/sweeps/蒙特卡罗/参数对比等功能都整合在ADE Explorer中,如此对芯片设计用户来说也就更具吸引力了。

Virtuoso的Voltus-Fi工具是在Virtuoso环境内与Quantus QRC(参见DFM设计大类EDA中的介绍)和SPECTRE(见下面的Spectre Circuit Simulators介绍)一同用于晶体管级noise/power signoff的工具。当前已经能够用于台积电的10nm/7nm节点工艺。其竞争对手是Ansys收购的Apache的Totem和Synopsys的HSim-PWRA。

Virtuoso的Analog Assisted Automation(模拟辅助自动化)功能就是画板上的Modgens。现在有了新的模式编辑器(pattern editor)和内置定制布线。

Virtuoso的IPVS在定制设计的运行中做signoff验收DRC检查,在Virtuoso中仅做瞬时DRC。能在16/14/10/7nm的FinFET/FD-SOI流程中做DPF奇回路检测并给设计者改进提示。注释浏览器交叉探查。

Virtuoso的版图EAD工具不需要LVS即可在设计内做实时RC提取。配有随机游动电容处理器,EM检查,电阻有限元网格化,电流限制/预算检查。还能在部分完成的版图上做寄生参数的重新仿真。版图工程师能够从版图得到立即反馈从而避免“rip and repair”综合症。EAD新功能还包括“电驱动”布线。Virtuoso的主要竞争对手Synopsys也试图在它的Custom Compiler工具中拷贝Cadence所有这些理念,但迄今为止Custom Compiler还没有能找到一线大客户。

-

Integrated Circuit (Advanced Node Virtuoso): ICADV 12.3 (ICADV12.30.700_Base)

ICADV就是IC Virtuoso在先进节点工艺制程(20nm以下节点工艺)上的版本。针对20nm以下节点工艺制程的定制芯片设计要用ICADV这个版本的Virtuoso,而不能使用IC Virtuoso。当前这个最新版本ICADV123能够用于最新7nm节点工艺制程的定制芯片设计——当然目前这只是少数几个有此财力物力人力的芯片设计大公司才利用最新7nm节点工艺制程了。ICADV可以做FinFET版图设计、根据track进行布线、row定义,SADP着色和MPT。

-

Spectre Circuit Simulators: SPECTRE 16.1 (SPECTRE16.10.187-ISR1_Hotfix)

这是Cadence的多模式仿真工具(Spectre,Spectre APS,Spectre XPS,Spectre RF等)用于定制芯片的前端设计和后端设计中的仿真,与Virtuoso一起使用。从16.1版开始,工具的名称代号改称为SPECTRE,而MMSIM则是15.1版及其之前版本的代号。所有其中相关工具名称也因此全部重新命名,例如原来名称为Virtuoso Spectre Circuit Simulator,现在改为Spectre Classic Simulator等等诸如此类。

Spectre XPS为FastSPICE工具可用于存储器设计。其benchmark基准测试要比Synopsys的HSPICE快3到4倍吞吐率。为多核运行,能按需智能快速或精确分区。

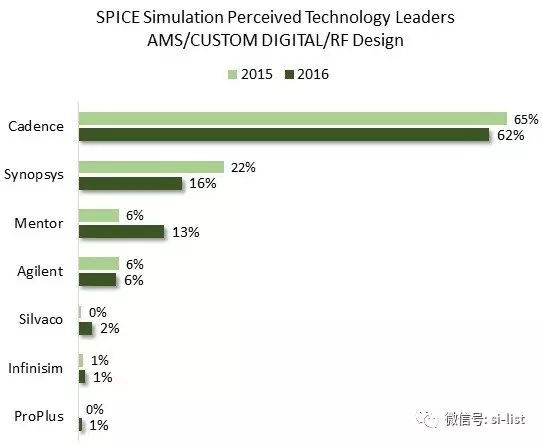

对北美芯片设计工程师(2015年317人,2016年246人)做的问卷调查(由加拿大一家EDA初创企业Solido Design Automation发起和资助的调查)显示的SPICE仿真在业界的使用状况:

可见不论是在芯片设计企业内部实际使用情况还是芯片设计工程师的主观意识里,Cadence的SPICE工具都是市场领先的仿真工具。

这同一个问卷调查还有SPICE在不同节点工艺上的分布情况:

其中几乎20%的SPICE是用于大于90nm节点的老工艺,因为20%的定制芯片是用于医疗设备、产品目录部件、工业控制器、手机基站、军用芯片等用途。这类芯片不需要先进的节点工艺,因此这些用途芯片使用成熟节点工艺,因为它们更便宜!

同时芯片设计使用的节点工艺有两大转移。一是从65nm转移至40nm,例如物联网和汽车芯片应用。另外就是芯片代工厂商在做低功耗40nm工艺版的65nm老芯片,例如台积电的40LP和GF的40LP。二是从28nm转移至16nm和10nm高性能FinFET芯片。这类芯片主要是类似苹果、高通、英特尔、英伟达、三星这类大品牌用于移动或高性能计算。总之,芯片设计主要依据应用场景以及成本来选择使用的节点工艺制程。先进节点工艺并不适用于所有应用,因而使用先进节点工艺设计的芯片在全体芯片应用中只占大约40%左右。

Spectre的简要来历:Spectre是由Ken Kundert在SPICE的诞生地伯克利加大读博士时创作的(其导师是Alberto Sangiovanni-Vincentelli教授——他也是EDA两大巨头Cadence和Synopsys的联合创始人Co-Founder!)。他取得博士后在Cadence领导开发了Spectre工具家族的主要部分,如Spectre、SpectreHDL、SpectreRF以及Verilog-A、Verilog-AMS、VHDL-AMS语言。知名的网络社区Designer's Guide Community也是由他联合创办的。

-

Virtuoso IP Foundation Characterization: LIBERATE 15.1 (LIBERATE15.15.070_Hotfix)

28nm及以下先进节点工艺制程的芯片设计需要用到许多附加的单元库views(多电压,多温度,增长的corners数目....),所以生成及维护所有这些单元库views在芯片设计流程中成为主要瓶颈问题。LIBERATE就是用于在先进节点工艺上为复杂的Soc芯片生成这些标准且复杂的单元库。这个工具原自Cadence收购的Altos设计自动化公司。

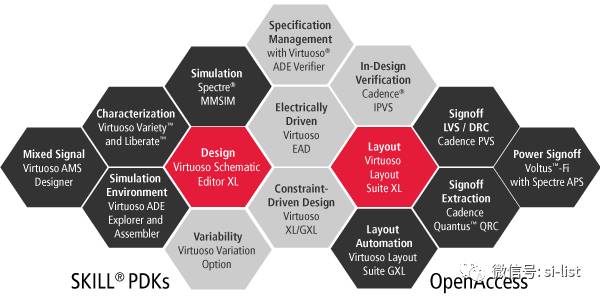

定制芯片设计流程:

Design for Manufacturing(DFM)可制造性设计

-

Assura Physical Verification: ASSURA 4.1 (ASSURA04.15.108-617_Hotfix)

Assura物理验证工具,用于芯片设计(包括前端和后端)流程中的DRC、LVS。

-

Extraction Tools (Quantus QRC): EXT 16.1 (EXT16.10.000_Base)

Quantus QRC为芯片寄生参数提取工具。其用户包括41个FinFET客户和3个FD-SOI客户。可在Virtuoso和Innovus环境内设计时运作。能用于二次暴光,3D-IC,16/14/10/7nm节点工艺建模。具备分布式处理,netlist缩减。竞争对手为Mentor Graphics的Calibre-xACT以及Synopsys的Star-RCXT。

-

Physical Verification Systems: PVS 15.2 (PVS15.21.000_Hotfix)

物理验证系统。这是Assura的升级换代产品,用于45nm以下节点工艺芯片设计流程中的DRC、LVS、XOR(LVL)、FastXOR、ERC、PERC、SVS。

以上工具中的物理验证功能(DRC/LVS)在芯片设计行业(特别是在芯片设计的sign-off验收完工阶段)通常都是用Mentor Graphics的Calibre工具代替,Calibre是芯片设计物理验证工具市场上的主导工具。当然Cadence的物理验证工具也有自己的特色,比如PVS中包含了MaskCompose,QuickView

-

Manufacturability and Variability Sign-Off: MVS 16.2 (MVS16.20.000_Base)

可制造性和可变性验收工具。这个工具中包含Litho Physical Analyzer,LDE Electrical Analyzer,CMP Predictor等工具。

LDE Electrical Analyzer用于优化和控制版图依赖效应(LDE)的影响,例如应力或阱邻近效应对设计性能的影响。这个工具直接插入到用户现存的定制模拟设计、IP设计、和基于单元的数字设计流程中帮助加速时序收敛。

Litho Physical Analyzer用于检测和矫正光刻热点等传统物理验证工具所忽略的可制造性问题以改进系统和参数的良品率并满足代工厂的DFM要求。

CMP Predictor预测化学机械抛光(CMP)的变化及其在设计上对整个层叠的影响,检测影响良品率的热点并生成改进指导。

以上工具都与Cadence的定制和数字设计平台紧密集成在一起帮助改进芯片设计的DFM。

Digital IC Design数字芯片设计

-

Encounter Conformal: CONFRML 16.2 (CONFRML16.20.140_Hotfix)

工具包括等效检查、功能工程修改、低功耗设计验证优化、约束设计。

Conformal ECO Designer为“最后一刻难解的ECO面积”产生拥塞感知的ECO。高通、博通、意法半导体都是这工具的用户。

Conformal Low Power从RTL到晶体管级做等效检查,支持IEEE 1801。客户包括ARM、高通、博通、Marvell等。

-

Genus Synthesis Solution: Genus 16.2 (GENUS16.20.000_Base)

Genus是大规模并行RTL和物理综合工具。声称比竞争对手Synopsys的Design Compiler快5倍,用户包括德州仪器、ImgTec等。

-

Innovus Implementation System: Innovus 16.2 (INNOVUS16.20.000_Base)

Innovus为Cadence于2015年发布的全新版数字芯片P&R布局布线版图设计工具,替代以前的Encounter平台。谣传称苹果曾经秘密地对Innovus进行benchmark基准测试与Synopsys的ICC2做比较,对比后苹果在其芯片设计中转而使用Innovus。后来Cadence的CEO陈立武在公司年报会议上宣称一家国际知名的公司与Cadence签署了5年EDA服务合同,这是Cadence近些年中曾经有过的最大合同。人们都在猜测这家大公司就是苹果。一些工程师在公开场合评论说Innovus在16nm/14nm节点工艺上表现良好,在10nm节点工艺中新的双重/三重/四重模式数字着色版图问题上取得成功,而Synopsys的ICC2对此类问题还无法应对。而后欧洲知名的半导体研发机构imec在其世界首个5nm芯片流片过程中只用Cadence的Innovus、Tempus和Virtuoso以及Mentor Graphics的Calibre,而根本不用Synopsys的ICC/ICC2和PrimeTime。在过去一年多里,Cadence的市场部门忙着对外宣称Innovus用新的Power Opt具备10-15%更好的PPA(Performance, Power, Area——性能、功耗、面积),用GigaPlace具备20%更好的布局QoR,还能与Virtuoso深度挂钩设计A/D芯片,诸如此类。还报道华为海思使用Innovus为其芯片减少了20%面积,东芝的芯片减少了16%面积并减少了25%功耗等等。Innovus目前已经可以用于10nm/7nm节点工艺。Innovus用户包括高通、英伟达、意法半导体、博通、华为海思、ARM、法拉第、NXP等。

Innovus-PVS用于signoff验收DRC/LVS、PERC、Innovus集成内全金属填充、DFM填充、全多重暴光颜色分解。与Virtuoso (IPVS)紧密集成。已取得台积电/联电/英特尔/GlobalFoundries的65nm至7nm节点工艺的认证。Innovus-PVS的基于track填充已经用于16/14/10nm节点工艺的生产。据称具备5至10倍快速ECO填充,4至5倍的快速全芯片填充。

-

Joules RTL Power Analysis: Joules 16.1 (JLS16.15.000-ISR5_Hotfix)

RTL功率分析工具Joules是RTL功率计算器。

-

Modus Test Solution: Modus 16.2 (MODUS16.20.000_Base)

Modus诊断与测试工具,可做扫描插入、压缩、ATPG、逻辑和存储器BIST、PMBIST。压缩比率达400倍。用户包括德州仪器、Microsemi、GlobalFoundries、Sequans等。Modus是Cadence试图冲击占据诊断测试这个小市场主导地位的Mentor Graphics的TestKompress。

-

Silicon Signoff and Verification (Tempus/Voltus IC): SSV 16.2 (SSV16.20.000_Base)

这个工具套件包括两个部分:Tempus Timing Signoff Solution和Voltus IC Power Integrity Solution。Tempus为芯片信号完整性(Signal Integrity)分析工具,Voltus为芯片电源完整性分析工具。

Tempus是与竞争对手Synopsys的PrimeTime竞争的产品。PrimeTime在STA(Static Timing Analysis)静态时序分析工具市场上占据垄断地位——差不多87%占有率。对5千万个晶体管的设计,PrimeTime在8个CPU上要花8.5小时,而Tempus在32个CPU上仅花费58分钟。Tempus能为20/16/14/10nm布局规则在MCMM时序优化中生成合法布局指令,能每小时处理1亿例晶体管,不需要布局工具来认可ECO。Tempus是业界首个全分布式大规模并行STA工具,已经在16/14/10nm工艺上得到认证,并且为7nm准备就绪。Tempus还能与Quantus QRC一起在Virtuoso环境内做静态时序分析。Tempus用户包括了高通、德州仪器、博通、意法半导体、NXP、ARM、夏普、LG这样的企业。

Voltus-DP是全芯片signoff验收工具。可做电压降、Power-Grid-Views、ECO。可在几百个CPU阵列(CPU Farm)上大规模并行处理十亿级晶体管。能与Cadence其他工具Tempus、Innovus协同运行以及Sigrity在芯片/封装/电路板协同进行联合设计运行。在两个用户做的benchmark基准测试中赢取主要竞争对手Ansys收购的Apache的RedHawk。Voltus的一个早期用户在其一个大型ARM芯片设计中将运行时间从9天减至1天。Voltus用户包括德州仪器、英伟达、意法半导体、华为海思、ARM、台积电、NXP、LGE、展迅等企业。

-

Stratus High-Level Synthesis: STRATUS 16.1 (STRATUS16.16.100_Update)

Stratus HLS是ASIC、SoC、FPGA设计的高层次综合平台。让用户能够从抽象的SystemC、C或C++模型中快速地设计和验证RTL实现,生成的Verilog RTL可以被Genus或者Synopsys的Design Compiler很容易地消化利用。能做控制逻辑和数据通道。通过与Innovus布局布线挂钩,Stratus HLS据说能够早在SystemC/C/C++原码中就能看到布局布线的拥挤阻塞问题。Cadence声称Stratus HLS比竞争对手Mentor Graphics的Catapult HLS有更高精确度。Stratus HLS的用户包括三星、LG、索尼、东芝、富士通、理光、Socionext、瑞昱半导体等公司。Stratus HLS原自Cadence收购的Forte设计系统公司。

数字芯片设计流程:

混合信号芯片设计流程:

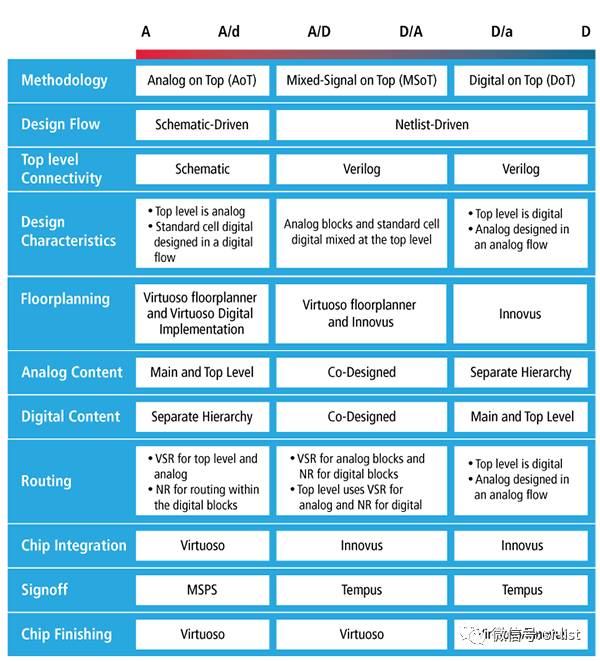

传统上混合信号芯片设计有两大方式:AoT和DoT。以模拟设计为主而集成少量到中等数量的数字逻辑时(即俗称的Big A,Little D——A/d),使用schematic驱动的AoT方式流程。以数字设计为主而引进模拟/混合信号IP时(即俗称的Big D,Little A——D/a),使用netlist驱动的DoT方式流程。

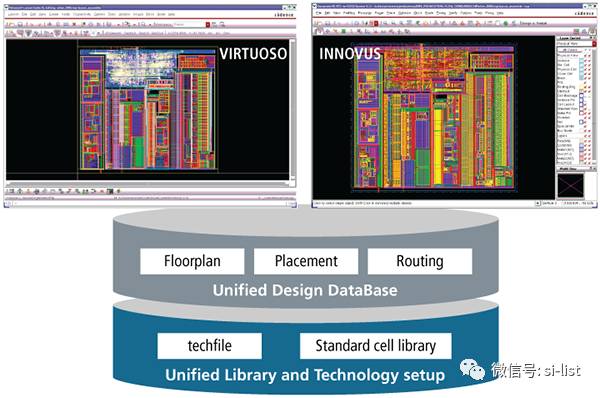

Cadence针对混合信号芯片设计引进了一种先进的联合设计(Co-Design)方式:MSoT,通过OpenAccess(OA)数据库将Virtuoso平台与Innovus平台对接在一起,帮助模拟设计团队和数字设计团队有效地实现复杂的混合信号芯片设计。

其他EDA厂商都在模仿Cadence这种思路,但它们的EDA产品都还没有达到Cadence在混合信号芯片设计EDA市场上的所拥有的程度。

Functional Verification数字芯片设计的功能验证

-

Indago Debug Platform. INDAGO 2016.11 (INDAGOMAIN2016.11.001_Base)

Indago排错调式平台从Cadence工具运行的logs中挖掘数据,将大数据捕获加入到根源分析中,以突出产生原先出错的因果关系和相关性。其理念是挖掘数据以尽量少做重复仿真。其竞争对手是市场领先的Synopsys的Verdi3。Indago用户包括IBM、HP、博通、英特尔、LSI、高通、Marvell、三星、日立等。

-

JasperGold Apps: JASPERGOLD 16.0 (JASPERGOLD16.12.000-INCISIVE1520_Base)

JasperGold是形式验证工具市场上占据支配地位的明星产品,在第三方用户调查中被评为形式验证工具的第一名:“JasperGold是所有形式验证工具(包括Cadence的IFV、Synopsys的VCS Formal和Mentor Graphics的Questa Formal等)中具备最佳运行时间和容量的一个”,“JasperGold的Visualize debug是同类中之最”....。JasperGold现在有13个应用Apps。JasperGold 2016版比JasperGold 2015版在性能上又有了很大的提升。JasperGold用户包括高通、德州仪器、博通、Marvell、ADI、英伟达、意法半导体、三星、索尼等知名企业。这工具原自Cadence于2014年收购进的Jasper Design Automation。Jasper的CEO为Kathryn Kranen,是EDA业界的一个传奇女性。她两次领导两个EDA创业企业取得成功,将新型验证技术引入EDA产业界,一次是Verisity, Ltd的验证自动化方案,包括Specman Elite testbench,另一个就是这个Jasper的形式验证的先驱技术。而且最后这两家公司都被Cadence收购了。

-

Metric-Driven Verification: MDV 20161.11 (MDVMAIN2016.11.003_Hotfix)

这个工具是原来Incisive中的验证规划和管理工具vManager和IMC,现在独立出来单独发行。

-

RocketSim Parallel Simulation Engine: RockSim 16.1 (ROCKSIM02.00.021_Update)

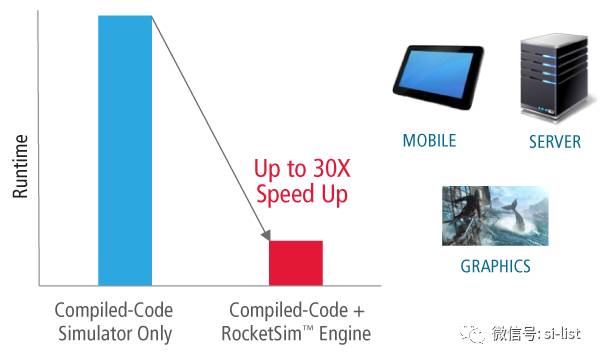

这是Cadence去年(2016)收购的以色列创业企业Rocketick的新型验证仿真加速引擎,以色列的这伙EDA研发人员花了9年时间搞出了这个多线程并行仿真工具。这是当前Verilog RTL仿真器市场上领先的明星产品。它的benchmark基准测试比Cadence的Incisive、Synopsys的VCS以及Mentor Graphics的Questa快了23倍。能够做门仿真和RTL仿真。能在2小时内编译10亿个门。全System Verilog并加速SVA。RocketSim通过PLI接口接入Cadence的Incisive、Synopsys的VCS以及Mentor Graphics的Questa进行验证仿真。

本来在Cadence、Synopsys和Mentor Graphics内部也都有多线程并行研发项目超过6年以上,但它们都没有鼓捣出什么结果。唯一另一个工具是Mentor Graphics于2013年收购了Axiom,但也没有奏效,Axiom只在某些设计上有用,其他设计都于太多事件而被压垮了。所以Cadence最后索性收购了这家以色列EDA公司,将这RocketSim超级仿真加速器纳入自己的囊中。而Synopsys则还在继续搞它的Cheetah VCS,但按照它自己的估计也还要2年以上才能搞出来。而且这Cheetah VCS还要用Nvidia英伟达的GPU特殊硬件,而不是像RocketSim那样使用x86_64的通用CPU,这对许多用户应用来说也是个妨碍。

逻辑仿真已经经过了两代:第一代是演绎仿真(interpreted simulation),第二代是编译仿真(compiled simulation)。现在到了第三代:并行仿真(parallel simulation)。而Rocketick就是在并行仿真上突破了关键技术。

-

Verification IP: VIPCAT 11.3 (VIPCAT11.30.045_Update)

验证使用的各种IP,包括收购的Denali的VIP,收购的Verisity的Specman "e" VIP。VIP包括AMBA 5 CHI,eMMC 5.0,HDMI 2.0,LPDDR4,MIPI C-PHY,MIPI CSI-3,MIPI SoundWire,Mobile PCI Express,PCI Express Gen 4,USB SuperSpeed Inter-Chip,Wide I/O 2,Ethernet 25G/50G,HBM,HMC,MIPI DSI-2,WiFi MAC。VIPCAT用户包括高通、博通、HP、IBM、英特尔、LSI、Marvell、三星、日立等企业。其竞争对手Mentor Graphics的Questa Verification IP在用户调查中处于遥遥领先地位。

-

Xcelium Verification Platform: XCELIUM 2016.11 (XCELIUMMAIN2016.11.001_Base)

这是Cadence将Incisive的C原码与RocketSim的C原码整合起来重新编写成为GNU C++的全新版验证平台,用来替代原来的Incisive验证平台。这个全新版验证平台由于具备了RocketSim上面所介绍的验证加速特性,验证性能有了飞跃性进步。现在5千万门(Little Boy小孩级别)可综合System Verilog RTL的设计,Xcelium在8核Linux机器上运行比Incisive在单核Linux机器上运行快4倍。而对于4亿门(Fat Man胖子级别)的设计,Xcelium在6核机器上运行要比Incisive快9.3倍。也就是说,具备测试台激励最大活跃度的设计的规模越大,Xcelium的加速性能也越大。当4亿门胖子做高活跃度DFT(Design For Test可测试设计)门级仿真时,Xcelium要快30倍!此外由于集成为一体,所以RocketSim在Xcelium中绕过了原先Incisive需要PLI接入这个瓶颈。

Incisive的各个程序指令在当前Xcelium版本中还能兼容继续使用,但在未来Xcelium升级版中将逐步被淘汰。Xcelium(以及Indago和MDV)现在分为Main Release主发布版和Agile Release灵活发布版。Agile版每月或更短时间进行升级以更快地改进工具(bug fixings等),而Main主发布版则要更长时间升级。

数字芯片设计及验证流程:

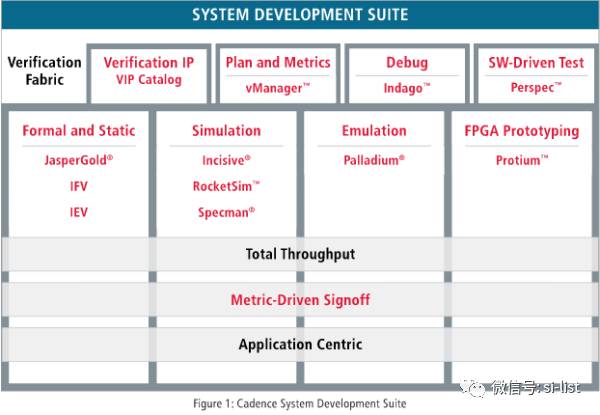

Cadence的数字系统验证开发组合套件功能分布图,这里图示了个各部分功能所使用的工具。例如仿真工具包括了Incisive(现在为Xcelium),RocektSim,Specman这些仿真工具,而形式与静态验证工具则包括了JasperGold,IFV(Incisive Formal Verification),IEV(Incisive Enterprise Verifier)这些验证工具,等等:

Silicon-Package-Board Co-Design芯片-封装-电路板联合设计

-

Allegro ECAD-MCAD Library Creator: SPBS 17.2 (SPBS17.21.000_Base)

ECAD-MCAD(电子CAD-机械CAD)单元库的制作工具,用于ECAD-MCAD联合设计。

-

Allegro Sigrity: SIGRITY 2017 (SIG17.00.000_Base)

Allegro信号完整性/电源完整性(SI/PI)工具,是高速PCB电路板和IC集成电路封装的分析工具,对芯片/封装/电路板进行信号和电源完整性进行分析。这工具原自Cadence收购的Sigrity。

-

OpenPOWER Compliance Kits in Sigrity2017: (SIG17.00.000-MODEL_OpenPOWER_Library)

这是Sigrity的Model Library中的分离出来单独包装的(因为其超过1.2GB),安装只需将其直接放进Sigrity的Library目录。

-

Silicon-Package-Board Co-Design: SPB 17.2 (SPB17.20.009_Hotfix)

正如名称所示,SPB是芯片/封装/电路板的联合设计工具套件,而不仅仅是Allegro PCB电路板的设计工具。许多人将这个工具仅作为PCB电路板设计工具,只用到了其中的一部分功能。例如芯片设计企业可以利用其中的封装设计工具SiP(System in Package)将不同材料或不同工艺制程的芯片封装成为一个芯片。比如说将不同材料设计的射频芯片(例如高性能GaN材料设计的功率放大器PA)与CMOS数字芯片封装成一个芯片。

SPB的OrbitIO工具:芯片/封装/电路板通过OrbitIO互联设计工具进行联合设计。

Verification Accelerator and Emulator验证加速器及模拟器

-

Memory Model Portfolio: MMP 16.1 (MMP16.10.000_Base)

-

Palladium Applications: PDAPP 16.1 (PDAPP16.10.000_Base)

-

Protium Rapid Prototyping Platform. Protium 16.1 (PTM16.10.000_Base)

-

Palladium XP (Unified Xccelerator Emulator): UXE 15.1 (UXE15.10.000_Base)

-

Palladium Z1 (Verification Xccelerator Emulator): VXE 16.1 (VXE16.10.000_Base)

此大类EDA是Cadence针对Incisive验证的硬件加速系统,用户需要购买Cadence的Palladium硬件加速系统,分别是Palladium XP系统和Palladium Z1系统,以及FPGA原型开发卡用于上面列出的Protium快速原型开发平台。整个系统相当于Cadence特制的服务器系统,对于大多数中小芯片设计企业来说其成本过于高昂,不值得投资,故在此不做更多介绍。

再来说一下EDA工具培训。EDA工具的培训对芯片设计企业来说是非常重要的一环,许多中小型企业往往忽视对设计人员做必要的EDA工具培训,让设计人员即刻上岗从事芯片等设计工作。这往往会与企业预期相反,造成设计项目的延误等事倍功半的反效果,形成投入产出的损失。EDA工具培训的最佳手段是使用EDA厂商原始官方的全套培训素材,例如EDA厂商的培训视频、培训实验课件RAKs(Rapid Adoption Kits)等,如此能加快受培训人员对EDA工具的融入和掌握,提升设计效率。毕竟EDA原本就是为了提升设计的效率而产生和发展的。此外Cadence还提供其专有的SKILL程序的各种scripts供用户在其各种EDA工具中使用。