Verilog - 笔试题(2)

1.下面哪个是可以用verilog语言进行描述,而不能用VHDL语言进行描述的级别?(A)

(A) 开关级 (B)门电路级 (C) 体系结构级 (D) 寄存器传输级

设计范围方面,Verilog HDL和VHDL语言有一个显著的区别:Verilog HDL可以描述系统级(System)、算法级(Algorithm)、寄存器传输级(RTL)、门级(Gate)和开关级(Switch)电路,而VHDL则不具备开关级电路描述能力。

3.下列哪些Verilog的基本门级元件是多输出(D)

(A) nand (B) nor (C) and (D) not

not U1(out1, out2, in);

缓冲门、非门都可以有多个输出,而且这些输出值都是相同的。

4.Verilog连线类型的驱动强度说明被省略时,则默认的输出驱动强度为(B)

(A) supply (B) strong (C) pull (D) weak

If drive strength is not specified, it shall default to (strong1, strong0).

assign (supply1, weak0) a = 1; 输出supply的1,weak的0。

5.元件实例语句“notif1 #(1:3:4,2:3:4,1:2:4) U1(out,in,ctrl);”中截止延迟的典型值为(B)

(A) 1 (B) 2 (C) 3 (D) 4

上升延迟:信号由0XZ变化到1时受到的门传输延迟。

下降延迟:信号由1XZ变化到0时受到的门传输延迟。

截止延迟:信号由01X变化到Z时受到的门传输延迟。

notif1 #(10,20,30) U3(out,in,ctrl); 分别为上升延迟,下降延迟,截止延迟

and #(4:5:6) U1(out,i1,i2); 分别为最小值,典型值,最大值(上升下降截止延迟同为4:5:6)

and #(2:3:4,3:4:5,4:5:6) U3(out,i1,i2);

7.根据调用子模块的不同抽象级别,模块的结构描述可以分为(ABC)

(A) 模块级 (B)门级 (C) 开关级 (D) 寄存器级

8.在verilog语言中,a=4b'1011,那么&a=(D)

(A) 4b'1011 (B) 4b'1111 (C) 1b'1 (D) 1b'0

归约运算符,从右向左依次运算

1.Verilog HDL语言进行电路设计方法有哪几种 ?

1.自上而下的设计方法(Top-Down)

2.自下而上的设计方法(Bottom-Up)

3.综合设计的方法,将上述两种方法结合,高层系统设计时采用Top-Down设计方法,便于系统划分,底层设计时采用Bottom-Up设计方法。

2.specparam语句和parameter语句在参数说明方面不同之处是什么?

1.specparam语句只能在延时说明块(specify块)中出现,而parameter语句则不能在延时说明块内出现

2.由specparam语句定义的参数只能是延时参数,而由parameter语句定义的参数则可以是任何数据类型的参数

3.由specparam语句定义的延时参数只能在延时说明块内使用,而由parameter语句定义的参数则可以在模块内(该parameter语句之后)的任何位置使用

1. 根据下面的程序,画出产生的信号波形

module test;

reg a, b;

initial begin

a = 0; b = 1;

#10 a = 1;

fork

b = 0;

#10 b = 1;

#20 a = 0;

join

#10 b = 0;

#10 a = 1;

b = 1;

end

endmodule

2. 根据下面的程序,画出产生的信号波形

module test;

reg dout;

initial begin

dout = 0;

#1 dout = 1;

#2 dout = 0;

#3 dout = 1;

#4 dout = 0;

end

endmodule

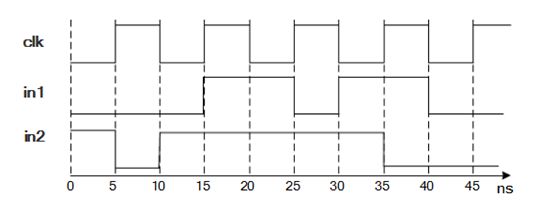

1. 用verilog语言产生如下图所示的测试信号

module test;

reg clk,in1,in2;

initial begin

clk = 0;

forever #5 clk = ~clk;

end

initial begin

in1 = 0;

#15 in1 = 1;

#10 in1 = 0;

#5 in1 = 1;

#10 in1 = 0;

end

initial begin

in2 = 1;

#5 in2 = 0;

#5 in2 = 1;

#25 in2 = 0;

end

endmodule

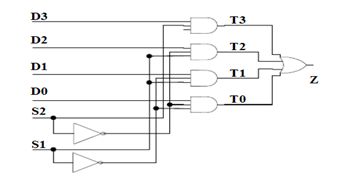

2.用verilog语言,利用内置基本门级元件,采用结构描述方式生成如图所示的电路

module a(

input D3,D2,D1,D0,S2,S1,

output Z

);

wire W2,W1,T3,T2,T1,T0;

not U1(W2,S2),

U2(W1,S1);

and U3(T3,D3,S2),

U4(T2,D2,W2,S1),

U5(T1,D1,W1,S1),

U6(T0,D0,W2,W1);

or U7(Z,T3,T2,T1,T0);

endmodule

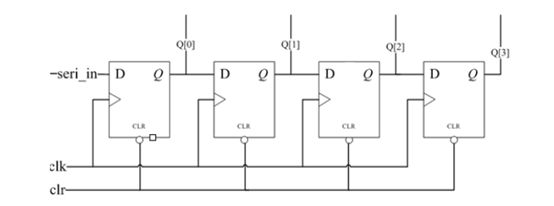

3. 用verilog语言描述:图示为一个4位移位寄存器,是由四个D触发器(分别设为U1,U2,U3,U4)构成的。其中seri_in是这个移位寄存器的串行输入;clk为时钟;clr为清零控制信号输入;Q[0]~Q[3]则为移位寄存器的并行输出。

module a(

input seri_in,clk,clr,

output reg [3:0] Q

);

always @(posedge clk or negedge clr) begin

if(!clr)

Q <= 4'b0000;

else

Q[3:0] <= {Q[2:0],seri_in};

end

endmodule

4.用verilog语言描述:有一个输入序列,位宽1bit,长度为16,每个时钟沿向左移一位,每当检测到输入序列为5的倍数时dout输出1.

这里只需关注余数,可以在每个周期检测序列除以5的余数是否为0

S0:余数为0;

S1:余数为1;

S2:余数为2;

S3:余数为3;

S4:余数为4;

module seqdet(

input clk,

input rst_n,

input din,

output reg dout

);

reg [2:0] state_c;

reg [2:0] state_n;

parameter S0 = 3'd0,

S1 = 3'd1,

S2 = 3'd2,

S3 = 3'd3,

S4 = 3'd4;

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)begin

state_c <= s0;

end

else begin

state_c <= state_n;

end

end

always @ (*) begin

case(state_c)

S0: if(din == 0)begin

state_n = S0;

end

else begin

state_n = S1;

end

S1: state_n = din ? S3 : S2;

S2: state_n = din ? S0 : S4;

S3: state_n = din ? S2 : S1;

S4: state_n = din ? S4 : S3;

default: state_n = S0;

endcase

end

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)begin

dout <= 1'b0;

end

else if(state_n == S0 && state_c != S0) begin

dout <= 1'b1;

end

else begin

dout <= 1'b0;

end

end

endmodule