【微机原理】一篇文章弄懂存储器子系统ram芯片地址范围计算

众所周知(并没有) ram芯片的寻址范围与译码器有关,这里使用两个题目来简要讲解2-4译码器和3-8译码器的存储器子系统中ram芯片地址范围的计算。

不想看解析只想看答案的同学,答案在最下方 还是看一下解析吧毕竟 我写得这么辛苦 会了解析 就啥情况都会了鸭 你说是吧ヾ(◍°∇°◍)ノ゙

前导

地址范围的计算永远看地址线,永远看地址线,永远看地址线。

这个芯片的地址范围计算跟CPU寻址范围计算不同的地方在于,有几根高位地址线可能是用于选择哪一组的(控制片选),而不是直接拿所有的n根地址线计算 2 n 2^n 2n 作为与地址范围

具体哪几根控制片选,由译码器决定

题目一:2-4译码器

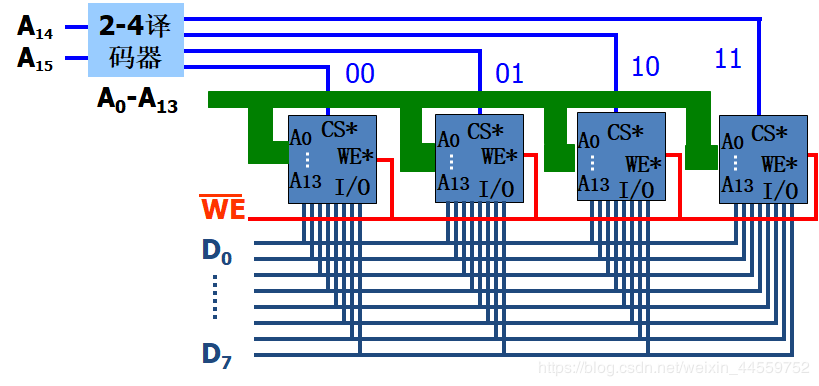

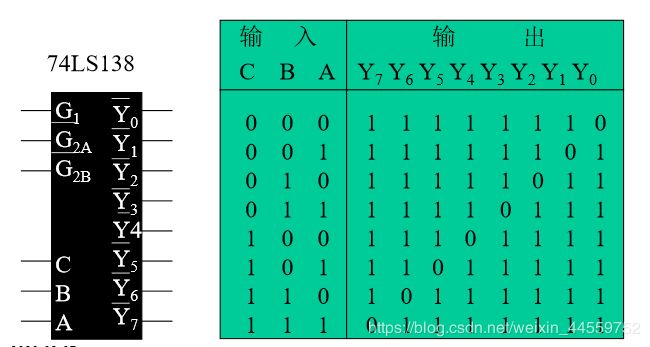

有一存储器子系统连接图如图1所示,系统有16条地址线A15-A0,使用2-4译码器,写出每个存储器的地址范围:(使用16进制表示)

解析

如图所示,一共0~15 16根地址线,即其本身寻址范围是 2 16 2^{16} 216 。

接下来分别计算每个芯片的寻址范围。

2-4译码器用A15、A14两个引脚来控制芯片的选择。如上图标示,从左到右的四个芯片分别于 A14=0,A15=0;A14=0,A15=1;A14=1,A15=0;A14=1,A15=1 这四种情况被选上(A11往前都是直接控制地址的,省略不写)

| 芯片组 | A 14 A 15 A_{14} A_{15} A14A15 |

|---|---|

| 第一片 | 0 0 |

| 第二片 | 0 1 |

| 第三片 | 1 0 |

| 第四片 | 1 1 |

那么剩下的14根地址线全为1的时候,就是每个芯片可寻址的空间大小啦: 11 , 1111 , 1111 , 1111 B 11,1111,1111,1111B 11,1111,1111,1111B = 3FFF H H H

已知了每个芯片的可寻址范围,又:首地址为所有地址线均为0即0,所以第一片芯片的寻址范围是:0000 H H H ~3FFF H H H。往后的每一个芯片,只要在其基础上增加3FFF H H H 就可以啦

那么就可以写出四个芯片的寻址范围了:

| 芯片 | A 14 A 15 A_{14} A_{15} A14A15 | 寻址范围 |

|---|---|---|

| 第一片 | 0 0 | 0000 H H H ~3FFF H H H |

| 第二片 | 0 1 | 4000 H H H ~7FFF H H H |

| 第三片 | 1 0 | 8000 H H H ~BFFF H H H |

| 第四片 | 1 1 | C000 H H H ~FFFF H H H |

注意每片的寻址范围是闭区间,所以进入下一片的时候地址还要额外+1哦(即第二片的寻址范围是从4000 H H H开始),以及16进制加法8000 H H H +4000 H H H = C000 H H H。

题目二 3-8译码器

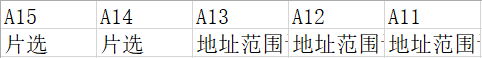

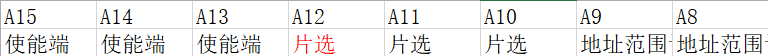

存储器系统连接如下图,使用74LS138,请分别写出图中四组芯片的地址分配范围。

解析

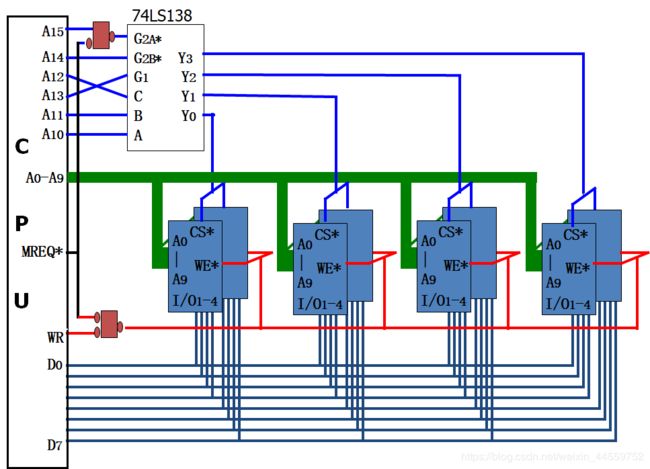

首先我们来看一下3-8译码器,重点关注跟2-4译码器不一样的地方:三个使能端。

这三个使能端的含义是,三个G全有效的时候,数字电路的真值表(绿表)才成立,才能够激活ABC三者组合控制Y0到Y7的作用。注意 G 1 G_{1} G1是正逻辑, G 2 A G_{2A} G2A和 G 2 B G_{2B} G2B是负逻辑(即要让三者全有效, G 1 G_1 G1的输入应为1,而 G 2 A G_{2A} G2A和 G 2 B G_{2B} G2B的输入应为0)

了解了3-8译码器,看这个题就很容易了。首先我们使用ABC来控制Yn实现片选。所以必须保证三个使能端全部有效(值全为1)。即: A 15 A_{15} A15=1, A 14 A_{14} A14=0, A 13 A_{13} A13=1

注意上面 A 15 A_{15} A15连接的 G 2 A G_{2A} G2A虽然是负逻辑,理应输入0,但 G 2 A G_{2A} G2A前面有一个负逻辑连线(那个小圈圈),所以负负得正啦!

确定了前面三条地址线的取值,接下来看连接ABC的 A 10 A_{10} A10、 A 11 A_{11} A11和 A 12 A_{12} A12。跟上面的2-4译码器相同,这三条地址线控制的是片选。也就是右边四组存储器。三条线可以控制 2 3 2^3 23 = 8 组,但我们只有四组,所以 A 12 A_{12} A12这条地址线的输入应该恒为0。

至此确认最高位4位恒定的取值:(0101)

剩下两条 A 10 A_{10} A10、 A 11 A_{11} A11就跟上题的 A 14 A_{14} A14、 A 15 A_{15} A15一样,二者的组合控制四组芯片

| 芯片组 | A 10 A 11 A_{10} A_{11} A10A11 |

|---|---|

| 第一组 | 0 0 |

| 第二组 | 0 1 |

| 第三组 | 1 0 |

| 第四组 | 1 1 |

那么剩下的12根地址线全为1的时候,就是每个芯片可寻址的空间大小啦: 1111 , 1111 , 1111 B 1111,1111,1111B 1111,1111,1111B = 03FF H H H

又:首地址为 1010 , 0000 , 0000 , 0000 B 1010,0000,0000,0000B 1010,0000,0000,0000B = A000 H H H 所以第一片芯片的寻址范围是:A000 H H H ~A3FF H H H。往后的每一个芯片在其基础上增加03FF H H H

那么就可以写出四个芯片的寻址范围了:

| 芯片组 | A 10 A 11 A_{10} A_{11} A10A11 | 寻址范围 |

|---|---|---|

| 第一组 | 0 0 | A000 H H H ~A3FF H H H |

| 第二组 | 0 1 | A400 H H H ~A7FF H H H |

| 第三组 | 1 0 | A800 H H H ~ABFF H H H |

| 第四组 | 1 1 | AC00 H H H ~AFFF H H H |

同上题每片的寻址范围是闭区间,所以进入下一片的时候地址还要额外+1哦(即第二片的寻址范围是从A400 H H H开始)

答案

第一题

0000 H H H ~3FFF H H H

4000 H H H ~7FFF H H H

8000 H H H ~BFFF H H H

C000 H H H ~FFFF H H H

第二题

A000 H H H ~A3FF H H H

A400 H H H ~A7FF H H H

A800 H H H ~ABFF H H H

AC00 H H H ~AFFF H H H