第2章 PCI总线的桥和配置

2.1 存储器域和PCI总线域

1)每个桥和设备都有配置空间,由HOST主桥管理

2)处理器包括多个CPU,外部cache,中断控制器,DRAM控制器

x86中,PCI总线统一管理全部外部设备

3)PCI总线地址空间在初始化时映射成为存储器域的存储地址

如32位的PCI总线中,每一个总线域的地址范围都是0x0000 0000 ~ 0xFFFF FFFF

2.2 HOST主桥

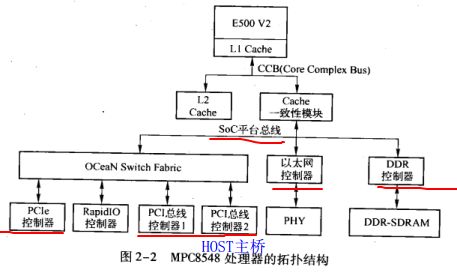

1)PowerPC MPC8548处理器

AMBA: ARM中典型的soc平台总线

RapidIO总线是用于解决背板互连的外部总线

2) 配置空间的访问

用ID号寻址,ID号包括:总线号,设备号,功能号

总线号由系统软件决定,与主桥相连的PCI总线编号为0

设备号由设备的IDSEL信号与总线地址线的连接关系确定;

功能号与设备的具体设计相关,大多只有一个功能设备

a. 内部寄存器 存放在BASE_ADDR为起始地址的“1MB的物理地址空间”中,通过BASE_ADDR+ 0x8000即为CFG_ADDR

CFG_ADDR 保存ID号和寄存器号,要访问配置空间时,需先设置该寄存器

CFG_DATA是大端,PCI设备的 配置寄存器 采用小端编址

b. 存储器地址转换为PCI地址 outbound

ATMU寄存器组包括outbound和inbound寄存器组

3)x86的HOST主桥

x86有两个I/O端口寄存器,分别为CONFIG_ADDRSS和CONFIG_DATA,0xCF8和0xCFC

x86处理器采用小端地址模式,南北桥升级为MCH和ICH,MCH基础存储器控制器、显卡芯片、HOST-to-PCIe主桥

ICH包括LPC、IDE、USB总线;而最新的nehalem I7中,MCH一分为二,存储控制器和图形控制器与CPU内核集成,剩下与ICH合并为PCH

2.3 桥和设备的配置空间

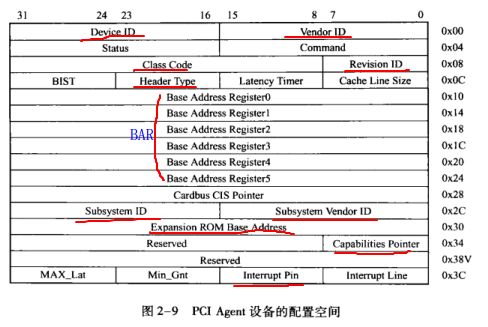

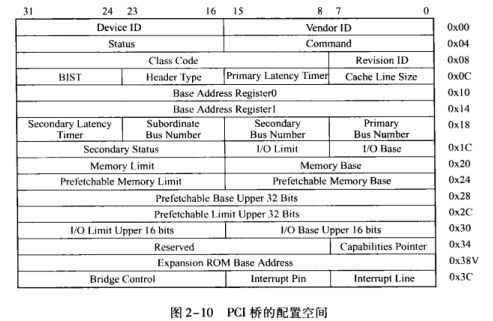

1)三种类型的配置空间:PCI agent, PCI桥, cardbus桥片

PCI桥不需要驱动来设置,被称为透明桥,还有种非透明的PCI桥

PCI设备将配置信息存放在E2PROM中,上电初始化时,把E2PROM读到配置空间中作为初始值,由硬件逻辑完成;然后系统会根据DFS算法初始化配置空间。

2)PCI agent配置

vendor id , 生产厂商, intel是0x8086, 0xffff无效

device id, 具体设备, 这两个是由PCISIG 分配的。

revision id, 版本号

class code, PCI设备的分类, 包括base class code (显卡、网卡、PCI桥等), sub class code, interface

header type, 区分 PCI Agent、 桥、 cardbus

Expansion ROM base address , 有些设备需要在操作系统运行前完成初始化,如显卡,键盘,硬盘,这个PCI设备需要运行ROM的地址

capabilities pointer, capabilities组的基地址,存放扩展配置信息,PCI可选,PCI-X和PCIE设备必须支持

interrupt line , PCI设备使用的中断向量号, 驱动得到后,注册ISR到OS

只对8259A中断控制器有效,多数处理器没有用这个

interrupt pin, 使用的中断引脚,1表示INTA#

base address register 0~5, BAR 保存基地址, linux用pci_resource_start读,ioremap物理地址转为逻辑地址,直接读BAR不对(得到PCI物理地址)

command, 命令寄存器,设置才能访问IO和存储

status, 得到设备状态

letency timer, 控制PCI设备占用总线的时间

3) 桥的配置空间

(待续)

2.4 PCI总线的配置

1) 两种配置请求: type 00, type 01, 穿桥只能01

2)系统软件用DFS初始化bus号,device号

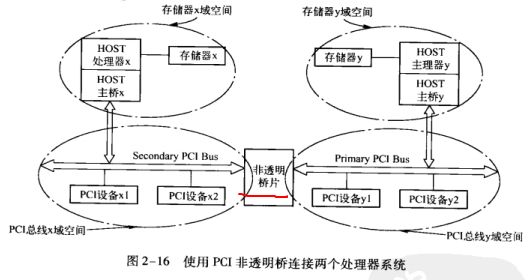

2.5 非透明桥

1)可以方便的连接两个处理器系统(不是cpu),对PCI总线x域和y域进行隔离,但不隔离存储器域空间

第3章 PCI总线的数据交换

3.1 BAR空间的初始化

1)系统使用DFS遍历PCI总线时会初始化BAR等寄存器,然后就可以进行数据传递

2)powerPC中通过inbound和outbound实现两域之间的转换;x86没有这个机制,而是直接相等,但还是是不同域的地址

3.2 设备的数据传递

3.3 与cache相关的事务

1)powerPC 设置inbound来设置是否进行cache一致性操作

x86使用MTRR寄存器设置

(cache好复杂,待续)

3.4 预读机制

1)使用预读机制降低了cache行失效带来的影响,有 指令预读、数据预读、外部设备的预读队列、操作系统的预读策略

指令预读:CPU根据程序的执行情况,提前把指令从主存预读到指令cache中