SPI总线 verilog代码

SPI总线的构成及信号类型

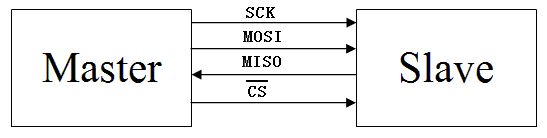

SPI总线只需四条线(如图1所示)就可以完成MCU与各种外围器件的通讯:

1)MOSI – Master数据输出,Slave数据输入

2)MISO – Master数据输入,Slave数据输出

3)SCK – 时钟信号,由Master产生

4)/CS – Slave使能信号,由Master控制。

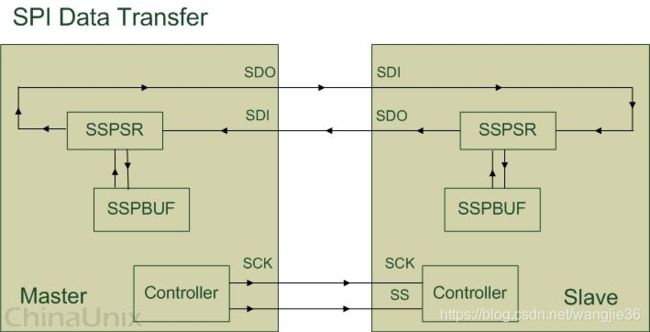

在一个SPI时钟周期内,会完成如下操作:

1) Master通过MOSI线发送1位数据,同时Slave通过MOSI线读取这1位数据

2) Slave通过MISO线发送1位数据,同时Master通过MISO线读取这1位数据

Master和Slave各有一个移位寄存器,如图4所示,而且这两个移位寄存器连接成环状。依照SCK的变化,数据以MSB first的方式依次移出Master寄存器和Slave寄存器,并且依次移入Slave寄存器和Master寄存器。当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。Master和Slave各有一个移位寄存器,如图4所示,而且这两个移位寄存器连接成环状。依照SCK的变化,数据以MSB first

module spi(rst,clk, spics,spiclk,spido);

input rst;//置位信号,低有效,复位要用计数器来产生,在FPGA里面产生

input clk;//时钟信号

output spics;//SPI片选信号,对于SPI来说是输出,对于FPGA来说是输入

output spiclk;//SPI时钟信号,对于SPI来说是输出,对于FPGA来说是输入

output spido;//SPI数据输出信号,对于SPI来说是输出,对于FPGA来说是输入

module top(clk,spics,spiclk,spido,LDET,led);

input clk;//时钟信号

output spics;//SPI片选信号

output spiclk;//SPI时钟信号

output spido;//SPI数据输出信号

input LDET;//是由SPI输入进来的寄存器配置信号,为1则说明已经配置好了

output led;//从FPGA右边输出出去

reg [4:0]cnt;//用于产生rst的计数器

reg rst;//置位信号,低有效

wire led;//链接出去的,但又不是内部输入输出。

spi spi(//例化的是SPI,和前面的那个模块要一模一样

.clk(clk),.rst(rst),.spiclk(spiclk),.spics(spics),.spido(spido));

always@(posedge clk)

begin

if(cnt==5'd01) rst<=1'b1;

else begin rst<=1'b0; cnt<=cnt+1'b1; end

end

assign led=LDET;//通过FPGA,将左边由SPI输入的LDET传给右边输出给led作为灯的信号

endmodule