【Verilog HDL 训练】第 03 天

阅读某工艺库:http://bbs.eetop.cn/thread-611701-1-1.html

第一次见这种东西,只能尝试摸索下,待修正!

大神答案:https://t.zsxq.com/JaqzjqR

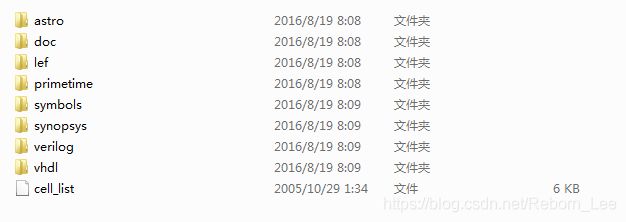

1. 了解目录结构:与前端相关的比如文档(doc),仿真模型(verilog/vhdl),标准单元库(synopsys/symbols)

1. 了解目录结构:与前端相关的比如文档(doc),仿真模型(verilog/vhdl),标准单元库(synopsys/symbols)。这是针对s家的模型,如果使用c家的综合工具就不能用了,所以这个库不全。

参考地址:https://t.zsxq.com/JaqzjqR

每一个/aci路径下面包含了astro(),doc(文档资料),lef(),primetime(),symbols(标准单元库),synopsys(标准单元库),verilog(仿真模型),vhdl(仿真模型)等文件夹。

从:

到:

再到:

参考:这是地址

参考:这是地址

2. 阅读文档transition time, propagation delay等参数的定义

propagation delay:

The propagation delay through a cell is the sum of the intrinsic delay, the load-dependent delay, and the input-slew dependent delay. Delays are defined as the time interval between the input stimulus crossing 50% of Vdd and the output crossing 50% of Vdd.Figure 1 illustrates the propagation delay.

transition time:

The transition times (slews) on input and output pins are defined as the time interval between the signal crossing 10% of Vdd and 90% of Vdd. Figure 2 illustrates transition time measurements for rising and falling signals.

给出别人的答案:

transtion delay time, 分为rising time和falling time。rising time是指从10%的Vdd到90%的Vdd的时间,falling time是指从Vdd 90%到10%的时间。 propagation delay,顾名思义是传播延迟,就是输入的电平变到50%Vdd起开始计时,到输出电平变到50%Vdd为止所需要的时间。这些参数都在时序约束当中起到重要的作用。

链接:链接

3. 阅读文档Power Dissipation/Calculation的描述

描述过长,见具体文档!

4. 阅读文档Delay calculation的描述

同上!

5. 提供了哪些类型的cell?

包含的特殊标准单元有,Antenna-Fix Cell、NWELL and Substrate Tie Cell、Fill Cells、Low-Power (XL) Cells、TIEHI/LO Cells、Delay Cells

主要包含的基础基本标准单元有

全加器、与门、与或门、BUF、D触发器、延迟、反相器、选择器、与非门、或非门、三态门、异或门、同或门等等。

参考:Verilog没有葵花宝典打卡day3

6. Verilog文件中包含了哪些信息?

cell的功能模型还有时序检查 specify

https://t.zsxq.com/JaqzjqR