Avalon总线基础介绍(数据手册版)之Avalon-MM接口

文章目录

- Avalon-MM接口

- Avalon-MM接口介绍

- Avalon-MM接口信号描述

- adress

- byteenable or byteenable_n

- read or read_n

- readdata

- response

- write or write_n

- writedata

- waitrequest or waitrequest_n

- readdatavalid or readdatavalid_n

- writeresponsevalid

- burstcount

- beginbursttransfer

- 传输(Transfers)类型介绍

- Transfer的概念说明

- 典型的读写传输

- 带有Waitrequest的读写传输

- 使用waitrequestAllowance属性的传输

- 具有固定等待状态的读取和写入传输

- 流水线传输(Pipelined Transfer)

- 具有可变延迟的流水线读取传输

- 具有固定延迟的流水线读取传输

- 突发传输(Burst Transfers)

- 读响应与写响应(Read and Write Responses)

- Avalon-MM读写响应(主控和从属)的事务处理顺序

- Avalon-MM读写响应时序图

- 具有readdatavalid或writeresponsevalid的minimumResponseLatency时序图

- 地址对齐

- Avalon-MM从站寻址

- 参考资料

Avalon-MM接口

Avalon-MM接口介绍

您可以使用Avalon内存映射(Avalon-MM)接口为主组件(components)和从属组件实现读写接口。

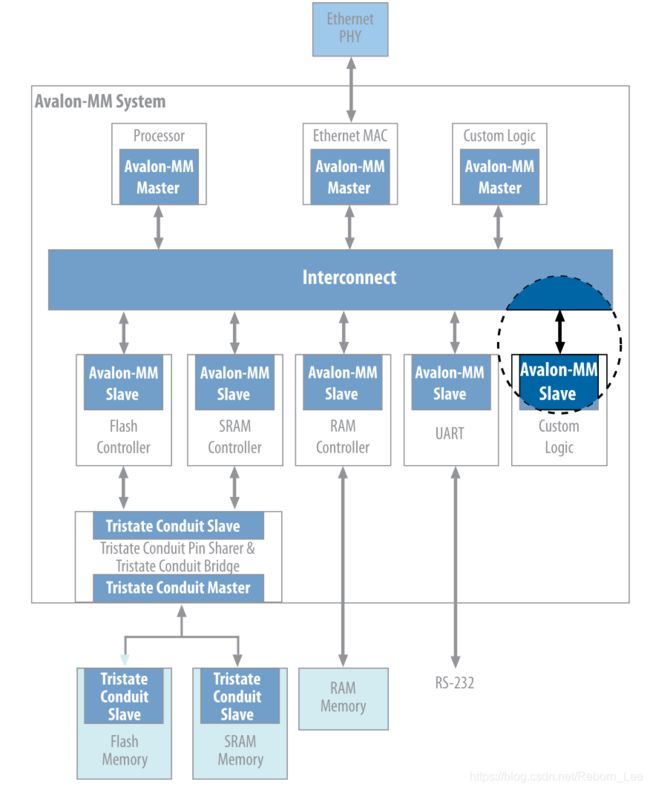

先给出一个Avalon接口的典型系统,显示了Avalon-MM slave 接口的连接:

Avalon-MM组件通常仅包含组件逻辑所需的信号。

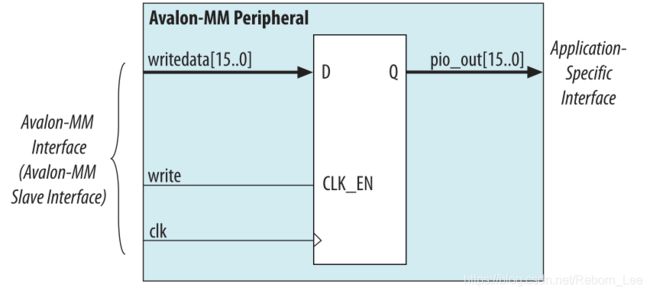

下图所示的16位通用I / O外设仅响应写请求。该组件仅包括写传输所需的从信号。

Avalon-MM从站中的每个信号都恰好对应一个Avalon-MM信号角色。

Avalon-MM接口信号描述

信号角色定义了Avalon-MM主端口和从端口允许的信号类型。本规范并不要求Avalon-MM接口中存在所有信号。始终没有一个信号是必需的。 Avalon-MM接口的最低要求是read-only接口的readdata,或write-only接口中的writedata和write。

下面是一些接口角色的信息,重点关注方向以及功能:

注:一些信号可以是高有效也可以是低有效,在命名上会有标识,如果是低有效,则存在后缀-n

adress

方向

Master -> Slave

描述

该信号宽度从1到64之间;

Master:默认情况下,地址信号表示一个字节地址。地址值必须与数据宽度对齐。为了写入数据字中的特定字节,主机必须使用byteenable信号。

Slave:默认情况下,互连结构(interconnect)将字节地址转换为Slave地址空间中的字地址。从Slave的角度来看,每个Slave访问都是一个数据字。例如,address = 0选择Slave的第一个字。 address = 1选择Slave的第二个字。

byteenable or byteenable_n

方向

Master -> Slave

描述

byteenable信号的位宽可以是2,4,8,16,32,64,以及128位。

在宽度大于8位的数据接口上进行传输时启用一个或多个特定字节通道。 byteenable中的每个位对应于writedata和readdata中的一个字节。byteenable信号中的第n个bit指示数据中的第n个字节是否正在被写或者被读。在写的过程中,byteenable指定要写入的字节,其他字节应该被Slave忽视;同理,在读的过程中,byteenable指定Master正在读哪个字节。

read or read_n

方向

Master -> Slave

描述

该信号位宽为1;

该信号如果存在,则必须与readdata同在;其有效,则表示正在进行读过程。(类似于读使能)

readdata

方向

Slave →Master

描述

该信号位宽可以为8, 16,32,64,128,256,512,1024;

对应于byteenable信号的位宽2,4,8,16,32,64,以及128位。

该信号响应read信号,与read信号同在,其作为对read信号的响应,从slave中返回读取的数据。

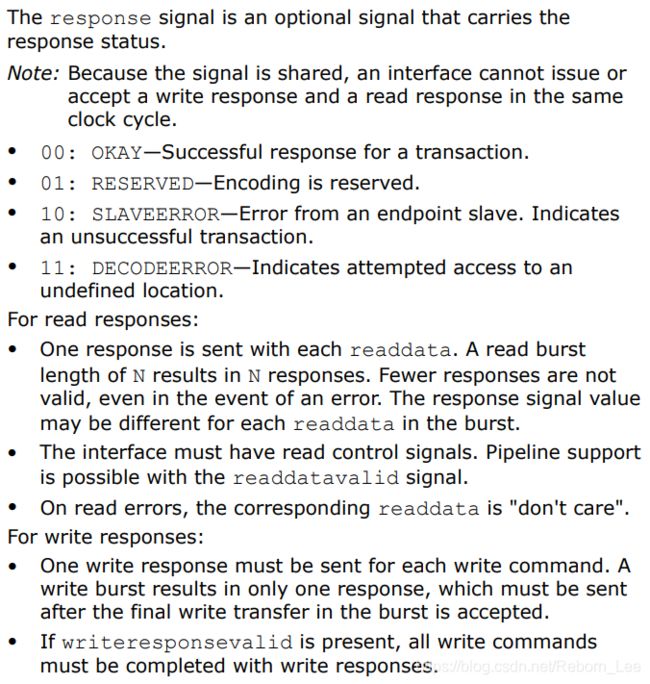

response

方向

Slave →Master

描述

该信号位宽为2位;

response信号是一个可选的信号,它携带响应状态。

其值的含义如下:

- 00: OKAY --表示对传输的成功响应;

- 01: RESERVED – 编码保留;

- 10: SLAVEERROR – 来自于终端Slave的一个错误。表明一个不成功的传输过程。

- 11: DECODEERROR – 表明尝试访问一个未定义的位置。

write or write_n

方向

Master →Slave

描述

该信号位宽为1,类似有上面的read;如果该信号为1,也即有效,则表明正在进行写传输过程,此信号与writedata同在。

writedata

方向

Master →Slave

描述

同理于readdata,该信号位宽可以为8, 16,32,64,128,256,512,1024;

如果存在readdata信号,则writedata信号的宽度必须与readdata一致;

该信号与write信号同在。

waitrequest or waitrequest_n

方向

Slave →Master

描述

该信号是Slave发出到Master的,表示当Slave无法响应Master的read或者write请求时,可以使该信号有效。强迫Master等待直到互联结构(Interconnect)准备好进行数据传输。在传输的开始,Master初始化传输并等待直到waitrequest信号无效。

简单说来就是该信号有效的时候,即使read或者write信号有效,也要停止读或者写,等待该信号无效为止。

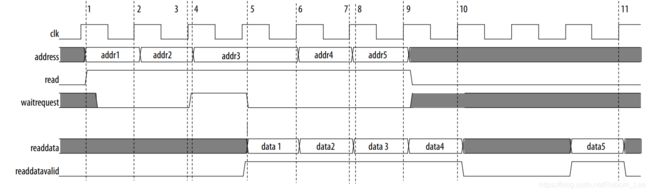

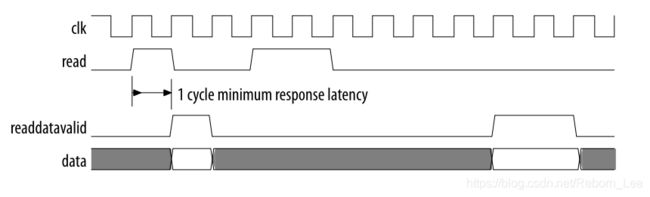

readdatavalid or readdatavalid_n

方向

Slave →Master

描述

用于可变延迟的流水线式读传输。当有效时,表示readdata信号包含有效数据。

对于burstcount值的读突发(read burst),readdatavalid信号必须被置为有效次,每个readdata项有效一次。read有效与readdatavalid有效之间必须有至少一个周期的延迟,也就是说read有效后必须至少延迟一个时钟才能读取数据readdata,关于说明readdatavalid信号的时序图,请参考Pipelined Read Transfer with Variable Latency。

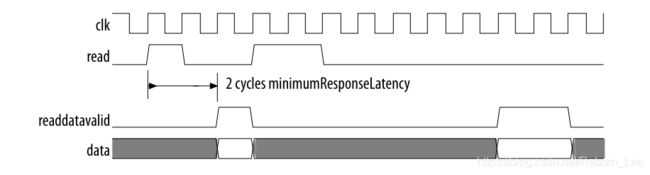

注意,信号readdatavalid与waitrequest相互独立,也就是说,Slave令readdatavalid有效以告诉Master读取数据readdata有效,但readdatavalid信号与waitrequest信号没有什么必然的关系,waitrequest信号有效可以照常执行其功能,即令Master读取或者写数据等待,readdatavalid信号有效则读取信号有效。如下图外套request的灰色部分与readdatavalid的关系:

readdatavalid是无所谓waitrequest的值的,只要我有效,便有数据输出。

如果master支持流水线读,则此信号为必须存在的。

writeresponsevalid

方向

Slave →Master

描述

可选信号。接口(如果存在)发出对写命令的写响应。置位后,响应信号上的值是有效的写响应。仅在接受写命令后的一个时钟周期或更长时间才声明Writeresponsevalid。从接受命令到置位writersponsevalid,至少有一个时钟周期的延迟。

burstcount

方向

Master →Slave

描述

位宽为1到11;

由突发主机(burst master)使用,以指示每个突发中的传输次数(即一次连续传输多少个数据,写或者读多少个数据);其值必须为2的幂次。

宽度为n的突发计数(burstcount)接口可以编码大小为2^(n-1)次的最大突发。例如,一个4位的突发计数(burstcount)信号可以支持最大突发计数8(2^3)。

最小突发计数为1。constantBurstBehavior属性控制突发计数信号的时序。具有读取功能的突发主机必须包含readdatavalid信号。对于使用字节地址突发的主机和从机,以下限制适用于地址的宽度:

<address_w> >=

<burstcount_w> +

log2(<symbols_per_word_of_interface>)

对于使用字地址突发的主机和从机,将省略上面的log2项。

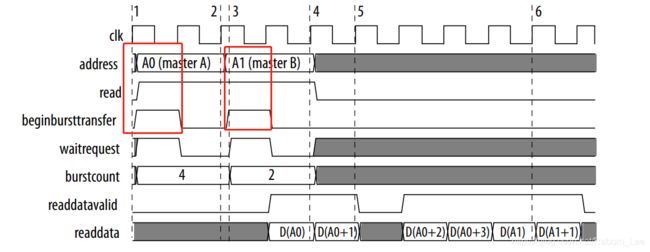

beginbursttransfer

方向

Interconnect → Slave

描述

在一次突发传输的第一个时钟周期有效表明该次突发传输的开始。不管waitrequest信号值为多少,该信号在一个周期后置为无效。

A0为一次突发传输的开始地址,A1为另一次突发传输的开始地址,且无论waitrequest是否有效,即使有效,也在一个时钟周期之后无效(不会因为waitrequest信号置位而在多持续一个时钟)。

beginbursttransfer是可选的。从机始终可以通过对数据传输计数来内部计算下一个写突发事务的开始。

警告:请勿使用此信号。存在此信号以支持旧版内存控制器。

传输(Transfers)类型介绍

Transfer的概念说明

上面在介绍avalon总线接口的时候遇到过很多次(每次)传输的说法,其实它是对transfer的直译,在介绍传输类型之前,有必要对transfer或者传输这个概念进行进一步说明:

- 传输是对一个字或一个或多个数据符号的读或写操作。传输发生在Avalon-MM接口和互连(interconnect)之间。

传输需要一个或多个时钟周期才能完成。

主设备(master)和从设备(Slave)都是传输(Transfer)的一部分。Avalon-MM Master发起传输,Avalon-MM Slave做出响应。 - 主从对(Master-Slave pair)-该术语是指传输中涉及的主接口和从接口。在传输过程中,主接口控制和数据信号通过互连结构并与从接口交互。

典型的读写传输

本节介绍一个典型的Avalon-MM接口,它支持使用从设备(Slave)控制的waitrequest进行读写传输。

带有Waitrequest的读写传输

从设备(Slave)可以通过置位waitrequest信号在所需的周期内停滞互连(也就是让读写都处于等待状态)。

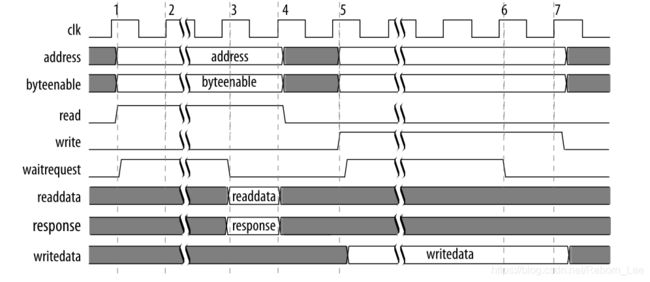

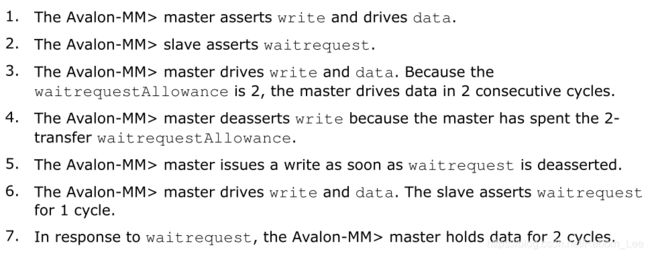

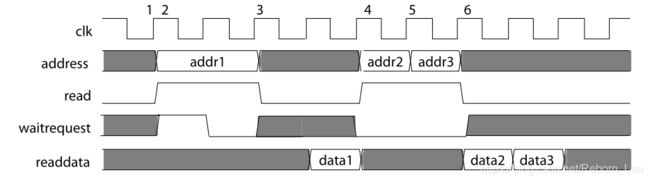

下图是具有Wait request的读写传输情况:

该时序图中的数字标记了以下转换:

- address,byteenable,read在clk的上升沿之后有效。Slave置位waitrequest,停止传输。

- waitrequest被采样,因为waitrequest信号有效,该周期仍为等待状态,address,read,write和byteenable保持不变。

- 在该时钟上升沿waitrequest信号无效,Slave断言readdata和response(response和readdata有效)。

- Master采样readdata,response,和置位无效的waitrequest以完成传输;

- 该时钟上升沿后address,writedata,byteenable以及write信号被置为有效,从设备置位waitrequest信号以停止传输。

- 从设备仍断言waitrequest信号(即置位令其有效);

- 从设备捕获写数据以完成传输。

再次提醒:

waitrequest信号表示等待请求,即是否需要等待,如果为高,则表示需要等待,也就是当前时钟的读使能或者写使能无效,如果为低,则无需等待。

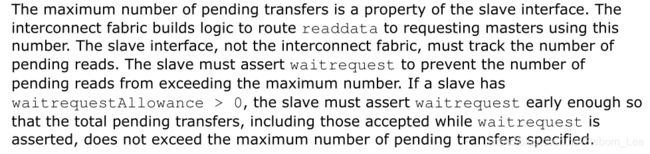

使用waitrequestAllowance属性的传输

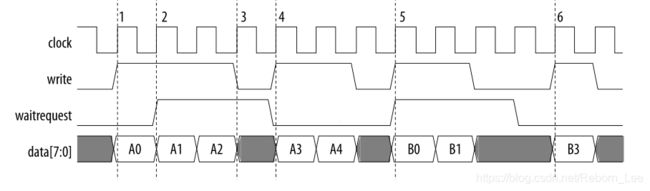

Master写:waitrequestAllowance等于两个时钟周期

这种情况是什么意思呢?

waitrequestAllowance=2,表明即使Slave置位waitrequest令其有效,Master仍然可以写两个时钟周期的数据:

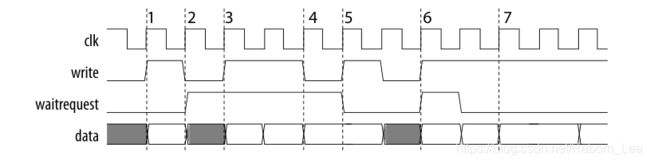

如下是其时序图:

可见,在第二个时钟的上升沿waitrequest为1,但是仍然可以进行两个时钟的写数据;

在标号为5的时钟上升沿时刻write信号有效,但此时waitrequest也有效,但是仍然可以写两个时钟的数据。

我想此时应该明白waitrequestAllowance=2的意思了吧。

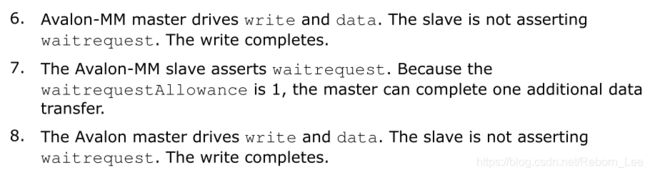

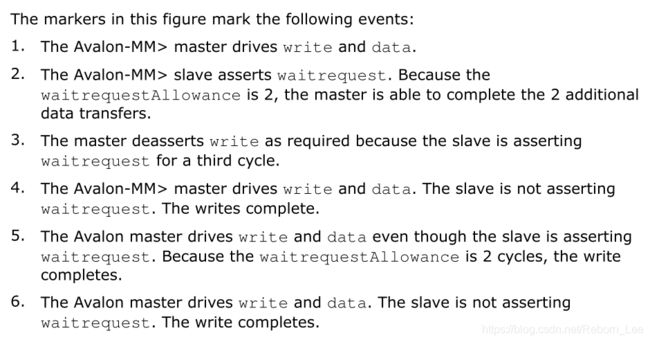

对于上述时序图的解读,我就不会细读了,下面是数据手册提供的原文:

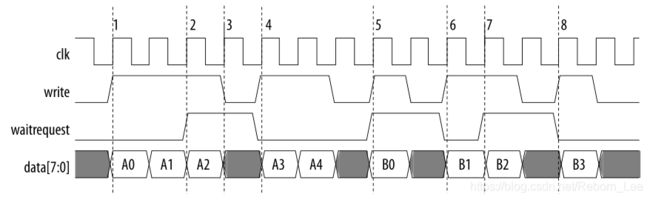

Master写:waitrequestAllowance等于一个时钟周期

标号为2的时钟上升沿,即使waitrequest为1,仍然进行一次写数据;

同理,标号为5也是如此,标号为7也是如此。

注意:

下图说明了Avalon-MM>主设备的时序,该主设备可以在断言waitrequest后发送两次传输。此时序是合法的,但不建议这样做。在此示例中,主设备对事务数进行计数,而不是时钟周期数。这种方法需要一个计数器,该计数器会使实现更加复杂并可能影响时序收敛。当主机通过waitrequest信号和恒定的周期数确定何时驱动事务时,主机将根据注册的信号启动或停止事务。

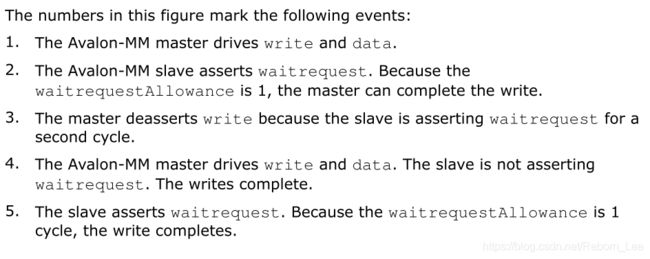

图中的数字表示以下事件:

注:必须注意的是,数字7处的事件是怎么回事?必须有这个响应?

具有固定等待状态的读取和写入传输

Slave可以使用readWaitTime和writeWaitTime属性指定固定的等待状态。使用固定的等待状态是使用waitrequest停止传输的一种替代方法。在传输过程中,地址和控制信号(byteenable,read和write)保持恒定。将readWaitTime或writeWaitTime设置为n等效于在每次传输时断言n个周期的waitrequest。

下面的时序图以writeWaitTime=2和readWaitTime = 1为例:

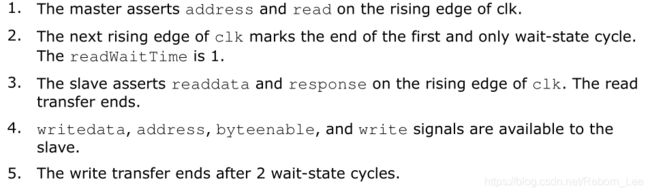

时序图中的数字表示如下的事件:

具有单个等待状态的传输通常用于多周期片外外围设备。外设在clk的上升沿捕获地址和控制信号。外设有一个完整的周期返回数据。

允许零等待状态的组件。但是,具有零等待状态的组件可能会降低可达到的频率。零等待状态要求组件在提出请求的同一周期内生成响应。

流水线传输(Pipelined Transfer)

Avalon-MM流水线读取传输提高了同步从设备的吞吐量,该同步从设备需要几个周期才能返回首次访问的数据。此后,此类设备通常每个周期可以返回一个数据值一段时间。新的流水线读取传输可以在返回之前传输的readdata之前开始。

流水线读取传输具有地址阶段和数据阶段。主机通过在地址阶段显示地址来启动传输。从机通过在数据阶段传递数据来完成传输。新传输(或多次传输)的地址阶段可以在先前传输的数据阶段完成之前开始。该延迟称为流水线延迟。流水线等待时间是从地址阶段结束到数据阶段开始的持续时间。

等待状态和流水线延迟的传输时序具有以下主要差异:

-

等待状态-等待状态确定地址阶段的长度。等待状态限制了端口的最大吞吐量。如果从设备需要一个等待状态来响应传输请求,则该端口每次传输需要两个时钟周期

-

流水线延迟-流水线延迟确定了直到返回数据的时间,而与地址阶段无关。没有等待状态的流水线从站可以在每个周期维持一次传输。但是,从机可能需要数个等待时间周期才能返回第一数据单元。

可以同时支持等待状态和流水线读取。流水线延迟可以是固定的,也可以是可变的。

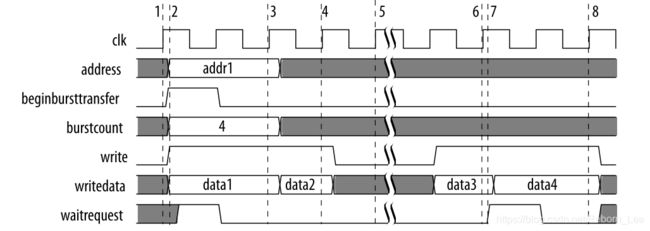

具有可变延迟的流水线读取传输

捕获地址和控制信号后,Avalon-MM流水线从站需要一个或多个周期来产生数据。流水线从机在任何给定时间可能有多个挂起的读取传输。

可变延迟流水线读取传输:

- 需要一个附加信号readdatavalid,用于指示读取数据何时有效。

- 包括与非流水线读取传输相同的信号集。

在可变延迟流水线读取传输中,使用readdatavalid的从属外设被视为具有可变延迟流水线。与读命令相对应的readdata和readdatavalid信号最早可以在该读命令被声明之后的周期中被声明。

注:

从站必须以接受读取命令的相同顺序返回readdata。具有可变延迟的流水线从端口必须使用waitrequest。从站可以声明waitrequest以暂停传输,以保持可接受数量的挂起传输。从机可以断言readdatavalid以独立于从机是否使用waitrequest停止新命令而将数据传输到主机。

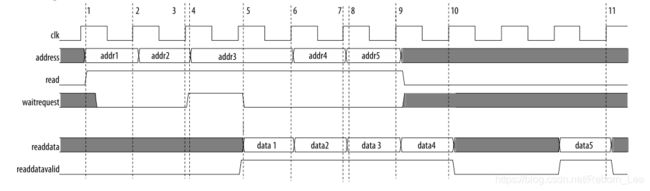

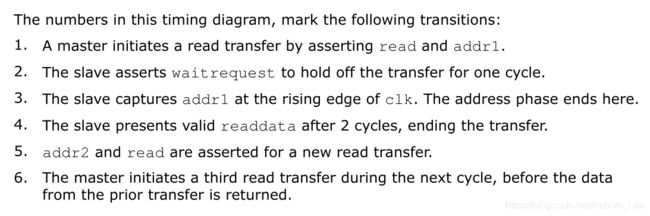

下图显示了几个从属读取传输。从站流水线具有可变的延迟。在此图中,从站最多可以接受两个挂起的传输。从站使用waitrequest来避免超过该最大值。

如果从设备在处理未决的读传输时无法处理写传输,则从设备必须声明waitrequest并停止写操作,直到未决的读传输完成为止。如果从机接受与当前暂挂的读传输相同地址的写传输,则Avalon-MM规范未定义readdata的值

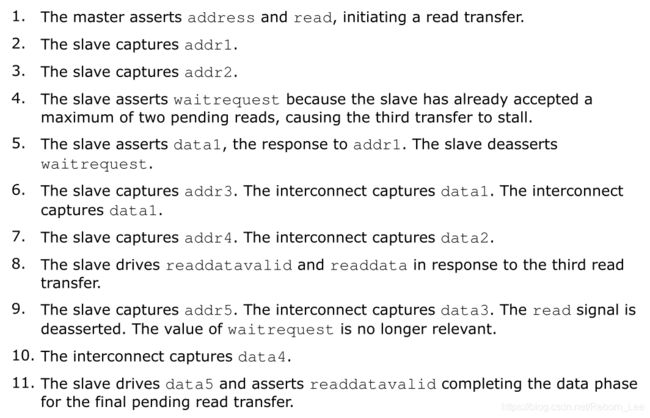

具有固定延迟的流水线读取传输

固定等待时间读取传输的地址阶段与可变等待时间情况相同。在地址阶段之后,具有固定读取延迟的流水线从机需要固定数量的时钟周期才能返回有效的读取数据。 readWaitTime属性指定返回有效readdata的时钟周期数。互连在适当的时钟上升沿捕获readdata,从而结束数据阶段。

下图显示了主机和流水线从机之间的多次数据传输。从属驱动器等待请求以停止传输。并具有2个周期的固定读取延迟。

解读原文:

突发传输(Burst Transfers)

突发将一个单元执行多次传输,而不是独立地对待每个单词。突发可能会增加从端口的吞吐量,而从端口在一次处理多个字时(例如SDRAM)可以实现更高的效率。突发的净效果是在突发期间锁定仲裁。同时支持读写的突发Avalon-MM接口必须同时支持读写突发。

突发Avalon-MM接口包括一个突发计数输出信号。如果从机具有突发计数输入,则该从机具有突发功能。

突发计数信号的行为如下:

- 在突发开始时,突发计数(burstcount)表示突发中顺序传输的次数。

- 对于突发计数宽度n,最大突发长度为

2^(n-1)。最小合法突发长度为1。

为了支持从设备读取突发,从设备还必须支持:

- 带有waitrequest信号的等待状态。

- 使用readdatavalid信号以可变延迟进行流水线传输。

在突发开始时,从机会在burstcount上看到地址和突发长度值。对于地址为且突发计数值为的突发,从站必须执行从地址开始的连续传输。从机接收(写入)或返回(读取)数据的字后,突发完成。突发从机必须为每个突发仅捕获一次地址和突发计数。从属逻辑必须为突发中除了第一个传输之外的所有传输推断地址。从机也可以使用输入信号beginbursttransfer,互连在每个突发的第一个周期将其置为有效。

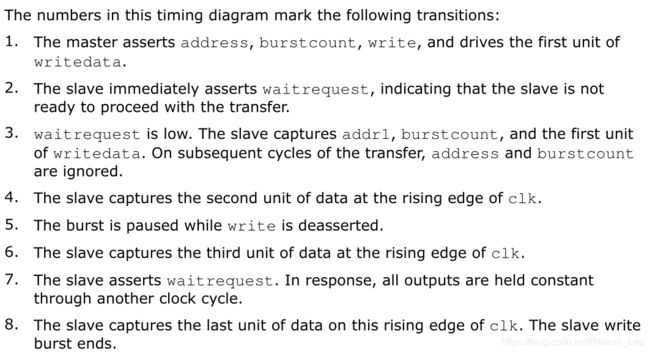

写突发

下图演示了长度为4的从设备写突发。在此示例中,从设备断言两次延迟等待请求的waitrequest。

在上图中,在突发的第一个时钟周期中声明了突发突发传输信号,并在下一个时钟周期中将其置为无效。即使从机声明了waitrequest,beginbursttransfer信号也仅在第一个时钟周期被声明。

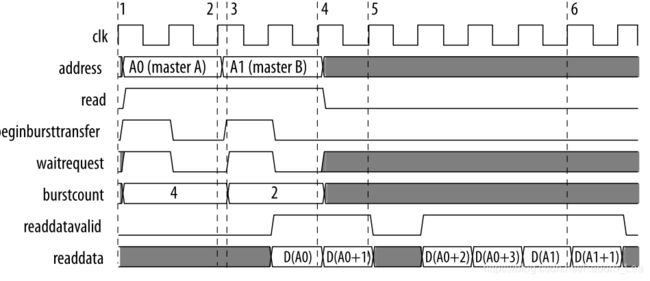

读突发

下图说明了一个具有两个突发主机访问一个从机的系统。请注意,主机B可以在为主机A返回数据之前驱动读取请求。

解读原文:

读响应与写响应(Read and Write Responses)

对于任何Avalon-MM从站,必须以无危险的方式处理命令。读写响应按接受命令的顺序发出。

Avalon-MM读写响应(主控和从属)的事务处理顺序

对于任何Avalon-MM主设备:

- Avalon接口规范保证到同一从设备的命令以命令发布顺序到达从设备,并且从设备以命令发布顺序响应。

- 不同的从机可能以与主机发出命令不同的顺序接收和响应命令。成功后,从站将按照命令发出顺序进行响应。

- 响应(如果存在)以命令发出顺序返回,而不管读或写命令是针对相同还是不同的从站。

- Avalon接口规范不能保证不同主机之间的事件顺序。

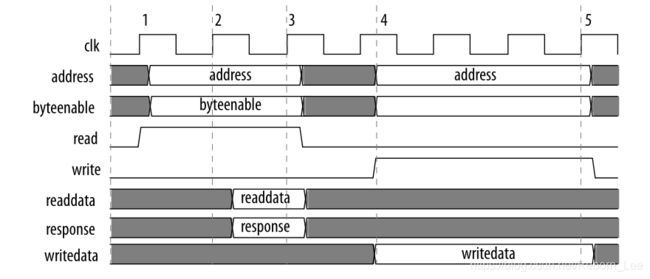

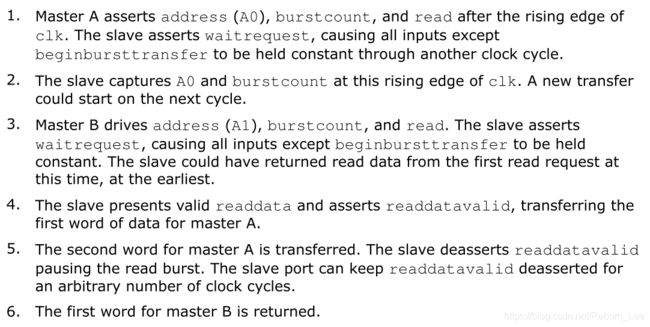

Avalon-MM读写响应时序图

下图显示了Avalon-MM读写响应的命令接受和命令发出顺序。因为读和写接口共享响应信号,所以接口不能在同一时钟周期内发出或接受写响应和读响应。

读取响应,为每个读取数据发送一个响应。 读取突发长度N有N个响应。

写响应,为每个写命令发送一个响应。写突发仅产生一个响应。从接口在接受突发中的最终写传输后发送响应。当接口包括writersponsevalid信号时,所有写命令都必须带有写响应。

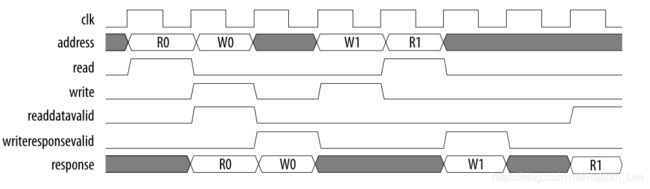

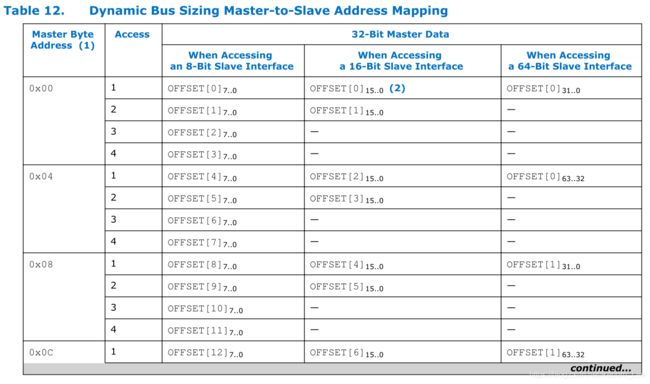

具有readdatavalid或writeresponsevalid的minimumResponseLatency时序图

minimumResponseLatency等于一个周期

minimumResponseLatency等于两个周期

Compatibility

具有相同minimumResponseLatency的接口无需任何调整即可互操作。如果主机具有比从机更高的minimateResponseLatency,请使用管道寄存器来补偿差异。流水线寄存器应延迟从机的读取数据。如果从属服务器具有比主服务器更高的minimumResponseLatency,则这些接口可以互操作而无需进行调整。

地址对齐

互联结构仅仅支持对齐的访问。Master只能以symbol的方式发布其数据宽度倍数的地址。(一个地址可能具有多个数据宽度的长度)

通过取消断言byteenable信号可以实现Master写部分字;例如,在地址2处写两个字节数据,可以令byteenable为4’b1100.

Avalon-MM从站寻址

动态总线大小可在数据宽度不同的主从对之间传输期间管理数据。

从站数据在主地址空间中以连续字节对齐。

如果主数据宽度大于从数据宽度,则主地址空间中的字会映射到从地址空间中的多个位置。例如,从16位从设备读取32位主设备将导致从设备侧进行两次读取传输。读取到连续地址。

如果主机比从机窄,则互连将管理从机字节通道。在主机读取传输期间,互连仅将适当的从机数据字节通道提供给较窄的主机。

在主写传输期间,互连自动声明可扩展信号以仅将数据写到指定的从字节通道。从站的数据宽度必须为8、16、32、64、128、256、512或1024位。

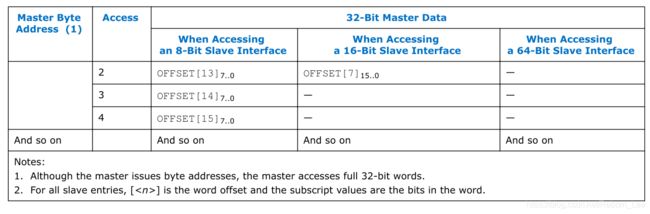

下表显示了执行全字访问的32位主机中各种宽度的从机数据的对齐方式。在此表中,OFFSET [N]表示从机字长偏移到从机地址空间的大小。

参考资料

- mnl_avalon_spec

- https://www.cnblogs.com/cofin/p/9972216.html