高速ADC时钟jitter对信噪比和有效位数的影响

高速ADC时钟jitter求解

高速ADC的时钟jitter会影响高速ADC的信噪比SNR,而信噪比决定了模拟前端输入的有效范围。所以需要先确定模拟前端的有效输入范围,然后确定应该满足的SNR,然后推导出时钟jitter。

一、模拟前端动态输入范围和有效位ENOB的关系

假设ADC的最大输入幅度是Vpp(单位V),分辨率位数N位,有效位数ENOB位。

有效位数ENOB是ADC的N位分辨率中实际有用的位数。N位ADC理论最小分辨率满足

然而如果ADC的噪声信号大于1LSB,则ADC采样信号的N位表示中并不是每一位都能表示采样信号,所以实际的分辨率位数会小于N,实际的分辨率位数我们称为有效位数ENOB。因此对于ADC来说,更加有效的参数是ENOB,而不是N,ADC实际的最小分辨率应该为:

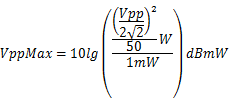

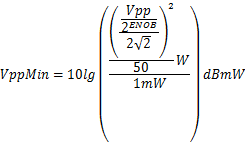

ADC的模拟输入动态范围为(VppMin,VppMax),VppMin和VppMax使用下面公式计算

模拟输入的幅度宽度:

VppMax-VppMin=6.02ENOB

二、有效位ENOB、信噪比SNR、信纳比SINAD,总谐波失真THD之间的关系

2.1、SNR

SNR的定义是信号幅度均方根与噪声幅度均方根的比值。假设信号幅度均方根是S,噪声均方根是N,则

2.3、SINAD

SINAD是信号幅度均方根与所有其它频谱成分(包括谐波但不含直流)的和方根的平均值之比。假设信号谐波幅度均方根是N,则

2.2、THD

THD指的是基波信号的均方根值与其谐波(一般仅前5次谐波比较重要)的和方根的平均值之比。假设2次、3次、4次以上的和谐波失真分别为HD2,HD3,HDn,总谐波失真是D,则THD可以用下面公式求解:

有些ADC的datasheet提供里THD的值,但是也有一些没有直接提供THD值得,没有提供THD值得可以使用HD2,HD3,HDn计算。

2.4ENOB、SNR、SINAD、THD之间的关系

信纳比和有效位数之间满足一个确定的关系:

因此我们可以根据所需要的ENOB来推导出ADC需要满足的SINAD的值。

由SINAD、THD和SNR的定义可以推导出如下公式:

THD是ADC可以通过ADC的datasheet直接查找到或者间接求出来,所以对于满足需求的SINAD,我们能够推导出来SNR应该满足的条件。

三、SNR求解

ADC的SNR主要由三部分引起:量化噪声,热噪声,抖动噪声。

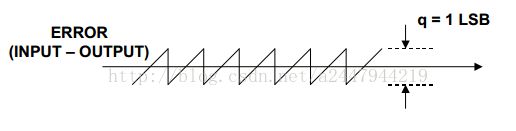

3.1、量化噪声

ADC对采样信号量化的时候,一定会产生一定的误差,从量化上来讲实际信号和量化后的信号之间的误差最大为0.5LSB。量化误差如下图所示:

量化误差引起的信噪比计算公式:

![]()

3.2、热噪声

热噪声是芯片固有的一个噪声,由采样缓存器噪声,采样切换阻抗等引起的,是一个定值,一般ADC都会给出热噪声的信噪比。如果没有给出可以使用下面公式计算:

NSD:noise spectral density or noise floordensity

3.3、抖动噪声

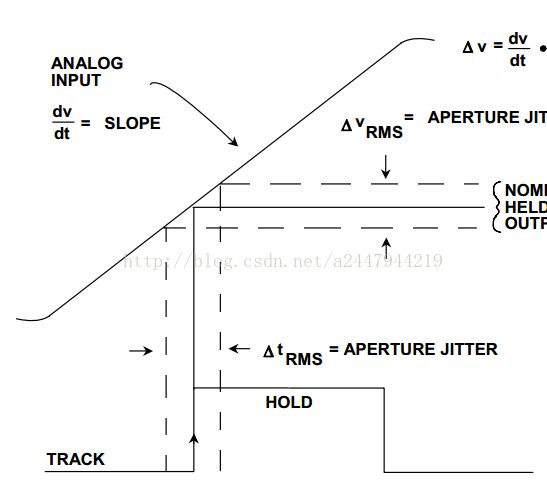

抖动噪声主要是由于时钟抖动和孔径抖动造成的。

上面两个图分别描述了时钟抖动和孔径抖动对采样点的影响,这两个抖动都会造成采样点的偏移,然而最后对数据处理的时候,会默认这些点都在理想位置采样的,在频域上会造成信号频率的弥散;另外一个理解方法是每一个采样点的实际采样值和理想采样值都有一定的偏差,相当于对每一个点都叠加了一个噪声。

时钟抖动引起的噪声的信噪比使用下面公式计算

从上面两个公式可以得出信噪比与采样时钟jitter成反比,与输入信号频率成反比,因此对于输入信号的频率越高,对时钟信号的jitter要求越严格。

3.4、总噪声

ADC总噪声是量化噪声,抖动噪声之和。量化噪声很多时候并不考虑,因为很多时候热噪声会远远大于量化噪声。当信号频率较低的时候,主要考虑热噪声,当信号频率较高的时候,才会考虑抖动噪声

ADC总信噪比用下面公式计算:

四、jitter求解实例

4.1、AD9680时钟jitter求解

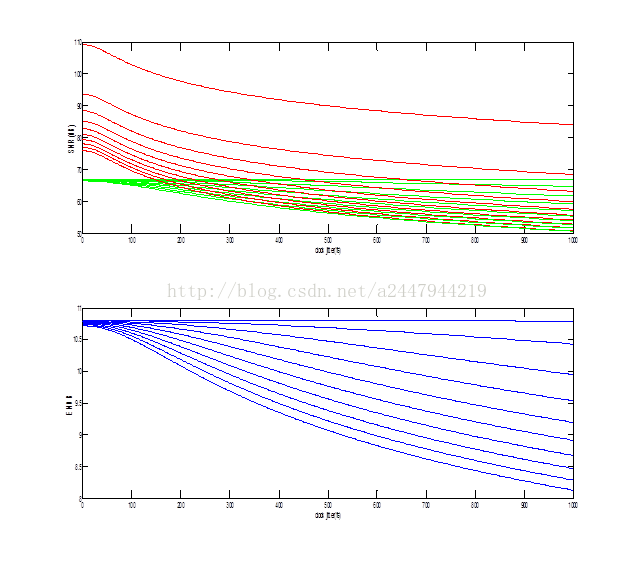

AD9680:14位分辨率位数,孔径抖动55fs,采样频率1GHz,THD值80dBFS,热噪声67dBFS,计算出来的jitter、SNR_jitter、SNR_ADC、fin、ENOB如下图:

第一幅图是jitter、fin、SNR之间的关系,红色代表SNR_jitter,绿色代表SNR_ADC,从上往下是不同fin对应的SNR,频率是从上依次1MHz,到501MHZ,步长50MHz。

第二幅图是jitter、fin、ENOB之间的关系,从上往下是不同fin对应的SNR,频率是从上依次1MHz,到501MHZ,步长50MHz。

从图中可以看出:fin越高,信噪比越大,ENOB越小,jitter越大,信噪比越大,ENOB越小。为了保证AD9680比较好的转换性能,最好使时钟jitter低于150fs,能够保证10位以上的有效位数。

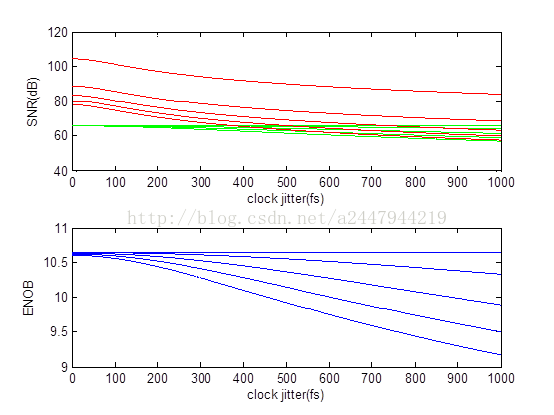

5.2、ADS54j54时钟jitter求解

ADS54j54:14位分辨率位数,孔径抖动98fs,采样频率500GHz,THD值80dBFS,热噪声66dBFS,计算出来的jitter、SNR_jitter、SNR_ADC、fin、ENOB如下图:第一幅图是jitter、fin、SNR之间的关系,红色代表SNR_jitter,绿色代表SNR_ADC,从上往下是不同fin对应的SNR,频率是从上依次1MHz,到251MHZ,步长50MHz。

第二幅图是jitter、fin、ENOB之间的关系,从上往下是不同fin对应的SNR,频率是从上依次1MHz,到251MHZ,步长50MHz。

4.3、ADS6445时钟jitter与AD9680时钟jitter比较

从两款芯片的jitter求解结果中能够发现,采样频率越高,信号频率越高的ADC对时钟jitter要求越严格。AD9680为了保证比较好的性能,需要小于150fs的jitter;AD54J54为了满足较好性能,需要小于300fs的jitter。

在翻阅不同ADC的datasheet,发现一个参数的规律,越是采样速度高的ADC,孔径抖动越小。这个参数是ADC本身固有的,是与芯片设计相关的。孔径抖动和时钟抖动同样的原理影响着ADC性能。为了更高的采样频率,芯片开发商会设计更小的孔径抖动,通过这个参数,我们也可以快速估算时钟抖动的大小。当时钟抖动小于孔径抖动的时候,能得到非常好的ADC性能,当两者相仿的时候,依然能保持很好的性能,当时钟抖动是孔径抖动的两三倍的时候,性能还比较好,当这个比例更大的时候,就需要参考采样信号的频率来具体分析。因此在设计ADC时钟的时候,可以将抖动粗略设为孔径抖动的两倍以内。