计算机组成原理---第四章 存储器(中)

存储器(中)

你做三四月的事,在八九月自有答案

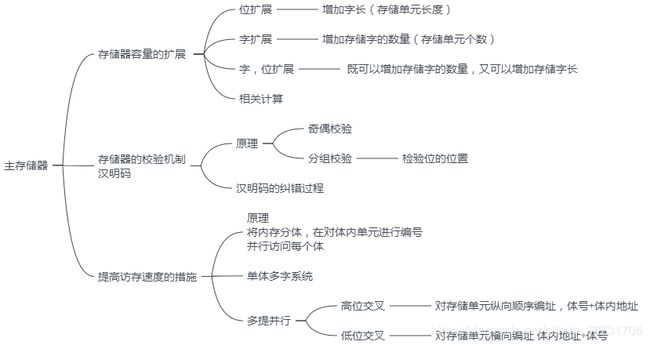

笔记框架:

- 4.2.4 只读存储器

- 4.2.5 存储器与 CPU 的连接

- 1.存储器容量的扩展

- 2.相关计算

- 4.2.6 存储器的校验

- 1.汉明码原理

- 2.汉明码的纠错过程

- 4.2.7 提高访问存储器的措施

- 1.单体多字

- 2.多体并行

4.2.4 只读存储器

只读存储器的种类

1.掩模 ROM

行列选择线交叉处有MOS管为 “1”

行列选择线交叉处无MOS管为“0”

MOS 管不可进行改变,只读

2.PROM

通过熔丝实现了一种一次性编程

熔丝断开为“0”

熔丝未断为“1”

是一种破坏性的编程,只读

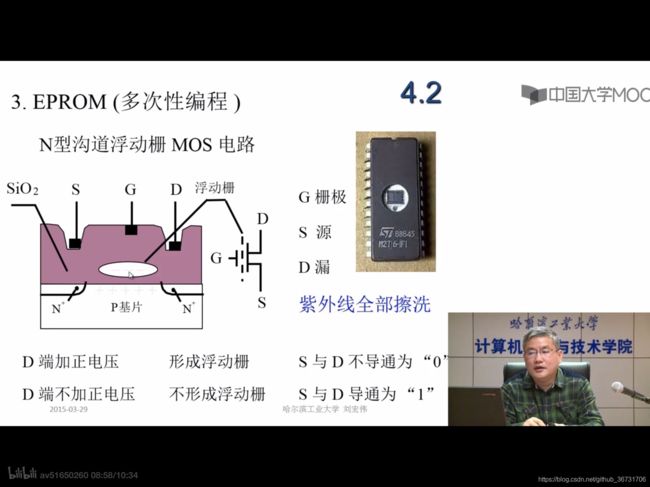

3.EPROM

4.2.5 存储器与 CPU 的连接

1.存储器容量的扩展

单片存储芯片的容量有限,很难满足实际要求,将若干个存储芯片连在一起才能组成更大容量

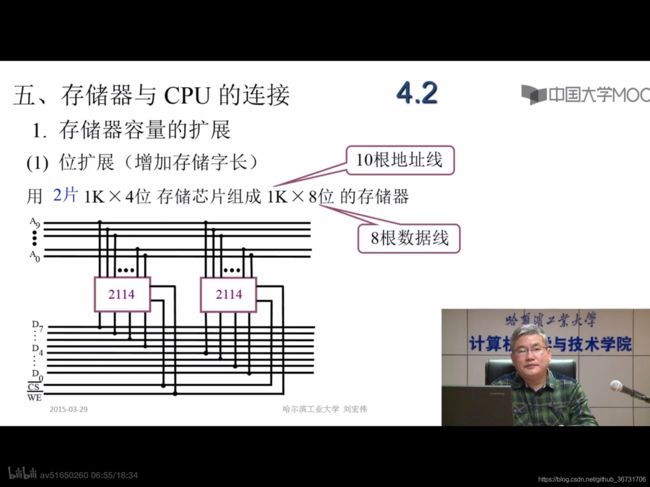

(1)位扩展

原理: 增加存储字长(增加存储单元大小)。上图为两个2114芯片,其大小为 1K x 4位,可以组成 2K x 8 位。其中每个芯片都连上10根地址线,但是数据线各自连不同的 10根。两个芯片片选线接在一起,可同时进行操作

原理: 增加存储器字的数量(存储单元个数)例如将两个 1Kx8位的芯片组成一个2Kx8(11根地址线)位的芯片。数据线同时连在两个内存上。如果 A10=0,选择第一个芯片,A10=1选择第二个芯片。

第一个存储空间:00000000000~ 0111111111

第二个存储空间:10000000000~11111111111

与字扩展不同,位扩展时不可同时连通

(3)字,位扩展

原理: 既可以增加存储字的数量,又可以增加存储字长。假设想要 4K x 8位(12根地址线,8根数据线,共 32K)的存储器,每个芯片为 1K x 4位,可算出一共需要8个芯片(共 32K)。两个芯片为一组,犹字扩展连接在数据线上。A10,A11作为片选:00选择第一组芯片,01选择第二组芯片,10选择第三组芯片,11选择第四组芯片

000000000000 ~ 001111111111 第一组

010000000000 ~ 011111111111 第二组

100000000000 ~101111111111 第三组

110000000000 ~ 111111111111第四组

2.存储器 CPU 的连接及相关计算

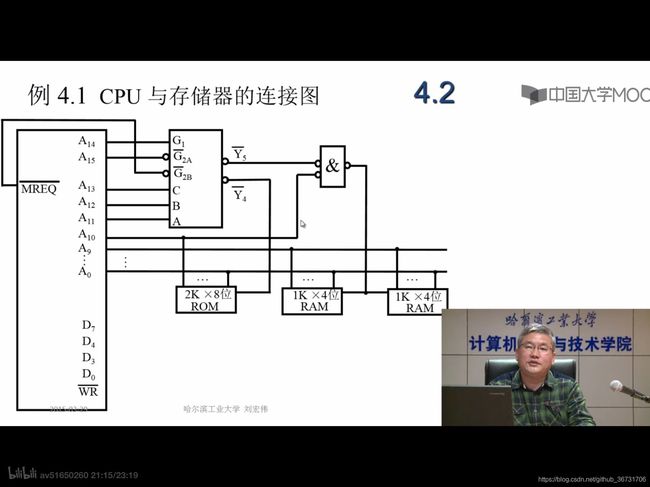

设CPU共有16根地址线,8根数据线,并用MREQ(低电平有效)作访存控制信号,WR作读写命令信号(高电平为读,低电平为写)。现有下列存储芯片:ROM(2K×8位,4K×4位,8K×8位),RAM(1K×4位,2K×8位,4K×8位),及74138译码器和其他门电路(门电路自定)。试从上述规格中选用合适芯片,画出CPU和存储芯片的连接图。要求:

(1)6000H ~ 67FFH 为系统区。6800H~6BFFH 为用户区

(2)指出选用的存储芯片类型及数量。

(3)详细画出片选逻辑。

①将 16进制转化为 2进制,判断存储空间的大小

由数据线可以看出来所选的位数是 8 位

a. 系统区

6000H = 0110 0000 0000 0000 0000

67FFH =0110 0111 1111 1111 1111

在这个地址区间内,前 5 位的地址是不变的,后11位的地址是变的。存储容量的大小用 11 位就可以了,根据范围可以判断应选择一片 2K x 8位的ROM,如果用 4K 或者 8K 的就都超了

b.用户区

6800H = 0110 1000 0000 0000

6BFFH = 0110 1011 1111 1111

在这个地址区间内,后10位的地址是改变的,所以此区域所用的芯片是1K x 8 位的。

②分配 CPU 的地址线

将 CPU的低11位地址 A0 ~ A10 与 2K x 8位的 ROM 地址线相连。CPU 的低10位地址 A0~A9 与两片 RAM 相连,相当于位扩展的方式

③ 片选信号的形成

判断哪些地址用于对内存的操作,哪些地址作为片选信号,且地址信号不可以有遗漏

74138 片选器的特点:可见连接

只有当 G1=1,G2A=0,G2B=0 的时候片选器才会工作,所以将地址线的高位处 不变的那几位 01100中的 A15,A14 分别介入 G2A,G1

当 CPU 从地址总线发出一个地址的时候,需要判断出是发送给内存的,而不是其他 I/O设备的,所以必须通过给出的 MREQ (低电平有效)去判断,而G2B(低)是低电压有效,所以让他俩相连,如果 G2B为低才会进行相应的译码,让内存进行相应的操作。

将高地址 A13 , A12 ,A11分别与输入信号 CBA 相连,用于判断是对系统程序芯片操作还是对用户程序芯片操作

由地址信号以及对应的真值表进行译码

如果 传入的为100也就是对系统芯片进行操作则译码后Y4为低,其余都是高,所以 Y4(低)接入系统区域的芯片

如果传入 101,Y5为低其余都为高则接入用户区的两片芯片,但是这两片芯片都是 1K的,A10也是不变的那一位,所以A10要是0才可以访问用户区的两个芯片。所以只有在 Y5 是低电平,且 A10 也是低电平的情况下才能对用户区的两个芯片进行操作,增加一个与门

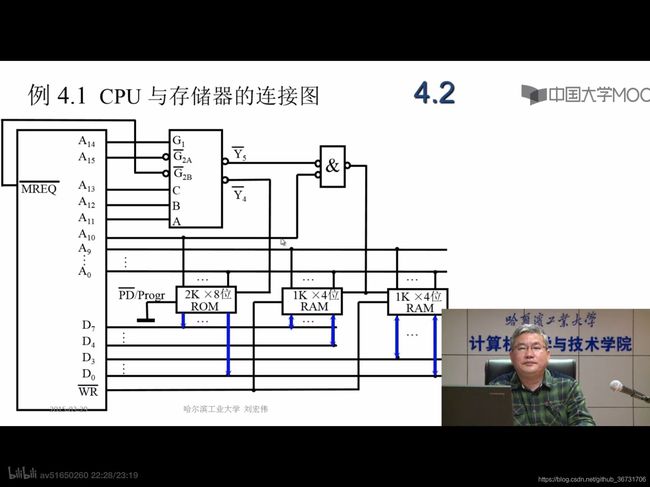

④数据线

首先 ROM只能读不能写,所以ROM的编程端 PD/progr接地工作状态,RAM 的读写信号与 CPU 的读写信号相连,RAM 通过位扩展,分别连CPU数据线的高四位与低4位

例题4.2

有点难,后期会补上

4.2.6存储器的校验

在计算机运行过程中种种原因会导致信息在存储过程中出错,所以需要校验编码的纠错,检错能力与编码的最小距离有关,即一个合法集中的合法代码,将它变为此合法集中另一个合法代码,需要改变的二进制的位数。最小距离越大检错,纠错能力越强

L -1=D+C(D>=C )

L------编码的最小距离

D------检验错误的位数

C------纠正错误的位数

1.汉明码的原理

我找到了一篇关于汉明码的博客 汉明码

例题:

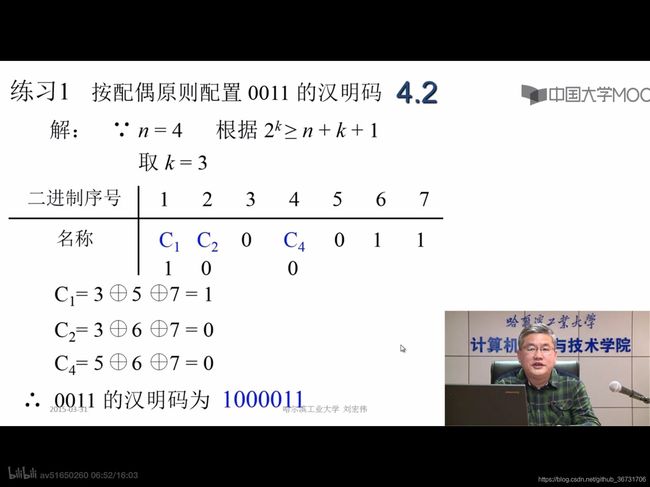

①添加校验位

n=4,由 公式(2k>=n+k+1)可得我们需要分成三组,形成的汉明码一共是 7位

2i 上放的为校验位,其余位置放需要配置的值。

②检测

由上方的 Ci 所承担的检测小组可以知道

C1检测 3,5,7 位上的数据

C2检测 3,6,7 位上的数据

C4检测 5,6,7 位上的数据

以 C1 为例,3,5,7上的1的个数为1(7),这里默认用 偶原则配置 1为偶数个 CI 为0,1为奇数个 Ci为1 所以这里 C1=1,其他的原理一样。

所以最后的汉明码为 1000011

2.汉明码的纠错过程

原理: 对传送过来的汉明码添加新的检测位 Pi,根据同样的分组规则(见 Ci 所承担的检测小组图),对相应的位置上的值按照奇偶检测进行纠错

例题:

本图需要注意的一点是: P2,P4 共同出现的,就是相交与 6,7,且汉明码默认只有一位出错;其中 P1没错,说明 7没错,所以错只能处在第6位上

其余例题详见课本 P102

4.2.7提高访存速度的措施

CPU 的速度越来越快,但是存储器的存取速度增加缓慢,分别可以从:寻找告诉元件,采用层次结构,调整主存的结构来增加对于存储器的存取速度

调增主存的结构:

1.单体多字系统

由于程序和数据在存储体内都是连续存放的,可以让 CPU 一次取出 4条指令(也可多条)作为一个整体单元放入数据寄存器中执行执行。当CPU 写入数据的时候再以 4个指令为单位写入

缺点:1.如果想要执行的指令不是连续的,那读入的其余3条指令都没用了

2. CPU 在向内存写入数据的时候从寄存器中读取数据,本来只想存放1个数据,但是该特性只能一次存放 4个数据,会造成对于原数据的覆盖

2.多体并行

(1)高位交叉

原理: 将内存的存储体分为多个模块,每个模块都有独立的 MAR ,MDR等,实现N个模块并行工作(CPU 在访问一个模块的时候,I/O访问另一个模块)。

对每个模块进行编码,高位地址表示体号,低位为体内的地址。用于存储器容量的扩展

缺点:CPU 连续访问存储单元的时候造成一个模块被频繁的访问。

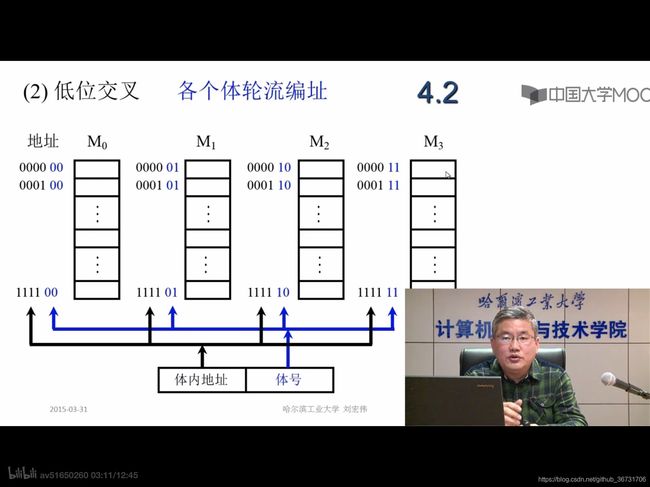

(2)低位交叉

相比于高位交叉,存储体的编码在后两位,体内的编码在前面。程序是顺序存取的,根据地址编码这样在存取指令的顺序就是横向的,用于存储器带宽和访问速度的提高

多体模块结构特点: 在不改变每个存储模块存取周期的前提下,提高存储器的带宽

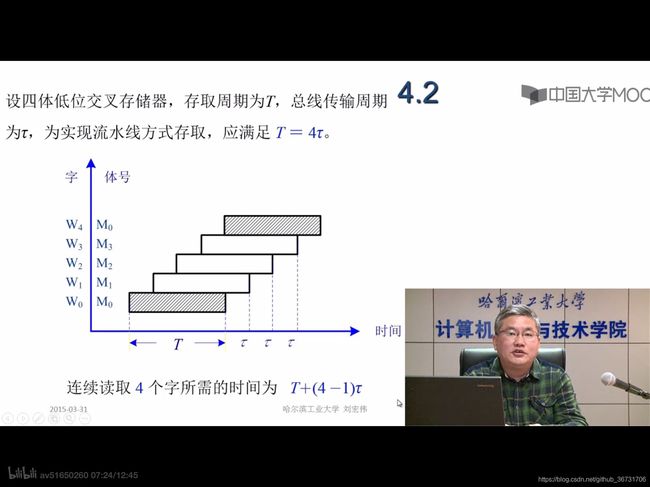

假设每个体的字长与数据总线一致,假设低位交叉的存储器模块数为 n,存取周期为T,总线传输时期为 t (tao),采用流水线的方式存取时应满足 T=nt

在最开始启动 M0 模块,当总线将数据传输完成后,在 t 时间之后启动 M3模块,在总线传输完成后启动 M2,…,如图所示,一个模块的存取周期为T,则在相应的 T时刻 M0完成了数据的传输,M1在 T+t时刻完成了数据的传输…。连续取四个字节后所需时间为 T+3t,对 n 个字节进行传输,时间为 T+(n-1)t

若采用高位交叉,则读取 n 个字所需要的时间为 nT

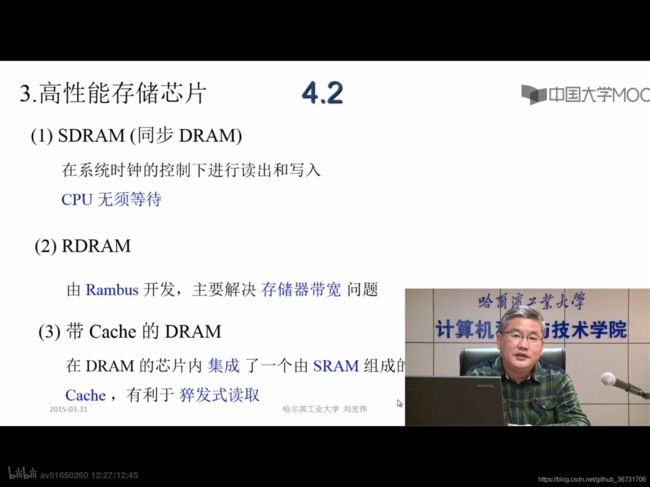

3.高性能的存储芯片

总结

只读存储器:大体的分类清除,以及只读存储器多用于系统数据的存储