555定时器(Timer)因内部有3个5K欧姆分压电阻而得名,是一种多用途的模数混合集成电路,它能方便地组成施密特触发器、单稳态触发器与多谐振荡器,而且成本低,性能可靠,在各种领域获得了广泛的应用。

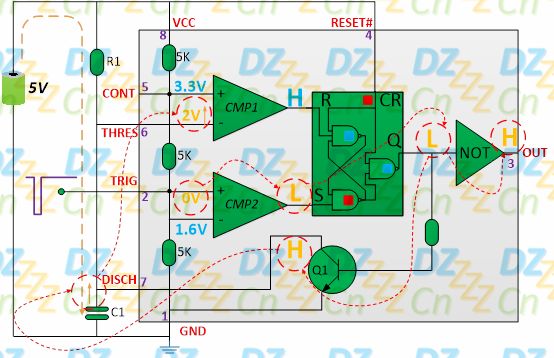

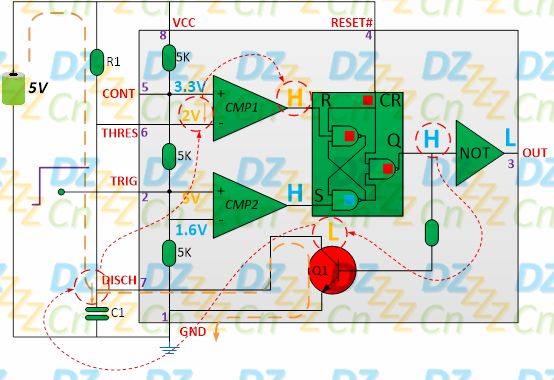

其原理框图如下图所示:

其中,第2脚TRIG(Trigger)为外部低电平信号触发端,第5脚为CONT(Control)为电压控制端,可通过外接电压来改变内部两个比较器的基准电压,不使用时应将该引脚串入0.01u电容接地以防止干扰。第6脚THRES(Threshold)为高电平触发端,第7脚DISCH(Discharge)为放电端,与内部放电三极管的集电极相连,用做定时器时电容的放电。

555定时器最基本的功能就是定时,实质为一个单稳态触发器,即外加信号一旦到来后,单稳态触发器可以产生时间可控制的脉冲宽度,这个脉冲的宽度就是我们需要的定时时间。为更方便地描述555定时器的原理,我们首先用下图所示电路来仿真一下单稳态触发器电路:

该单稳态触发器电路是负脉冲触发,因此我们设置周期为50ms,而高电平宽度为49ms,亦即负脉冲(低电平)宽度为1ms,仿真波形如下图所示:

从波形图上可以看到,每来一个负脉冲(低电平)信号(橙色),则电路输出固定宽度的脉冲(蓝色),此电路的输出脉冲宽度由电阻R1与电容C1决定,约为1.1R1C1(即1.1×1×10=11ms),我们将细节部分放大后测量一下输出的实际数据,如下图所示:

仿真输出脉冲宽度约为11.0347ms,与理论值非常接近。为了更进一步分析电路的工作原理,我们用四通道示波器来跟踪如下图所示的三个信号波形:

其波形如下图所示:

与之前的波形是一样的,只不过加入了THR与DIS引脚(连接在一起的)的波形,我们将其中一部分放大如下图所示:

555芯片内部的三个5K电阻将5V直流电源电压,其中2/3(约3.3V)供给比较器CMP1的同相端,1/3(约1.6V)供给比较器CMP2的反相端。比较器CMP1的反相端经过电容C1接地,在电路刚刚上电时,由于电容C1两端的电压不能突变,反相端的电压比同相端低,因此比较器CMP1输出高电平H(由于RS触发器是数字逻辑,因此后级电路按高电平H与低电平L来区别)。而对于比较器CMP2,同相端默认电平是高电平(负脉冲触发),比反相端电压1.6V高,因此,比较器CMP2输出也为高电平H。

由于R=H,S=H,RS触发器处于状态保持,我们假设555定时芯片处于复位状态,此时触发器输出为高电平H(也可以是低电平,最后的结果是一样的),经过一个反相器NOT后,则电路输出为低电平L,其状态如下图所示:

另一方面触发器输出的高电平H使三极管Q1饱和导通,此时第7脚DISCH被拉为低电平L(相当于电容C1处于放电状态),这个引脚同时与比较器CMP1的反相端同电位,维持比较器CMP1输出为H,此时电路为稳定状态,且输出为低电平,在这个寂寞的黑夜里,一边静静地等待着外部触发信号的到来,一边欣赏着点点繁星的夜色,如下图所示:

如果外部触发(低电平)信号一直没有到来,则电路一直保持输出为低电平L,波形如下图所示:

皇天不负有心人,终于等到了期待已久的负电平触发脉冲,比较器CMP2的同相端电压低于反相端电压而输出低电平L,由于R=H,S=L,RS触发器处于置位状态输出低电平L,一方面经反相器NOT输出高电平H,另一方面使三极管Q1截止,此时直流5V电源通过电阻R1对电容C1充电,第6脚THRESHOLD电位开始上升,如下图所示:

在电容C1上的电压还没有超过3.3V(即VCC的2/3)前,比较器CMP1的输出状态是不会变化的,则如下图所示:

在电容C1充电期间,如果输入低电平触发脉冲撤消(即当前输入为高电平H),比较器CMP2输出为高电平H,由于R=H,S=H,RS触发器处于保持状态,不影响电路的输出状态,如下图所示:

当电容C1上电压超过3.3V时,则比较器CMP1输出为低电平L,由于R=L,S=H,触发器因处于置位状态而输出高电平H,一方面经反相器NOT输出低电平L,如下图所示:

另一方面触发器输出的高电平H使三极管Q1饱和导通,此时第7脚DISCH被拉为低电平L(相当于电容C1处于放电状态),这个引脚同时与比较器CMP1的反相端同电位,维持比较器CMP1输出为高电平H,此时电路又返回稳定状态,且输出为低电平,又是这样一个寂寞的黑夜里,一边静静地等待着外部触发信号的到来,一边欣赏着点点繁星的夜色,如下图所示:

此时波形如下图所示:

当然,输入触发信号有可能在电容C1充电期间一直保持为低电平,电容C1充电超过VCC的2/3时,比较器CMP1输出低电平,此时R=L,S=L,理论上RS触发器不允许出现这种状态,因此触发器输出一直为低电平L,也就是电容C1一直在充电直到5V电压,如下图所示

这也算是一种稳定状态,但这种状态是不允许出现的,也就是说,触发信号的宽度至少不应该比定时的宽度要长。

原文地址点击这里