NVIDIA Jetson TX1(3)

2.0 电源和系统管理

Jetson TX1模块设计思想是易于系统集成,它单电源供电(VDD_IN),还有一个可选的备份电池输入VDD_RTC,这个电源用来维持系统RTC。

Jetsin TX1模块要求电源以一个已知的顺序进行开关,顺序有一组控制信号确定,信号CARRIER_PWR_ON用来在TX1完全上电后使载板上电。

2.1 使用模型(UCM:Use Case Models)

l UCM #1

n 每天运行于最高性能时的时间是20%(剩下时间是SLEEP或OFF状态)

l UCM #2

n 每天运行于最高性能时的时间是100%

表2:TM670D(UCM#1,UCM#2)允许的GPU操作:

| UCM |

允许的GPU操作:GFLOPS(FP16) |

||

| Tj <= 70C |

Tj <= 90C |

Tj <= 105C |

|

| #1 |

1024 |

1024 |

942 |

| #2 |

1024 |

1024 |

942 |

表3:TM670D(UCM#1,UCM#2)允许的GPU运行频率:

| UCM |

允许的GPU运行频率 |

||

| Tj <= 70C |

Tj <= 90C |

Tj <= 105C |

|

| #1 |

1.73GHz |

1.63GHz |

1.55GHz |

| #2 |

1.68GHz |

1.55GHz |

1.47GHz |

Tj为SoC的结温

2.2 电源

VDD_IN:

必须由载板提供。电源需要满足的电气特性见第5节。

VDD_RTC:

备份电池能连接到这个输入,它用来在VDD_IN没有的时候,为RTC供电。这个脚直接连接到板子上的PMIC。当备份电池连接到PMIC时,RTC会保持其内容不丢失。

这个脚可连接:

l 超级电容(法拉电容、双层电解电容)

l 标准电容(钽电容)

l 可充电锂电池。

备份电池电压必须在2.5V到3.5V之间,电池会被恒流充电。也可以配置为恒压充电:2.5V到3.5V恒压充电和50uA到800uA恒流充电。

IO Rail电压:

TX1接口的所有信号都是参考于模块电压rail,不需要为模块提供IO电压。见设计指南。

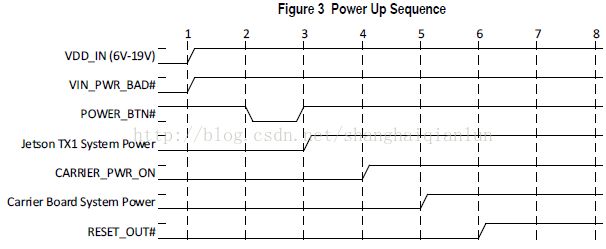

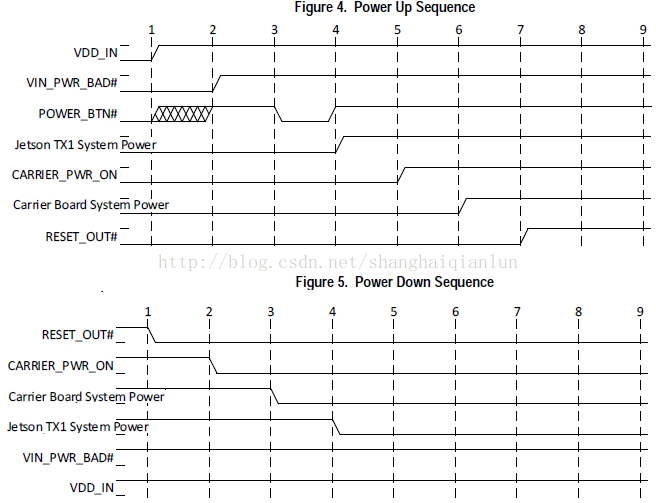

2.3 电源序列

TX1模块和载板的电源顺序必须按规定的顺序执行,以避免元件的永久损坏。

Powerup:

在上电期间,载板必须等到CARRIER_PWR_ON信号断言才开始上电。TX1解除断言RESET_OUT#信号表示开始执行系统boot

Powerdown:

一旦接收到Shutdown请求,TX1就断言RESET_OUT#信号,使得载板能将所有元件置于一个已知状态,CARRIER_PWR_ON信号会解除断言表示载板掉电,这时载板必须禁止它的电源,TX1会关闭它的电源。

2.4 电源状态

TX1有3个主要状态:OFF、ON和SLEEP。模块在通过硬件的或软件的事件触发在这些状态之间进行转换。

ON状态:

在ON状态,TX1所有功能正常运行。ON EVENT源自POWER_BTN#脚由低到高的跳变,但VDD_IN必须存在,且VIN_PWR_BAD#必须被断言(逻辑1)。当VIN达到它要求的电压值且稳定时,载板必须断言这个信号为高,这确保TX1模块直到VIN稳定时才上电。

注意:TX1的确包括一个Auto-Power-On的选项,一个系统输入(也就是:CHARGER_PRSNT#)如果断言,能使能模块上电。

当前即便在ON状态,TX1也采取了很多措施降低功耗:

l 先进的电源管理IC(PMIC)

l 系统电源门控

l 高级片上时钟门控

l 动态电压和频率调整(DVFS)

l Always-On逻辑用来唤醒系统,基于定时器或外部触发(比如按键)

l 低电源DRAM,LPDDR4

OFF状态:

系统没有供电。由Off事件使模块进入OFF状态。

表4 OFF状态事件

| 事件 |

细节 |

预先条件 |

| 电源按钮(按下10秒) |

保持POWER_BTN#为低7秒钟,将关机 |

在ON状态 |

| SW关机 |

软件发起 |

ON状态,软件操作 |

| 过热关机 |

如果内部温度达到不安全温度,硬件产生关机 |

任何状态 |

| 电源掉电 |

电源监视电路发现VDD_IN下降到5V以下,HW发起降低Tegra时钟,减少电源功耗 |

任何状态 |

SLEEP状态:

Sleep状态仅从ON状态进入,这个状态允许TX1重新进入正常状态而无需执行完整的boot过程,在这个状态,TX1运行于低功耗,输出逻辑维持进入这个状态前的状态(也就是说不会改变到0V电平)。

SLEEP状态能通过SW直接进入,例如,运行在OS下,一段时间没有操作,可触发SLEEP状态。

WAKE事件会是模块退出SLEEP状态,WAKE事件能来自外部设备,通过TX1连接器上的不同管脚。完整的列表见下面:

表5 SLEEP状态事件

| 事件 |

细节 |

| RTC WAKE up |

TX1里的定时器在进入SLEEP时能被编程,当超时时能产生WAKE事件并推出SLEEP状态。 |

| Thermal Condition |

TX1内部温度超过编程的冷和热限制之后。系统会迫使唤醒。所以它能报告并采取相应行动(例如:关机) |

| Low VDD_IN |

如果VDD_IN掉到6V以下。系统能唤醒并触发关机 |

| USB VBUS检测 |

如果VBUS应用于系统(USB线连着),然后,设备能配置成唤醒和枚举 |

| SD卡检测 |

卡检测脚。能配置为唤醒系统 |

| WIFI唤醒 |

Wifi能配置成用来唤醒系统 |

| Bluetooth唤醒 |

蓝牙事件也可使系统唤醒 |

| 连接器上WAKE信号唤醒 |

在连接器上有16个这样的信号,列表如下 |

表6 可编程接口唤醒事件

| 事件 |

连接器上的脚 |

Wake# |

| 音频中断 |

GPIO20_AUD_INT |

4 |

| 外部BT对AP的唤醒请求 |

GPIO13_BT_WAKE_AP |

10 |

| 外部对WiFi对AP的唤醒请求 |

GPIO10_WIFI_WAKE_AP |

11 |

| 调制解调器对AP准备好 |

GPIO17_MDM2AP_READY |

14 |

| 调制解调器冷启动告警 |

GPIO18_MDM_COLDBOOT |

15 |

| HDMI CEC |

HDMI_CEC |

19 |

| GPIO扩展器0中断 |

GPIO_EXP0_INT |

21 |

| 电源按钮On |

POWER_BTN# |

24 |

| 充电中断 |

CHARGING# |

26 |

| 来自载板的休眠请求 |

SLEEP# |

27 |

| Ambient/Proximity中断 |

GPIO8_ALS_PROX_INT |

32 |

| HDMI热插拔中断 |

DP1_HPD |

53 |

| 电池低告警 |

BATLOW# |

57 |

| 主调整解调器对AP的唤醒请求 |

GPIO16_MDM_WAKE_AP |

61 |

| 触摸控制中断 |

GPIO6_TOUCH_INT |

62 |

| 运动传感器中断 |

GPIO9_MOTION_INT |

63 |

2.5 热管理

TX1可运行于不同的工作负荷和环境条件,设计时采用了主动和被动两种散热方式,模块包含多种硬件的和软件的方法用于限制内部温度在运行允许的极限范围内。更详细的内容见热设计指南。

2.6 时钟

TX1模块的运行不需要外部时钟,所有的时钟均内部产生,这其中也包括低功耗的用于实时操作的32.768kHz时钟。

下面的时钟由TX1模块提供,可用于外设接口:AUDIO_MCLK,TOUCH_CLK, SPI0_CLK, SPI1_CLK, SPI2_CLK, CAM0_MCLK, CAM1_MCLK

2.7 WiFi电源状态

TX1集成5G WiFi802.11ac客户端,有下面的电源状态:

STA模式

l PM0

不节电,Always On

l PM1

传统的802.11节电,STA必须通过设置数据包的PM位向AP表明它正进入节电模式。随着来自AP的响应,它进入节电模式。STA必须周期唤醒(周期=DTIM)以便检查在TIM映射图里的AID。如果AID置位,STA会使用PS-Poll包来存取缓冲包(每个缓冲包一个PS-Poll),这是一种低效的机制,因为会导致通讯突发增加的趋势。

l PM2

厂家实现的,在PM2模式,每当有通讯发生的时候(Tx或Rx),DUT都会退出节电模式,并保持直到包交换停止的时间超过最小的空闲周期(典型200ms),有流量的时候,PM2会运行在近乎PM0模式,几乎没有PS相关的延迟,没有流量的时候,PM2类似于PM1节电模式。

P2PGroup-owner节电状态

l OPS(Opportunistic power save)

当所有相关的客户处于休眠状态的时候,OPS允许P2P组拥有者(P2P Group Owner)进入节电状态。在P2P组拥有者存在期间,P2P电源管理协议定义一个有效周期“CTWindow”(Client Traffic Window),P2P客户在CTWindow期间允许传输。如果在CTWindow结束的时候,所有相关的P2P客户都处于休眠状态,P2P组拥有着允许休眠直到下个信标时间。

为了改变OPS模式:

使用wpa_cli工具发布命令“p2p_set ctwindow

这里‘value’是CTWindow,单位ms

使用wpa_cli工具,发布命令“p2p_set opps

这里value为‘1/0’,分别使能/禁止OPS。(为了影响固件,每当CTWindow改变的时候,必须发布此命令)

l NoA(Notice-of-Absence)

NoA类似于OPS。对NoA,GO定义缺席周期,带有一个信号通知元素,包括信标帧和Probe响应

为了配置NoA:

使用wpa_cli工具发布命令“p2p_set_noa

这里,duration是每个缺席周期的长度,start time是第一个缺席周期的开始时间(在当前信标帧之后),count是在当前NoA期间,计划的缺席周期数目。

2.8 蓝牙电源状态

集成的蓝牙控制器,包含下面的电源状态:

l Active:这是缺省状态,不节电

l LP:这是节电状态,BT芯片会进入低电源模式,通讯时会被唤醒。

为了改变模式,断言/解除断言ext_wakeGPIO会将芯片置于Active或LP模式。

BT控制器还包括一个唤醒BT功能,当它收到数据时,芯片会断言Host_wake GPIO。AP能把它看作为一个唤醒中断或通知GPIO,但这也要看AP所处的状态,

2.9 以太网

TX1上的以太网设备包含许多节电特性,参考有关手册。

2.10 载板电源设计

注意:Jetson TX1不能热插拔,在安装或移除模块时,主电源(VDD_IN)必须断开足够时间(推荐大于1分钟),以便电源彻底释放掉。

图2 电源方块图

表5 Jetson TX1 电源&系统脚描述

| 管脚 |

Jetson TX1脚的名称 |

Tegra X1信号 |

方向 |

类型 |

描述和使用 |

| C7 |

BATLOW# |

LCD_GPIO1 |

输入 |

CMOS 1.8V |

GPIO 电池电压低。没有这个功能,悬空。 |

| A48 |

CARRIR_PWR_ON |

|

输出 |

CMOS, 3.3V |

作为上电序列的一部分,当Jetson TX1认为载板可以上电的时候才断言这个信号。载板依据此此信号开始上电。 |

| B7 |

CARRIR_STBY# |

SOC_PWR_REQ |

输出 |

CMOS, 1.8V |

当Jetson TX1处于待机状态的时候,它把这个信号驱动成低。不支持这个功能时候,悬空这个脚。 |

| A49 |

CHARGER_PRSNT# |

|

输入 |

Open Drain, 1.8V |

可以用来支持自动上电:当主电源连接上的时候,TX1自动上电,而无须等待电源按钮按下。实现加电自动开机的功能 |

| A7 |

CHARGING# |

BUTTOM_VOL_DOWN |

输入 |

CMOS, 1.8V |

Charger中断。悬空。 |

| C16 |

FAN_PWM |

GPIO_PE7 |

输出 |

CMOS, 1.8V |

风扇控制,风扇PWM。没有风扇就不管这个信号,悬空。 |

| B17 |

FAN_TACH |

GPIO_PK7 |

输入 |

CMOS, 1.8V |

风扇控制,风扇Tach。没有风扇就1.8V拉高。 |

| E1 |

FORCE_RECOV# |

BUTTON_VOL_UP |

输入 |

CMOS, 1.8V |

强制恢复strap脚 |

| B50 |

POWER_BTN# |

BUTTOM_PWR_ON |

输入 |

Open Drain, 5.0V |

电源按钮,由载板产生输入至Jetson TX1,这个信号在Jetson TX1上是拉高的。不用电源按钮开关控制,悬空。 |

| A47 |

RESET_IN# |

SYS_RESET_IN_N |

双向 |

Open Drain, 1.8V |

系统复位,来自PMIC,去载板,请求系统的完整复位,也可以由载板驱动,以触发整个系统的复位,比如复位按钮。接外部复位按钮。 |

| A46 |

RESET_OUT# |

|

双向 |

CMOS, 1.8V |

来自PMIC(通过二极管)向Tegra、eMMC发送复位请求,载板驱动这个信号,强制复位Tegra或eMMC。 |

| E2 |

SLEEP# |

BUTTOM_SLIDE_SW |

输入 |

Open Drain, 1.8V |

载板向Jetson TX1发Sleep请求。悬空。 |

| B8 |

VIN_PWR_BAD# |

|

输入 |

CMOS-VDD_IN |

载板向Jetson TX1指示VDD_IN是不是正常。当VIN达到要求的电压且稳定的时候,载板应该断言这个信号为高,这个信号用来保证Jetson TX1在VIN稳定的时候才开始上电。 |

| A1 |

VDD_IN |

|

输入 |

5.5-19.6V |

主电源。5.5V-19.6V |

| A2 |

|||||

| B1 |

|||||

| B2 |

|||||

| C1 |

|||||

| C2 |

|||||

| A50 |

VDD_RTC |

(PMIC BBAT) |

双向 |

1.65-5.5V |

实时时钟模块的备份电源(连接到锂电池或超级电容上)。当系统没有电源时,由超级电容或电池供电。当系统有电时,PMIC供电给电容或电池充电。接一个超级电容。 |

评估板上关于RESET_OUT的处理:

RESET_OUT_L:

(1) 控制音频CODEC信号电平转换芯片的使能。

(2) 通过一个OC门与RESET_IN连在一起,去JTAG和debug header

(3) 来自一个上电复位芯片U32,对1V8电源检测来复位

(4) 来自1V8开关电源芯片

表7 Jetson TX1内部电源

| 电源 |

使用 |

(V) |

供电 |

源 |

| VDD_5V0_SYS |

开关电源和负载开关,轮流给Jetson TX1上的不同元件上电。 |

5.0 |

5V DC-DC |

VDD_IN |

| VDV_3V3_SYS |

LDO和负载开关,轮流给Jetson TX1上的不同元件上电。 |

3.3 |

3.3V DC-DC |

VDD_IN |

| VDD_CPU |

Tegra CPU |

1.0(var) |

OpenVREG |

VDD_5V0_SYS |

| VDD_GPU |

Tegra GPU |

1.0(var) |

OpenVREG |

VDD_5V0_SYS |

| VDD_SOC(CORE) |

Tegra SOC |

1.1(var) |

PMU Switcher 0 |

VDD_5V0_SYS |

| VDD_DDR_1V1 |

LPDDR4 |

1.1 |

PMU Switcher 1 |

VDD_5V0_SYS |

| VDD_PRE_REG_1V35 |

某些PMU LDO输入的源 |

1.35 |

PMU Switcher 2 |

VDD_5V0_SYS |

| VDD_1V8 |

Tegra, eMMC, WiFi |

1.8 |

PMU Switcher 3 |

VDD_5V0_SYS |

| AVDD_DSI_CSI_1V2 |

Tegra CSI和DSI |

1.2 |

PMU LDO 0 |

VDD_PRE_REG_1V35 |

| VDDIO_SDMMC_AP |

Tegra SDMMC |

1.8/2.8 |

PMU LDO 2 |

VDD_3V3_SYS |

| VDD_RTC |

Tegra实时时钟/Always-on Rail,这是Tegra X1电源,不要与Jetson TX1 VDD_RTC脚相混淆 |

0.9(Var) |

PMU LDO 4 |

VDD_5V0_SYS |

| AVDD_1V05_PLL |

Tegra PLLs |

1.05 |

PMU LDO 7 |

VDD_PRE_REG_1V35 |

| AVDD_SATA_HDMI_DP_1V05 |

Tegra SATA和HDMI |

1.05 |

PMU LDO 8 |

VDD_PRE_REG_1V35 |

| VDD_PEX_1V05 |

Tegra PEX/USB3.0 |

1.05 |

LDO |

VDD_1V8 |

| VDD_1V8_PLL_UTMIP |

Tegra USB PLL |

1.8 |

Load Switch |

VDD_1V8 |

| AVDD_IO_EDP_1V05 |

Tegra EDP |

1.05 |

Load Switch |

AVDD_1V05_PLL |

| VDD_3V3_SLP |

3.3V外设rail-off在深度睡眠状态 |

3.3 |

Load Switch |

VDD_3V3_SYS |

| VSS_1V8_COM |

Wi-Fi/BT |

1.8 |

Load Switch |

VDD_1V8 |

图3是Jetson TX1载板电源

关于上电顺序的问题:

为了确保可靠一致的的上电顺序,在JetsonTX1的连接器上实现了VIN_PWR_BAD#、CARRIER_PWR_ON和RESET_OUT#三个信号。VIN_PWR_BAD#信号有载板产生,送给Jetson TX1,以便在VDD_IN稳定之前保持Jetson TX1处于关机状态,它还可能给TX1上的其它待机电路上电,这个信号阻止Jetson TX1过早上电。

像看到的的上电序列一样,Jetson TX1在载板之前上电,CARRIER_PWR_ON信号在Jetson TX1之前产生,送到载板上,表示JetsonTX1已经上电,载板可以上电了。

在载板上电后的一段足够时间之后,RESET_OUT#解除断言。

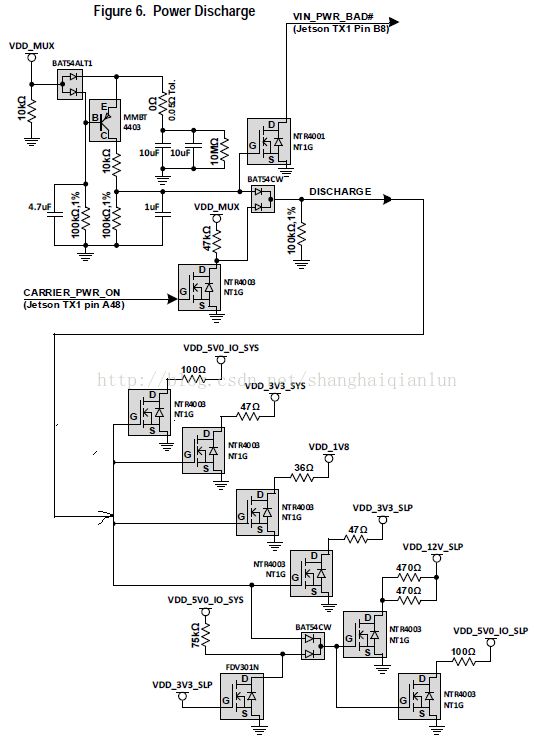

关于放电:

为了满足掉电顺序,需要放电电路,在下面的放电电路中,基于CARRIER_POWER_ON信号的变化或主电源(VDD_MUX/VDD_IN)断电,产生了DISCHARGE信号,当DISCHARGE断言时,VDD_5V0_IO_SYS、VDD_3V3_SYS、VDD_1V8和VDD_3V3_SLP以一种受控的方式强制到地,VDD_MUX断电也会引起产生VIN_PWR_BAD#,这个信号控制Jetson TX1上的主5V电源。

电源监视

在Jetson TX1上有一个电源监视电路,监视主DC、GPU和CPU电源,并触发WARN输出,或CRIT(critical)输出。

电压监视

电压监视电路用来监视主DC、VDD_IN是否降到一个可接受的电平,

深度休眠唤醒考虑

为了唤醒要求某些事件发生,这与操作系统有关,检查平台的设计指南和参考原理图。

自动上电

当VDD_IN加电之后,系统即上电而不用等待电源按钮按下,为了实现这种自动上电,在VDD_IN电源上电到CHAERGER_PRSNT#被驱动为高期间,需要一个特定的序列。CHARGER_PRSNT#脚连接到Jetson TX1,自VDD_IN达到最低电平5.5V起,要求至少300ms的延迟之后CHARGER_PRSNT#才能驱动为低,为了实现自动上电。可有下面三种选项

1) 微处理器:被推荐。如果一个微控制器已经被用来控制上电

2) 监视IC:使用一个监视IC,以及有关分立器件,和满足上电顺序的要求

3) 分立电路:使用分立电路,以满足顺序要求。

一、微处理器

l 在微处理器退出复位后等待300ms后再使CHARGER_PRSNT#或POWER_BTN#为低。

l 如果使用POWER_BTN#,保持其为低时长在40ms到5s范围

l 如果使用CHARGER_PRSNT#,保持低的时间大于200us

二、监视IC

三、分立电路