基于高性能视频编解码技术的解决方案,可以实现高清画质更快的压缩速度、更少的带宽消耗,在满足用户高清画质要求的前提下有效降低运营成本。阿里巴巴达摩院XG实验室,高级算法专家杨名远在LiveVideoStack线上分享中详细介绍了现有视频编码方案存在的挑战,并对高性能视频硬件编码技术进行了详细解析。

文 / 杨名远

整理 / LiveVideoStack

视频回放:https://www.livevideostack.cn...

大家好,非常高兴能够和大家分享我们团队这一年内所做的一些工作、研究和想法,本次分享的主题是高性能硬件视频编码。

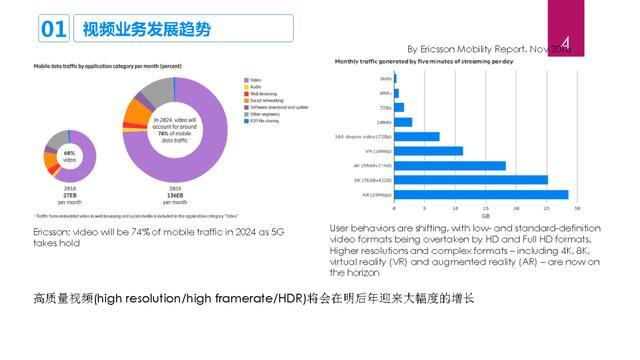

视频业务发展趋势

大约是在2018年,我们在考虑是否要面向视频编码方向做些研究,当时看到的一个趋势是:互联网视频头部内容如电商直播、游戏直播等视频内容质量越来越高,已经从标准尺寸转换为720P,甚至部分游戏直播场景、网红直播场景已经支持1080p/30fps、1080p/60fps,同时由于5G信道带宽的增加,AR/VR场景的应用出现复苏迹象。

从端侧来讲,手机屏幕的面积越来越大,目前已基本可以支持720P或1080P。随着柔性屏幕的扩展以及观看视野的放大,视频的体验也许可以从1080P扩展到4K、8K,高性能视频端到端传输系统已经具备了从内容制作到传输到终端整体的技术支持。

如图是一些调研报告,我们可以看到无线信道中的视频流量占有很大比重,预计到2024年比重可达到74%,同时用户的使用行为正在逐渐发生变化,从标清视频开始向高清HD甚至是4K、8K超高清方向转变。

因此,高质量视频(high resolution/high framerate/HDR)将在明后年迎来大幅度的增长

如图左边是一个商业调研报告,以电商直播、在线教育等新的基于行业特点的视频应用不断涌现,到2020年,中国网络视频行业规模达2940亿人民币,其中大部分来自于泛娱乐直播,包括短视频、在线视频等。

如图右边是来自赛灵思的针对各大上市公司的财报调研报告,报告中显示,普遍带宽成本在全年财政收入中所占比重较大,特别以游戏直播为主的视频网站,带宽成本甚至可能有超过10%的占比。所以,对于视频网站来说,带宽成本和存储成本是非常大的。

现有视频编码方案存在的挑战

现有视频编码方案主要分为两种,一种是软件方案,例如较多应用于X86平台上的软件编码器。另一种就是硬件方案,例如NVDIA GPU中的硬核,FPGA方案以及ASIC SoC的解决方案。

软件编码器的特点是可以进行复杂度配置的任意调整,例如x265,就有很多复杂度,不同的复杂度对应不同的压缩效率和处理能力,例如x265 veryslow档的带宽节省比superfast档高出40%的码率,但是单位时间内处理帧率会低很多。随着摩尔定律的失效,软件编码器在对时效性有要求的业务场景需要进行压缩性能和处理能力的平衡。

右图是对当前几种不同硬件编码器的水平进行的测试,从测试结果中可以看到,现存业界较好的硬件实时高清硬件编码方案的压缩性能基本可以达到x265 medium档的水平。

硬件编码技术

基于上述现有编码技术背景的调研以及现有方案的分析,我们发现,硬件编码器可能需要一种产品形态,即在现有硬件编码技术基础上追求更高的压缩性能,同时需要保证一定的实时性的处理能力,在压缩性能与处理能力间寻找一种平衡,以更好的解决带宽和存储成本的问题。

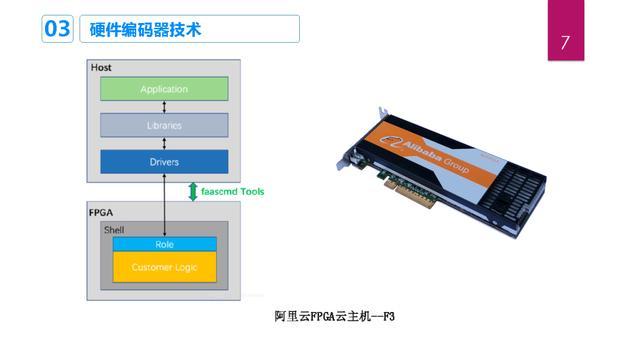

因此,我们团队经过一年多的努力,成功研发了一款基于FPGA的硬件编码器-XGH265,目前已经将该编码器部署在阿里云的异构服务平台(阿里云舜天平台)。右侧图就是FPGA卡,可以通过PCIE插在X86服务器上。图中Host代表X86服务器,通过PCIE与FPGA板卡进行信息交互。

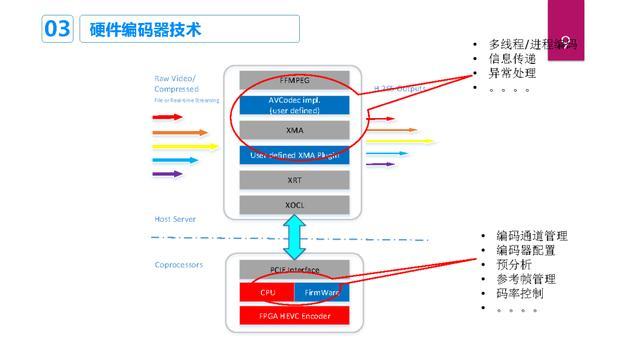

如上图中架构图所示,黄色区域代表X86服务器;蓝色区域代表异构服务器平台本身具备的硬件和架构,包括PCIE的驱动、传输等;绿色部分是我们搭建的整套系统,包括嵌入式CPU、DMA交互、数据传输等;橙色部分也是我们团队研发的265编码器,主要包括两个模块:预处理模块、编码模块。

软件方面,在X86服务器上采用的是较为流行的FFmpeg软件进行编码调度、命令下发等工作,原始编码码流会通过FFmpeg解码,将解码后的YUV图像通过PCIE传到FPGA卡上,FPGA卡上的CPU/固件系统在接收到YUV图像后进行编码任务调度,控制FPGA HEVC Encoder编码出265码流,将编好的码流回传至主服务器, 再通过协议封装成TS或MP4等格式进行推流。

X86服务器的FFmpeg支持多线程、多进程编码、编码参数等信息传递、以及对编码器的监控和异常处理。

FPGA编码器上的CPU和固件负责的工作有:编码通道管理、不同通道的编码器配置、预分析计算(包括场景检测、帧类型决策等)、参考帧管理、码率控制等。

如图是硬件编码器的编码框架,之前的一些硬件编码器设计中,MD模块大多是采用非RDO或者说是简单RDO的决策,而我们的设计目标是实现一款高压缩性能的编码器,因此在编码器架构设计中采用了全RDO的决策模式,整个决策过程可以得到最真实的重构像素和CABAC状态及时更新后的概率表,最大程度上保留了编码过程的依赖性,同时对DPCM流水线处理做了极致优化保证MD能够全遍历不同CU大小和更多的模式,从而获得了最好的压缩性能。

但是全RDO的编码架构设计会给硬件的高速实现带来很多困难,如编码模块中会存在大量复杂的反馈信息。在硬件设计中,处理性能的更好实现主要是基于数据的流水和并行处理,因此反馈机制所要承担的压力就会比较大,如果在一定时间内反馈的数据没有到达则流水处理就需要等待,所以说反馈机制的设计是编码器设计实现中的一个难点。

我们在流水线设计和算法设计上的优化解决了这些难题,比如通过对TU流水线的Cycle级精细化控制,频域Distortion预估等架构和算法的设计既增加了流水线的吞吐量,又保持了各个模块的信息获取的依赖关系。类似的设计和算法优化还有很多,由于篇幅的限制在此就不一一列举了。

从视频编码的角度来说,如H.265、H.266/VVC等,压缩性能的提升很大程度上来自反馈机制或者模块间的耦合。为了尽可能保证实现265比较高的压缩性能,因此在设计架构时,对于反馈机制部分我们投入了很大的精力进行设计与优化。

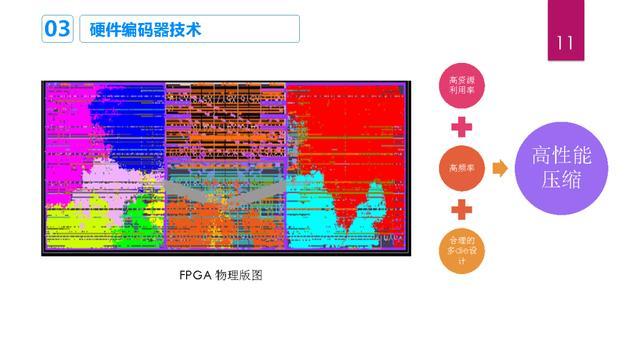

如图是FPGA的物理版图,由三个die组成,每个die之间通过连线的方式进行数据传递,不同色彩的模块代表不同的编码模块,资源的利用非常密集。实现了编码器的三大特点:高资源利用率、高频率(核心计算模块的主频已达到400M)、合理的多die设计,这三个特点保证了高性能压缩的能力。

以下是我们实现的硬件编码器的一些主要特性:

l 全RDO架构保证了视频中低码率段的压缩性能

l 支持CBR、CRF、CQP等各类码控算法

l 场景检测、帧类型决策、码率控制等算法为软件算法,可以支持随时升级

l 支持延迟可配置,延迟从几帧到几十帧

l 支持高性能主管调节,提升主客观性能,减少马赛克效应的出现

l 支持Close GOP,OPEN GOP和自适应B帧

l 流媒体系统采用ffmpeg,便于与现有大部分系统对接

硬件编码器性能

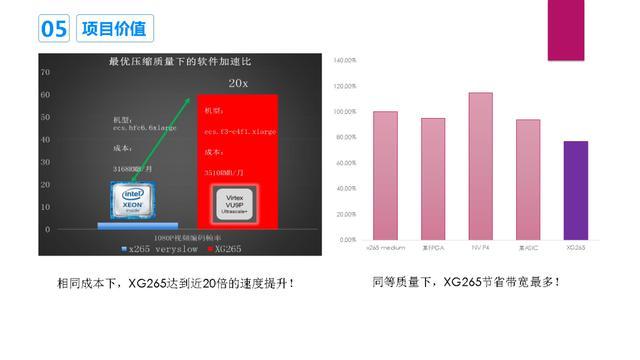

最后是XGH265与x265 veryslow档 软件加速比的一个测试比较。在阿里云标准机型下,在同等成本下,XGH265达到近20倍速度的提升。在压缩性能方面,同等质量下,XGH265节省带宽最多。