计算机组成原理--mooc

第四章存储系统

参考链接:计算机组成原理课后答案第四章-庞海波

参考链接:計算机组成原理第3章习题参考答案

参考链接:计算机组成原理第四章存储器复习

4.1、存储体系层次结构

哈弗结构 (Harvard Architecture)是指 ( ) (单选)

A.数据和指令分别存放

B.数据和指令统一存放

C.指令和数据分时存放

D.指令和数据串行存放

正确答案:A

2、如果一个被访问的存储单元,很快会再次被访问,这种局部性是( )(单选)

A.时间局部性

B.空间局部性

C.数据局部性

D.程序局部性

正确答案:A

3、下列关于存储系统层次结构的描述中正确的是( )(多选)

A.存储系统层次结构由Cache 、主存、辅助存储器三级体系构成

B.存储系统层次结构缓解了主存容量不足和速度不快的问题

C.构建存储系统层次结构的的原理是局部性原理

D.构建存储系统层次结构还有利于降低存储系统的价格

正确答案:A、B、C、D

4、下列属于加剧CPU和主存之间速度差异的原因的是( ) (多选)

A.由于技术与工作原理不同,CPU增速度明显高于主存增速率

B.指令执行过程中CPU需要多次访问主存

C.辅存容量不断增加

D.辅存速度太慢

正确答案:A、B

5、下列关于局部性的描述中正确的是 ( ) (多选)

A.局部性包括时间局部行和空间局部性

B.局部性是保证存储系统层次结构高效的基础

C.顺序程序结构具有空间局部性

D.循环程序结构具有时间局部性

正确答案:A、B、C、D

4.3、静态存储器工作原理

1某计算机字长16位,其存储器容量为64KB,按字编址时,其寻址范围是( ) (单选)

(PS:注意按字编址与按节编址2)

A.64K

B.32KB

C.32K

D.64KB

正确答案:C

2、一个16K*32位的SRAM存储芯片,其数据线和地址线之和为( )(单选)

A.48

B.46

C.36

D.39

正确答案:B

解释:16K = 2^4 * 2^10 ==>所以14根数据线+32根地址线

3、一个16K*32位的SRAM存储芯片,其内部采用位数相同的行列地址译码器,则其内部译码输出线的总量为( )(单选)

A.2^14

B.2^7

C.2^8

D.2^16

正确答案:C

类似的题目:

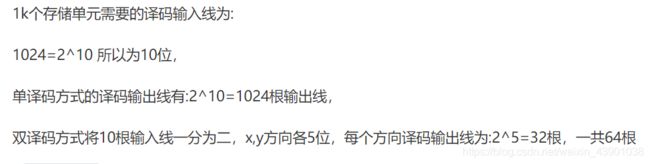

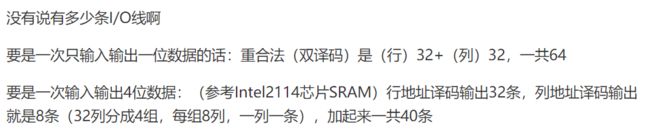

若存储器中有1k个存储单元,采用双译码方式要求译码输出线有几根?

4、下列关于SRAM工作原理的描述中 ,错误的是( )(单选)

A.6管SRAM中保存“1"的存储单元有两个工作管处于饱和导通状态

B.6管SRAM中保存“0"的存储单元有两个工作管处于饱和导通状态

C.对任何一个SRAM存储单元的读写,一定需要通过对应的行选通和列选通信号使与该存储单元对应的4个门控管都处于选通状态

D.现有一个1KB的SRAM存储器,若只使用其低端地址的前16个单元,则只要使用该存储器的前4位地址线,其余地址线可以不做任何端接处理

正确答案:D

4.4、动态存储工作器原理

1、某动态存储器存储单体的容量是64K*8位,采用双译码结构且地址线平均送到两个译码器,刷新周期是2ms 。下列关于动态存储器的描述中正确的是( )(多选)

A.动态存储器的刷新按行进行

B.该动态存储器的刷新地址计数器的模为2^8

C.该动态存储单体的数据线和地址线之和为16

D.该刷新地址计数器在2ms内必须进行一轮计数循环

正确答案:A、B、C、D

解析:地址线有 64k=2^16 由于双译码且地址线平均,因此 行X = 列Y = 8位,共有 2 ^ 8 根数据线,模为 2 ^ 8 。

刷新周期:对于DRAM的存储位元是基于电容器的电荷量存储,这个电荷量会随着时间和温度而减少,因此必须定期的刷新,以保持它们原来记忆的正确信息。对DRAM的所有存储单元恢复一次原状态的时间间隔,叫做刷新周期。因此,该刷新地址计数器在2ms内必须进行一轮计数循环。

2、下列属于导致DRAM 比SRAM慢的原因是( )(多选)

A.DRAM需要刷新操作

B.DRAM 读写过程中其地址分行、列分时传送

C.读操作前先要进行预充操作

D.DRAM的容量比SRAM容量大

正确答案:A、B、C

3、下列关于DRAM刷新的描述中,正确的是( )(多选)

A.刷新地址可由CPU给出

B.集中刷新虽然保持了存储单体的高速特性,但存在死时间

C.异步刷新方式既保持了存储单体的高速特性,也不存在死时间

D.分散刷新由于刷新次数过多,大大降低了存储单体的性能

正确答案:B、C、D

解析:

DRAM的刷新地址可由刷新地址计数器给出

4、下列关于动态存储器的描述中,正确的是 ( ) (多选)

A.读操作也具有刷新功能

B.DRAM 比相同工艺的SRAM要慢

C.某DRAM芯片地址引脚数据为12根,则其容量为16M

D.工具DRAM 的工作原理可知,相同容量的DRAM 比SRAM 功耗低

正确答案:A、B、C、D

解析:

类似:某DRAM芯片容量为16M×32,问这种芯片分别需要多少根地址线和数据与其连接

某DRAM芯片地址引脚数据为12根,则其容量为16M:

容量 = 2^12 * ( 2 ^ 12) = 2 ^ 24 = 16M

4.5、存储扩展

1、假定用若干块4K 4位的存储芯片组成一个8K8位的存储器,则地址1B1F所在芯片的最大地址是( )(单选)

A.1BFFH

B.1FFFH

C.1000H

D.0B00H

正确答案:B

2、假定用编号为0-3片16K 8位的存储芯片组成一个64K8位的存储器,从第0片到第3片依次使用64K存储空间中从低到高的16K空间,则编号为2的存储芯片在64K全局空间中的地址范围是( ) (单选)

A.8000H - BFFFH

B.C000H - FFFFH

C.4000H-7FFFH

D.2000H-5FFFH

正确答案:A

解析:

16K --> 2^14 --> 14位

64K --> 2^16 --> 16位

所以可得,16-14=2位,那么当构建存储器时,高两位A15~A14用来作为片选信号,后面的14位连接芯片。

编号为2的存储芯片地址空间范围为:

开始:11(前两位)0000 0000 0000 00(后面14位)= 8000H

末尾:11(前两位)1111 1111 1111 11 (后面14位)= BFFFH

3、下列关于存储扩展的描述中,错误的是( )(单选)

A.字扩展时,存储芯片的片选信号一般由地址译码器产生

B.只做位扩展时,所有存储芯片的片选信号都固定接0

C.CPU的读写控制线应连接到SRAM的读写控制线

D.只做字扩展时,不同存储芯片相同编号的数据位(如D2)不能连接到CPU数据总线的同一位上

正确答案:D

4.8、相联存储器

1、相联存储器是一种按内容访问的存储器,这里的"内容"是指 ( ) (单选)

A.所访问的数据

B.主存地址

C.从主存地址中分离出的标记(Tag)

D.从主存地址中分离出来的索引(Index)

正确答案:C

2、下列关于相联存储器的描述中,正确的是 ( ) (单选)

A.在实现技术相同的情况下,容量较小的相联存储器,速度较快

B.相联存储器结构简单,与静态存储器的访问方式基本相同

C.为提高查找速度,相联存储器的存储体应采用动态存储单元

D.访问相联存储器时既需要内容,也需要地址

正确答案:A

3、下列关于相联存储器的描述中,正确的是 ( )(多选)

A.按地址进行并行访问

B.对访问的内容进行并行比较

C.按关键字实现快速查找

D.相联存储器中存放的是主存数据的副本

正确答案:B、C

4、关于相联存储器,下面的论述中,错误的是______。

A.相联存储器按地址进行并行访问

B.相联存储器的每个存储单元都具有信息处理能力

C.相联存储器能并行进行各种比较操作

D.在知识库中应用相联存储器实现按关键字检索

正确答案:A

解析:

相联存储器(也称为按内容访问的存储器)不是按地址访问存储器,而是按所存数据字的全部内容或部分内容进行查找(或检索、更新)。为了进行检索操作,要求相联存储器能进行各种并行的比较操作(=、≠、>、<、max、min等)。其每个存储单元除了具有存储信息的功能之外,还应具有信息处理的能力,即每个存储单元必须有一个处理单元。

相联存储器除了应用于虚拟存储器与Cache中之外,还可用于数据库和知识库中按关键字进行检索。

相联存储器(CAM)是一种特殊的存储器,是一种基于数据内容进行访问的存储设备,特点是每个存储单元都必须有一个处理单元。当对其写入数据时,CAM能够自动选择一个未用的空单元进行存储;当要读出数据时,不是给出其存储单元的地址,而是直接给出该数据或该数据的一部分内容,CAM对所有的存储单元中的数据同时进行比较,并标记符合条件的所有数据以供读取。由于比较是同时、并行进行的,所以这种基于数据内容进行读/写的机制,其速度比基于地址进行读/写的方式要快许多。

在计算机系统中,相联存储器主要用于虚拟存储器和cache。在虚拟存储器中存放分段表、页表和快表,在高速缓冲存储器中存放cache的行地址。另外,相联存储器还经常用于数据库与知识库中按关键字进行检索。

4.9、cache地址映射与变换方法

1、某计算机的Cache共有16块,采用2路组相联映射方式(即每组2块)。每个主存块大小为32字节,按字节编址。主存129号单元所在主存块应装入到的Cache组号是( )(组号从0开始编号)(单选)

A.1

B.2

C.4

D.6

正确答案:C

解析:考查Cache与主存之间的映射方式。

主存按字节变址,第129号单元代表第129个字节。

主存129单元,所在的块号为129/32=4(从0开始编号);

由于Cache共有16块,采用2路组相联,因此共有8组,0,1,2,…,7。

主存的某一字块按模8映像到Cache某组的任一字块中,即主存的第0,8,16…字块可以映像到Cache第0组2个字块的任一字块中,而129号单元是位于第4块主存块中,因此将映射到Cache第4组2个字块的任一字块中。

2、某计算机的Cache共有8块,采用直接映射,每个主存块大小为32字节(按字节编址)。主存129号单元所在主存块应装入到的Cache块号是( )(块号从0开始编号) (单选)

A.1

B.2

C.4

D.6

正确答案:C

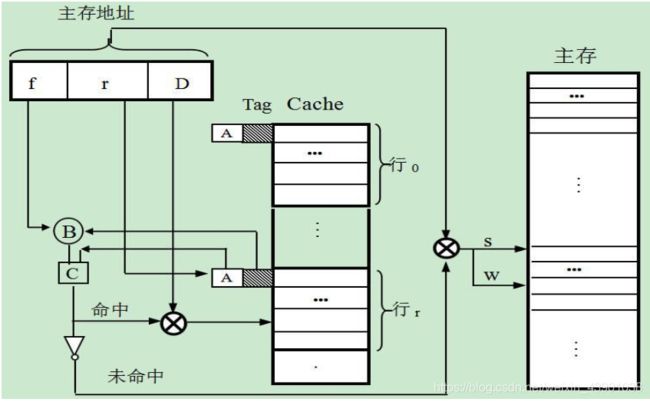

图中A、B、C、D是地址映射中要用到的信息或功能部件。下列关于A、B、C、D的描述中,正确的是( )(单选)

A. A为标记位,B为与门, C为比较电路,D为块内偏移地址

B.A为有效位,B为与门, C为比较电路,D为索引字段

C. A为有效位,B为比较电路, C为与门,D为块内偏移地址

D.A为有效位,B为比较电路, C为与门,D为索引字段

正确答案:C

4、下列关于Cache的描述中,正确的是 ( )(多选)

A.Cache的设计思想是在合理成本下提高其访问的命中率

B.Cache的功能全部由硬件实现

C.Cache块(行)的大小与主存块的大小一致

D.K=1的组相联就是直接相联

正确答案:A、B、C、D

4.12、虚拟存储器

1、虚拟存储器的最大容量是由( )决定的 (单选)

A.计算机系统的地址结构和外存空间

B.页表长度

C.内存空间

D.逻辑空间

正确答案:A

2、下列关于虚拟存储器的描述中 ,正确的是 ( ) (多选)

A.CPU基于虚拟地址访问虚拟存储器

B.页式虚拟存储器中,虚拟页的容量与主存物理块的容量相同

C.构成虚拟存储器需要硬件与软件的配合

D.采用虚拟存储技术解决了主存容量不足的问题

正确答案:A、B、C、D

3、下列属于构建虚拟存储器要用的技术/部件的是 ( ) (多选 )

A.页表

B.MMU (存储管理单元)

C.Cache (高速缓冲存储器)

D.磁盘等外存储器

正确答案:A、B、D

4、某页式虚拟存储器容量为4G ,主存容量为512M,页大小为8K,下列关于该虚拟存储器的描述中,正确的是 ( ) ( 多选)

A.虚拟地址为32位

B.物理地址29位

C.页表中的页表项数为 2^19项

D.页内偏移地址为13位

正确答案:A、B、C、D

解析:参考链接:计算机组成原理第9章习题参考

4.13、TLB

1、下列关于TLB的描述中,正确的是 ( )

A.TLB中存放的是页表项

B.TLB的工作原理是局部性原理

C.引入TLB的目的快速实现虚实地址转换

D.TLB中采用了类似Cache的映射方法

正确答案:A、B、C、D

2、下列关于使用TLB的虚实地址转换过程的描述中,错误的是 ( ) (多选)

A.CPU基于虚地址访问TLB

B.在虚实地址转换过程中,可能更新TLB

C.TLB命中后其直接输出物理地址

D.TLB的功能由硬件实现

正确答案:A、C

第四章测验

1、下列命令组合情况中,一次访存过程中,不可能发生的是( )

A.TLB未命中,Cache未命中,Page未命中

B.TLB未命中,Cache命中,Page命中

C.TLB命中,Cache未命中,Page命中

D.TLB命中,Cache命中,Page未命中

正确答案:D

答案解析

[解析] 考查TLB、Cache及Page之间的关系。

TLB即为快表,快表只是慢表(Page)的小小副本,因此TLB命中,必然Page也命中,而当Page命中,TLB则未必命中,故D不可能发生;而Cache的命中与否与TLB、Page的命中与否并无必然联系。

2、[单选题]下列关于Cache与TLB的描述中,哪个说法是错误的?

A、TLB与Cache中保存的数据是不同的

B、TLB miss之后,有可能直接在Cache中找到页表内容

C、TLB miss会导致程序执行出错,但是Cache miss不会

D、TLB和Cache的命中率都与程序的访存模式有关

答案C

TLB的作用是增加虚拟地址到物理地址的转换效率,TLB miss后仍然可以通过查询页表获得虚拟地址对应的物理地址。Cache miss后也可以在低等级存储中找到数据。

第六章 中央处理器

6.1、CPU的组成与功能

1、控制CPU内数据通路传送的部件是( ) (单选)

A.程序控制器

B.时序产生器

C.指令译码器

D.操作控制器

正确答案:D

2、下列可能是CPU组成部件的是( )(多选)

A.程序计数器 PC

B.指令寄存器IR

C.累加器AC

D.算术逻辑运算单元 ALU

正确答案:A、B、C、D

3、下列属于CPU功能的是 ( ) (多选)

A.算术逻辑运算功能

B.存储控制功能

C.操作控制功能

D.异常控制功能

正确答案:A、C、D

4、下列关于程序计数器的下列描述中,正确的是( ) (多选)

A.指令执行过程中会保存当前正在执行的指令地址

B.指令执行过程中会保存下一条指令的地址

C.其值不一定按PC+“1”的方式改变

D.CPU中可以没有PC

正确答案:A、B、C