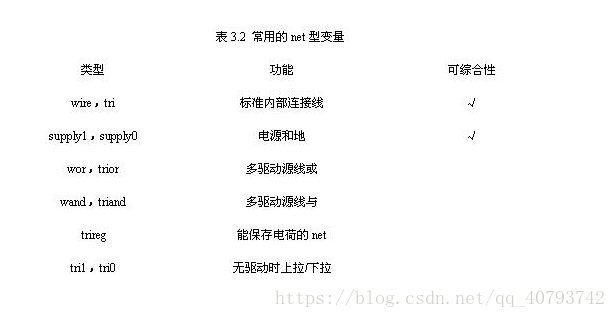

verilog HDL中wire和reg类型的区别

本文参考 夜煞CSDN 的CSDN 博客 ,有改动

全文地址请点击:https://blog.csdn.net/u010549444/article/details/50993274?utm_source=copy

基本概念的差别

wire型数据常用来表示以assign关键字指定的组合逻辑信号,模块的输入输出端口类型都默认为wire型,wire相当于物理连线,默认初始值是z。

reg型表示的寄存器类型,用于always模块内被赋值的信号,必须定义为reg型,代表触发器,常用于时序逻辑电路,reg相当于存储单元,默认初始值是x。

在赋值语句中的差别

在连续赋值语句中,表达式右侧的计算结果可以立即更新表达式的左侧。在理解上,相当于一个逻辑之后直接连了一条线,这个逻辑对应于表达式的右侧,而这条线就对应于wire。

在过程赋值语句中,表达式右侧的计算结果在某种条件的触发下放到一个变量当中,而这个变量可以声明成reg类型。根据触发条件的不同,过程赋值语句可以建模不同的硬件结构:如果这个条件是时钟的上升沿或下降沿,那么这个硬件模型就是一个触发器;如果这个条件是某一信号的高电平或低电平,那么这个硬件模型就是一个锁存器;如果这个条件是赋值语句右侧任意操作数的变化,那么这个硬件模型就是一个组合逻辑。

总而言之,wire只能被assign连续赋值,reg只能在initial和always中赋值

端口信号和内部信号的差别

信号可以分为端口信号和内部信号。出现在端口列表中的信号是端口信号,其它的信号为内部信号。

对于端口信号,一旦定义位input或者output端口,默认就定义成了wire类型,输入端口只能是net类型(wire/tri)。输出端口可以是net类型,也可以是reg类型。若输出端口在过程块中赋值则为register类型;若在过程块外赋值(包括实例化语句),则为net类型。

内部信号类型与输出端口相同,可以是net或reg类型。判断方法也与输出端口相同。若在过程块中赋值,则为reg类型;若在过程块外如assign赋值,则为net类型。

若信号既需要在过程块中赋值,又需要在过程块外赋值。这种情况是有可能出现的,如决断信号。这时需要一个中间信号转换。

inout是一个双向端口, inout端口不能声明为reg类型,只能是wire类型。

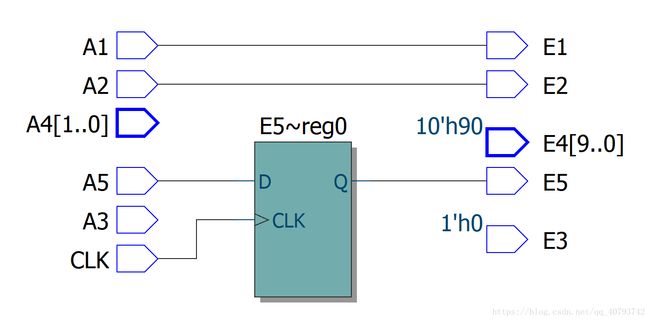

module net_reg(

//input

A1,A2,A3,A4,A5,CLK,

//output

E1,E2,E3,E4,E5

);

//端口信号

//1、输入端口定义,默认定义为wire类型,省略声明为wire A1,A2,A3;

input A1;

input A2;

input A3;

input [1:0]A4;

input A5;

input CLK;

//2、输出端口定义,默认定义为wire类型,省略声明为wire E1,E2,E3;

output E1;

output E2;

output E3;

output [9:0]E4;

output reg E5;

reg E2;

reg E3;

reg [9:0]E4;

//内部信号:过程块中赋值,则为reg类型;若在过程块外如assign赋值,则为net类型。

reg [9:0]in_var1;

reg [5:0]in_var2;

reg [3:0]cc;

initial begin //E3 在initial块中赋值,需要定义为reg

E3 = A3;

end

assign E1 = A1; // 连续赋值语句中被赋值,定义为wire

always @ (A1,A2,A3,A4)begin

E2 = A2; //E2在always过程块中被赋值,定义为reg类型

if(A3 == 0)

E3 = A3; //E3在always过程块中被赋值,定义为reg类型

if(A4 == 2'd0)begin

in_var1 = 10'd0;

in_var2 = 6'd36;

E4 = in_var1;

E4 = in_var2;

end

end

always @ (posedge CLK)begin

if(A5 == 0)begin

E5 <= 0;

cc <= 4'd0;

end

else begin

E5 <= A5;

cc <= cc + 1'b1;

end

end

endmodule

【注意】

虽然E2定义在了过程赋值语句中,但是这个条件是赋值语句右侧任意操作数的变化,那么这个硬件模型就是一个组合逻辑。

虽然E3定义在了过程赋值语句中,但是这个条件是某一信号的高电平或低电平,那么这个硬件模型就是一个锁存器;