HDLBits刷题合集—11 Latches and Flip-Flops

HDLBits刷题合集—11 Latches and Flip-Flops

HDLBits-81 Dff

Problem Statement

D触发器是存储一位数据并定期更新的电路,通常变化位于时钟信号的上升沿。

D触发器是由逻辑合成器在使用时钟always时产生的(参见alwaysblock2)。D触发器是“组合逻辑的后面跟着一个触发器”的最简单形式,其中组合逻辑部分只是一根导线。

创建一个D触发器。

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

always @(posedge clk)

begin

q <= d;

end

endmodule

HDLBits-82 Dff8

Problem Statement

创建一个8为D触发器。所有D触发器都由时钟信号clk的上升沿触发。

代码如下:

module top_module (

input clk,

input [7:0] d,

output [7:0] q

);

always @(posedge clk)

q <= d;

endmodule

HDLBits-83 Dff8r

Problem Statement

创建一个具有高电平同步复位功能的8位D触发器。所有D触发器都由时钟信号clk的上升沿触发。

代码如下:

module top_module (

input clk,

input reset, // Synchronous reset

input [7:0] d,

output [7:0] q

);

always @(posedge clk)

if (reset)

q <= 8'b0;

else

q <= d;

endmodule

HDLBits-84 Dff8r

Problem Statement

创建一个具有高电平同步复位功能的8位D触发器。触发器被重置为0x34,而不是0,所有D触发器都由时钟信号clk的下降沿触发。

代码如下:

module top_module (

input clk,

input reset,

input [7:0] d,

output [7:0] q

);

always @(negedge clk)

if (reset)

q <= 8'h34;

else

q <= d;

endmodule

HDLBits-85 Dff8ar

Problem Statement

创建一个具有高电平异步复位功能的8位D触发器。所有D触发器都由时钟信号clk的上升沿触发。

代码如下:

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output [7:0] q

);

always @(posedge clk or posedge areset)

if (areset)

q <= 8'b0;

else

q <= d;

endmodule

HDLBits-86 Dff8ar

Problem Statement

创建一个16位D触发器。有时候,只修改一组触发器的一部分是大有用处的。字节使能输入控制16个寄存器的每个字节是否应该在那个周期写入。byteena[0]控制高部分字节d[15:8],而byteena[0]控制低部分字节d[7:0]。

resetn是同步的、低电平有效。所有D触发器都由时钟信号clk的上升沿触发。

代码如下:

module top_module (

input clk,

input resetn,

input [1:0] byteena,

input [15:0] d,

output [15:0] q

);

always @(posedge clk) begin

if (~resetn)

q <= 16'b0;

else if (byteena[0] || byteena[1]) begin

//OR else if (|byteena) begin

if(byteena[1])

q[15:8] <= d[15:8];

if(byteena[0])

q[7:0] <= d[7:0];

end

end

endmodule

HDLBits-87 Exams/m2014 q4a

Problem Statement

实现下面的电路。

请注意,这是一个锁存器,因此会出现一个“预计会产生一个锁存器”的Quartus警告。

代码如下:

module top_module (

input d,

input ena,

output q);

always @(*) begin

if (ena)

q <= d;

end

endmodule

HDLBits-88 Exams/m2014 q4b

Problem Statement

实现下面的电路。

module top_module (

input clk,

input d,

input ar, // asynchronous reset

output q);

always @(posedge clk or posedge ar) begin

if (ar) begin

q <= 0;

end

else begin

q <= d;

end

end

endmodule

HDLBits-89 Exams/m2014 q4c

Problem Statement

实现下面的电路。

module top_module (

input clk,

input d,

input r, // synchronous reset

output q);

always @(posedge clk) begin

if (r)

q <= 1'b0;

else

q <= d;

end

endmodule

HDLBits-90 Exams/m2014 q4d

Problem Statement

实现下面的电路.

module top_module (

input clk,

input in,

output out);

always @(posedge clk)

out <= in ^ out;

endmodule

HDLBits-91 Mt2015 muxdff

Problem Statement

思考下面的时序电路:

假设你为这个电路实现分层次编写Verilog代码,使用包含触发器和多路选择器的子模块的三次实例化。为这个子模块编写一个名为top_module的Verilog模块(包含一个触发器和多路选择器)。

我理解的意思是触发器和多路选择器已经写好,我们要写顶层的模块。

代码如下:

module top_module (

input clk,

input L,

input r_in,

input q_in,

output reg Q);

always @(posedge clk) begin

Q <= L ? r_ina : q_in;

end

endmodule

HDLBits-92 Exams/2014 q4a

Problem Statement

思考如下所示的n位移位寄存器电路:

为电路的一级编写一个名为top_module的Verilog模块,包括触发器和多路选择器。

代码如下:

module top_module (

input clk,

input w, R, E, L,

output Q

);

always @(posedge clk) begin

Q <= L ? R : (E ? w : Q);

end

endmodule

HDLBits-93 Exams/ece241 2014 q4

Problem Statement

给定如图所示的有限状态机电路,假设D触发器在电路执行前初始复位为零。

实现这个电路。

module top_module (

input clk,

input x,

output z

);

reg q1 = 0;

reg q2 = 0;

reg q3 = 0;

always @(posedge clk) begin

q1 <= x ^ q1;

q2 <= x & ~q2;

q3 <= x | ~q3;

end

assign z = ~(q1 | q2 | q3);

endmodule

HDLBits-94 Exams/ece241 2013 q7

Problem Statement

JK触发器有如下所示的真值表。只用D触发器和逻辑门实现JK触发器。注意:Qold是D触发器在时钟上升沿到来之前的输出。

| J | K | Q |

|---|---|---|

| 0 | 0 | Qold |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | ~Qold |

代码如下:

module top_module (

input clk,

input j,

input k,

output Q);

always @(posedge clk)

begin

case ({j,k})

2'b00: Q <= Q;

2'b01: Q <= 1'b0;

2'b10: Q <= 1'b1;

2'b11: Q <= ~Q;

endcase

end

endmodule

HDLBits-95 Edgedetect

Problem Statement

对于8位向量中的每一位,当输入信号在一个时钟周期内从0变为下一个时钟周期内的1时进行检测(类似于上升沿检测)。输出位应在0到1转换发生后的周期内设置。

下图是一些例子。为了清晰起见,in[1]和pedge[1]分别显示。

module top_module (

input clk,

input [7:0] in,

output [7:0] pedge

);

reg [7:0] temp;

always @(posedge clk)

begin

temp <= in;

pedge <= ~temp & in;

end

endmodule

HDLBits-96 Edgedetect2

Problem Statement

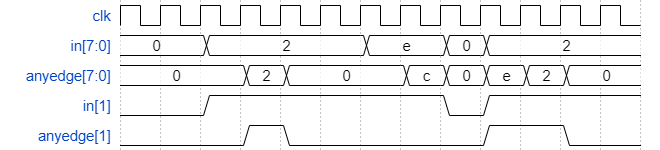

对于8位向量中的每一位,当输入信号在一个时钟周期变为下一个时钟周期时进行检测(类似于下降沿检测)。输出位应在0到1转换发生后的周期内设置。

下图是一些例子。为了清晰起见,in[1]和pedge[1]分别显示。

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);

reg [7:0] temp;

always @(posedge clk)

begin

temp <= in;

anyedge <= temp ^ in;

end

endmodule

HDLBits-97 Edgecapture

Problem Statement

对于32位向量中的每一位,当输入信号从一个时钟周期的1变为下一个时钟周期的0时进行捕获。“捕获”意味着输出将保持1,直到寄存器被重置(同步置位)。

每个输出位的行为类似于SR触发器:在发生1到0的转换之后,应该将输出位设置为1。当复位reset高的时候,输出位应该在时钟上升沿复位(到0)。如果上述两个事件同时发生,则置位reset具有优先级。在下面的示例波形的最后4个周期中,“reset”事件比“set”事件早发生一个周期,因此这里不存在冲突。

在下面的示例波形中,为了清晰起见,reset、in[1]和out[1]为再次单独显示。

代码如下:

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] temp;

wire [31:0] capture;

always @(posedge clk) begin

temp <= in;

end

assign capture = ~in & temp;

always @(posedge clk) begin

if (reset)

out <= 32'b0;

else

begin

for (int i=0; i<32; i=i+1)

begin

if(capture[i] == 1'b1)

out[i] <= 1'b1;

end

end

end

endmodule

HDLBits-98 Dualedge

Problem Statement

你可能很熟悉触发器,它会在时钟的上升沿触发,或者在时钟的下降沿触发。双边沿触发的触发器在时钟的两个边沿触发。然而,FPGAs没有双边沿触发器,而且always @(posedge clk or negedge clk)不被认为是一个合法的敏感列表。

建立一个双边沿触发的触发器电路:

module top_module (

input clk,

input d,

output q

);

reg q1, q2;

assign q = clk ? q1 : q2;

always @(posedge clk)

begin

q1 <= d;

end

always @(negedge clk)

begin

q2 <= d;

end

endmodule

Note

新手一枚,主要分享博客,记录学习过程,后期参考大佬代码或思想会一一列出。欢迎大家批评指正!