Verilog专题(三十八)根据波形写电路(十道题)

HDLBits网址:https://hdlbits.01xz.net/wiki/Main_Page

题目一

module top_module (input a,input b,output q );//assign q = 0; // Fix meendmodule

我的设计(一)

module top_module (input a,input b,output q );//assign q = a&b;endmodule

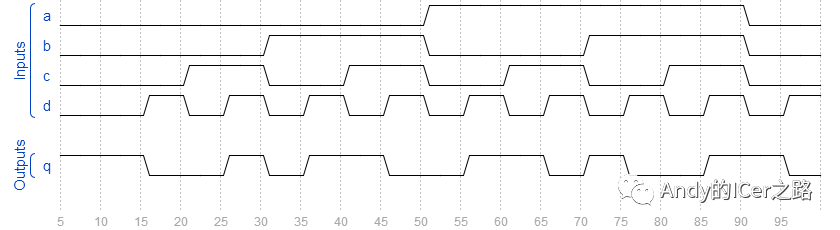

题目二

module top_module (input a,input b,input c,input d,output q );//assign q = 0; // Fix meendmodule

我的设计(二)

module top_module (input a,input b,input c,input d,output q );//assign q = ~(a^b^c^d);endmodule

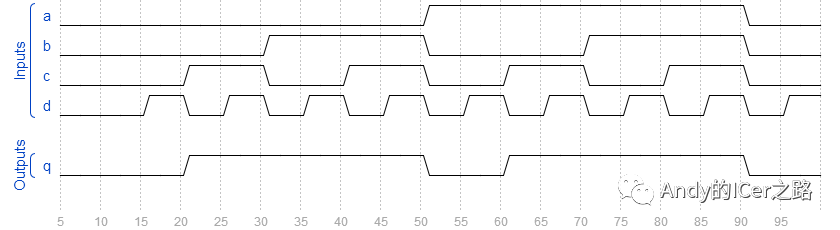

题目三

module top_module (input a,input b,input c,input d,output q );//assign q = 0; // Fix meendmodule

我的设计(三)

module top_module (input a,input b,input c,input d,output q );assign q = (a|b)&(d|c);endmodule

题目四

module top_module (input a,input b,input c,input d,output q );//assign q = 0; // Fix meendmodule

我的设计(四)

module top_module (input a,input b,input c,input d,output q );assign q = b | c;endmodule

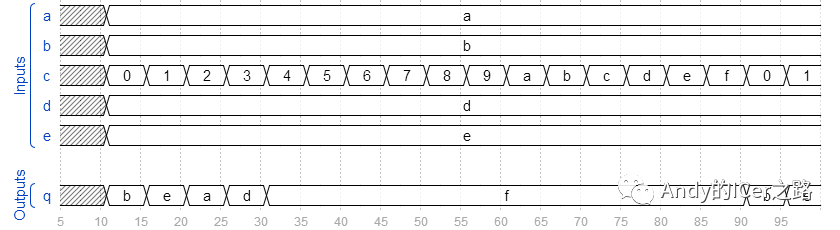

题目五

module top_module (input [3:0] a,input [3:0] b,input [3:0] c,input [3:0] d,input [3:0] e,output [3:0] q );endmodule

我的设计(五)

module top_module (input [3:0] a,input [3:0] b,input [3:0] c,input [3:0] d,input [3:0] e,output reg [3:0] q );always@(*)begincase(c)0:q=b;1:q=e;2:q=a;3:q=d;default:q=4'b1111;endcaseendendmodule

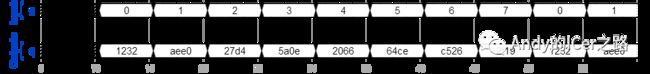

题目六

module top_module (input [2:0] a,output [15:0] q );endmodule

我的设计(六)

module top_module (input [2:0] a,output [15:0] q );always@(*)begincase(a)0:q=16'h1232;1:q=16'haee0;2:q=16'h27d4;3:q=16'h5a0e;4:q=16'h2066;5:q=16'h64ce;6:q=16'hc526;7:q=16'h2f19;endcaseendendmodule

题目七

module top_module (input clk,input a,output q );endmodule

我的设计(七)

module top_module (input clk,input a,output q );reg q_r1;always@(posedge clk) beginq_r1 <= a;endassign q = ~q_r1;endmodule

题目八

module top_module (input clock,input a,output p,output q );

我的设计(八)

module top_module (input clock,input a,output p,output q );always@(negedge clock)beginq=p;endalways@(clock)beginif(clock)p=a;else p=p;endendmodule

题目九

module top_module (input clk,input a,output [3:0] q );endmodule

我的设计(九)

module top_module (input clk,input a,output [3:0] q );always@(posedge clk)beginif(a) q=4;elseq=(q==6)?0:q+1;endendmodule

题目十

module top_module (input clk,input a,input b,output q,output state );endmodule

我的设计(十)

module top_module (input clk,input a,input b,output q,output state );assign q= state?~(a^b):a^b;wire current,next_state;parameter A=1'b0,B=1'b1;always @(*)case (current)A: next_state=(a&b)?B:A;B: next_state=(a|b)? B:A;endcasealways @(posedge clk)current<=next_state;assign state=current;endmodule

微信公众号

建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验,做公众号的目的就是记录自己的学习过程,很多东西回过头来可能就忘记了,为了记住知识和分享知识,希望自己可以保持更新,有兴趣的朋友可以关注一下!

![]()