PCIe总线是继承了PCI总线而设计而来的,所以理解PCIe总线先熟悉PCI总线会有很大帮助;我写的blog是根据《PCI Express 体系结构导读》作者:王齐,这本书学习后的整理笔记,都是自己理解后用自己的意思表达的,如果理解上有什么出入希望大家可以指出,请以作者原书为准,谢谢;

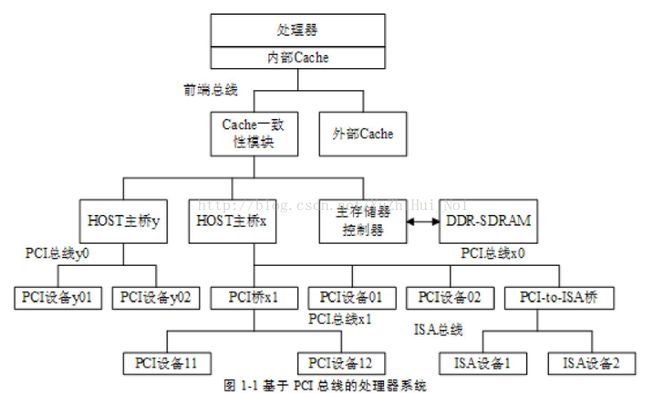

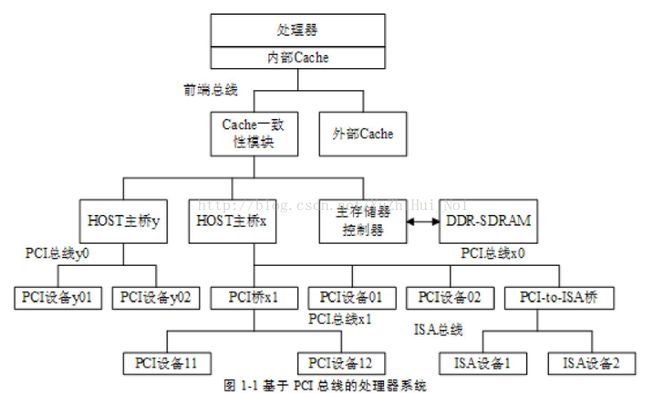

在看这个书时我规规矩矩的从前往后看,其实有些内容在后面会有很多理解和答案;先看下下面的图示,会很好理解PCI总线的整个架构:

PCI总线和其他总线比较有几个突出优点:

1、PCI总线空间和处理器空间隔离

PCI总线上的设备都有自己的PCI地址(PCI总线地址),处理器空间地址和PCI总线地址通过HOST主桥(HOST主桥就是连接处理器和PCI总线的一个设备器件)进行隔离。HOST主桥中有很多寄存器,这就可以使得处理器工作的频率和总线工作频率可以不一样,通过寄存器缓存数据。当处理器要访问PCI设备时,需要通过HOST主桥进行地址转换,把处理器地址转换成PCI总线地址,然后才能访问PCI设备;同理,PCI设备中的数据要往外走,也要通过HOST主桥进行地址转换。说到底,HOST主桥就是一个桥梁。

2、可扩展性

所谓可扩展性就是说在PCI总线上可以挂个PCI桥(PCI桥就是连接PCI总线和PCI总线的),然后PCI桥会推出一条PCI总线,该总线上又可以挂一个PCI桥,然后又可以推出一条PCI总线.......;但是一颗PCI总线树(PCI总线树以HOST主桥为树根PCI总线连接的所有设备)上的设备上限为256,其中包括HOST主桥和PCI桥;再提一个概念,上游总线和下游总线:上游总线是PCI桥靠近HOST主桥(或者说处理器)的一段总线,下游总线就是另外一端总线了;

PCI桥的作用可以隔离PCI设备,不影响各条总线的带宽,总线x1上通讯和总线x2上是否通讯无关;同一条总线上的设备可以自由通讯,同HOST主桥下(PCI域)中设备可以通讯,而不需要处理器操作。当PCI桥出现故障时,如:PCI桥x1出现故障,那么PCI设备11和PCI设备12可以通讯,但是数据不能出去,当然也不影响其他总线上的通讯;

如果HOST主桥支持Peer-to-Peer数据传输方式,那么设备可以跨PCI桥直接通讯,比如:PCI设备01和PCI设备12;

3、动态配置机制

PCI设备的地址可以由系统软件动态分配,解决了地址冲突。每一个PCI设备都有一个独立的配置空间,在配置空间中有该设备在总线上的地址系列的基地址,这个基地址也是有系统软件动态分配的。PCI桥的配置空间中有其PCI子树使用的地址范围;

4、共享总线机制

PCI总线上有多个设备,但他们需要通讯时,都必须向PCI总线仲裁器提出申请,当得到允许后才能在总线中发送数据;

5、中断机制

PCI总线上的设备可以使用四根中断请求信号INTA INTB INTC INTD向处理器发出中断请求;其中INTA是单功能设备,其他的是多功能设备;

PCI总线知识重点

1、HOST主桥

HOST主桥是用来隔离处理器的存储器域与PCI总线域的特殊桥片,管理PCI总线域。在其所管理的PCI设备中所有设备的配置空间都由HOST主桥通过配置读写总线周期访问的。

HOST主桥可以通过设置Inbound寄存器来让不同的PCI总线域中的设备进行通讯;

2、接口控制信号

a、FRAME#信号(#表示低电压有效),该信号表示一个PCI总线事务的开始和结束,当设备获得PCI总线仲裁允许,得到使用权后,将置该信号为低电压。

b、IRDY#信号,该信号由PCI主设备驱动(主设备可以主动发送读写命令,而从设备只能被动接受),其实就是PCI源设备驱动信号,表示主设备(源设备)已经把数据准备好了。如果总线为写事务,则表示在AD[31:0]上的数据有效;如果是读,则表示目标设备(从设备)已经准备好缓存了,主设备可以把数据发送到AD[31:0]上了;(这是个人的理解,和书上有点出入)

c、TRDY#信号,该信号由目标设备驱动,该信号有效,表示目标设备已经将数据准备好了。如果总线是写事务,则表示目标设备已经准备好了缓存,可以把数据写入目标设备中;如果总线是读事务,表示设备需要的数据在AD[31:0]上有效了。

d、stop#信号,表示目标设备请求主设备停止当前PCI总线的事务。目标设备可以要主设备对当前PCI总线事务进行重试(Retry,目标数据没有准备好),断连(Disconnect,目标设备不能接受较长的Burst操作),夭折(Target Abort,数据传输出错);

e、IDSEL信号,PCI总线在进行配置读写总线事务时,使用该信号选择PCI目标设备;

f、LOCK#信号,主设备可以使用该信号,将目标设备的某个资源锁定,以防止其他设备访问;

看下面的PCI总线事务时序图:

下面的时序图解释(书上的描述):

当一个 PCI 主设备需要使用 PCI 总线时,需要首先发送 REQ#信号,通过总线仲裁获得总线使用权,即 GNT#信号有效后,使用以下步骤完成一个完整 PCI 总线事务,对目标设备进行存储器或者 I/O 地址空间的读写访问。

(1) 当 PCI 主设备获得总线使用权之后, 将在 CLK1 的上升沿置 FRAME#信号有效, 启动 PCI总线事务。当 PCI 总线事务结束后,FRAME#信号将被置为无效。

(2) PCI 总线周期的第一个时钟周期(CLK1 的上升沿到 CLK2 的上升沿之间)为地址周期。在地址周期中,PCI 主设备将访问的目的地址和总线命令分别驱动到 AD[31:0]和 C/BE#信号上。如果当前总线命令是配置读写,那么 IDSEL 信号线也被置为有效,IDSEL 信号与 PCI 总线的AD[31:11]相连。

(3) 当 IRDY#、TRDY#和 DEVSEL#信号都有效后,总线事务将使用数据周期,进行数据传递。当 IRDY#和 TRDY#信号没有同时有效时,PCI 总线不能进行数据传递,PCI 总线使用这两个信号进行传送控制。

(4) PCI 总线支持突发周期,因此在地址周期之后可以有多个数据周期,可以传送多组数据。而目标设备并不知道突发周期的长度,如果目标设备不能继续接收数据时,可以 disconnect 当前总线事务。值得注意的是,只有存储器读写总线事务可以使用突发周期。一个完整的 PCI 总线事务远比上述过程复杂的多,因为 PCI 总线还支持许多传送方式,如双地址周期、fast back-to-back(快速背靠背)、插入等待状态、重试和断连、总线上的错误处理等一系列总线事务。

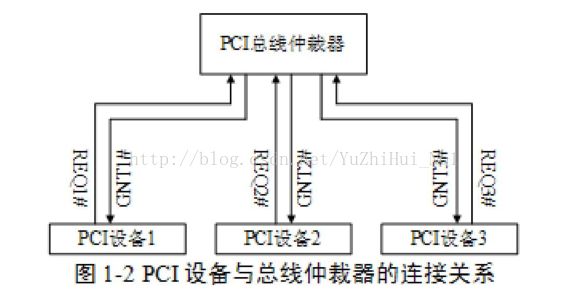

3、仲裁信号

当主设备(从设备被动操作,不需要仲裁信号)需要发起读写总线事务时(就是要占用总线使用权),必须先向仲裁器发起请求,当得到允许PCI总线使用权时,才可以开始通讯;而仲裁就是通过仲裁信号来处理的,仲裁信号有两个信号组成,REQ#和GNT#组成。每个仲裁器都要和主设备直接相连,所以仲裁器的信号接口数量将会限制PCI主设备的数量。解决办法是利用PCI桥推出新的PCI总线,因为在新的总线上也要有仲裁器。下面看下主设备和仲裁器的连接:

请求过程:PCI 主设备使用 PCI 总线进行数据传递时,需要首先置 REQ#信号有效,向 PCI 总线仲裁器发出总线申请,当 PCI 总线仲裁器允许 PCI 主设备获得 PCI 总线的使用权后,将置 GNT#信号为有效,并将其发送给指定的 PCI 主设备。而 PCI 主设备在获得总线使用权之后,将可以置FRAME#信号有效,与 PCI 从设备进行数据通信。

4、Posted和Non-Posted传送方式

Posted总线事务是指PCI主设备向PCI目标设备发送数据时,数据到达PCI桥后,上游总线就可以结束该事务,该事务就由PCI桥和下游总线去处理。这可以提高效率和解决PCI总线拥挤的问题;

Non-Posted总线事务是指PCI主设备向PCI目标设备发送数据时,数据必须到达目的设备后才能结束总线事务(此时上游总线不能提前结束);

很显然这两种传送数据方式中Posted方式会高效些,但是PCI总线中规定:只有在存储器写请求时,才可以使用Posted总线事务(PMW = Posted Memory Write);其他的存储器读请求和I/O读写请求、配置读写请求只能使用Non-Posted总线事务;

5、HOST处理器访问PCI设备

这涉及到地址域问题,到第二章可以更方便的理解。HOST处理器对PCI设备的数据访问主要包括两个方面内容:一、处理器对PCI设备的存储器和I/O读写请求;二、处理器对PCI设备进行配置读写;

处理器对PCI设备的I/O读写请求:如果有独立的I/O地址空间,则把PCI的I/O地址映射到存储域的I/O地址空间,然后处理器就可以通过 out/in 指令来访问PCI的数据;如果没有独立的I/O地址空间,则在HOST主桥初始化时,将PCI设备使用的I/O地址空间映射为处理器的存储器地址空间;然后处理器就可以直接访问这些映射出去的地址,当然访问这些地址时,会通过HOST主桥把这些请求转交到PCI总线上。

处理器对PCI设备的存储器读写请求:将PCI设备使用的BAR空间映射到“存储器域”的存储器地址空间。然后处理器就可以通过存储器读写指令访问存储器地址空间(HOST主桥会转化为PCI总线事务;)

6、PCI设备读写主存储器

PCI设备与存储器直接进行数据交换的过程也被称为DMA。PCI总线进行DMA操作时,需要得到数据的大小和目的地址(PCI总线域的物理地址,HOST主桥会负责地址转换);

转载地址: http://blog.csdn.net/yuzhihui_no1/article/details/45417709