modelsim平台下万兆phy仿真

软件版本

modelsim : 10.1a

vivado :2016.4

win10 系统

仿真步骤

用vivado生成ip core

具体过程跳过,我这里选择的是 10G Ethernet PCS/PMA ,保持默认配置。然后生成example工程(感谢xilinx提供,通过example工程可以快速将ip core用起来)。

生成的example的文件树如图, example工程已经报文的仿真TB文件,简直不要太方便。

在vivado 默认设置情况下, 直接点击左边的 Run Simulation ,则可以调用vivado simulator 进行仿真,好了,此文结束。

呵呵,偏离了主题,这里是想在modelsim平台下面仿真,继续往下看。

编译xilinx-modelsim联合仿真库

在vivado 的tools -> compile simulation libraries

这里的前面几个选项根据自己要求选择,重点在 compiled library location, 选择库存放的路径, simulator executable path指定modelsim仿真软件的路径。然后点击 compile, 等待完成, 编译时间根据个人选择的language, library, family 不同, 全部all的时候,编译时间会长一些,等待完成就行。

启动modelsim

在simulation setting 中选择modelsim simulator , 选择顶层TB, 注意库文件的位置。然后OK.

然后点击 run simulation .

提示错误( GG,为啥,为啥。。。), 不急,查看错误原因,提示执行compile.bat时出错, 找到这个文件,打开看看, compile.bat主要作用是指定modelsim的路径,然后执行demo_tb_compile.do 这个脚本文件。分析原因,应该是执行do脚本文件出错。

modelsim执行脚本

打开modelsim软件,将modelsim的仿真目录指定到vivado 工程仿真目录(compile.bat的文件夹下)。

具体方法在modelsim下的 file -> change directory ,或者直接在命令窗口通过cd 命令切换到仿真目录下。

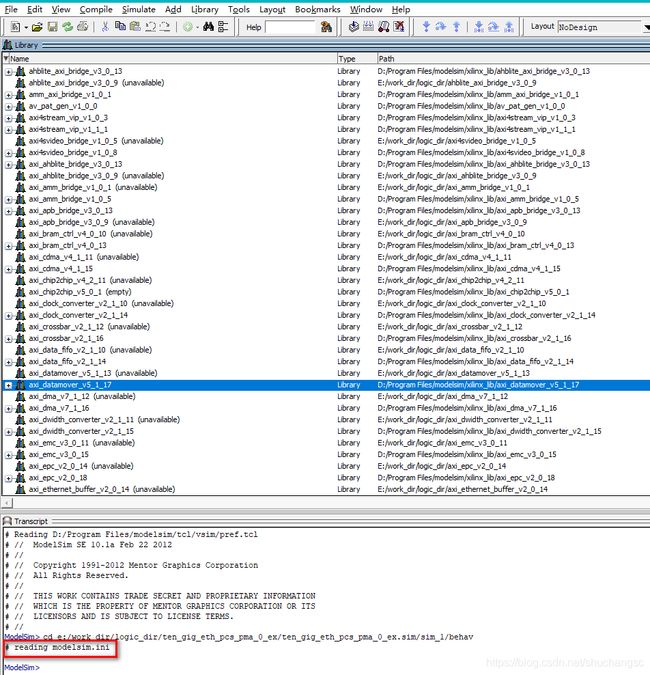

切换到此目录后, modelsim会自动读取当前的 modelsim.ini文件,加载库文件,可以在library窗口中看到 vivado编译后的xilinx仿真库文件。

查看当前目录下的文件, 执行do文件后,发现modelsim 软件自动关闭了。打开 demo_tb_compile.do文件查看。

应该是demo_tb_compile.do文件的最后一条命令 quit -force, 执行到这里强制关闭modelsim软件,这里用#将这一条命令注释掉(# quit -force).

重新打开modelsim,切换仿真目录,然后执行 do demo_tb_compile.do文件, 打印如下

由于本人之前未使用过脚本,也是一边看do文件,一边在网上搜modelsim脚本语言。这些打印的意思就不解释了,大概是脚本采用增量编译的方式,这里都是skiping。modelsim里面用vsim命令执行仿真, 这里没有,那么我自行添加了一下(抄的网上的命令格式)。

截取后面几行 ,vsim -gui -t 1ns -novopt xil_defaultlib.demo_tb , 这条命令就是指定demo_tb做仿真。其他附加参数自行百度。

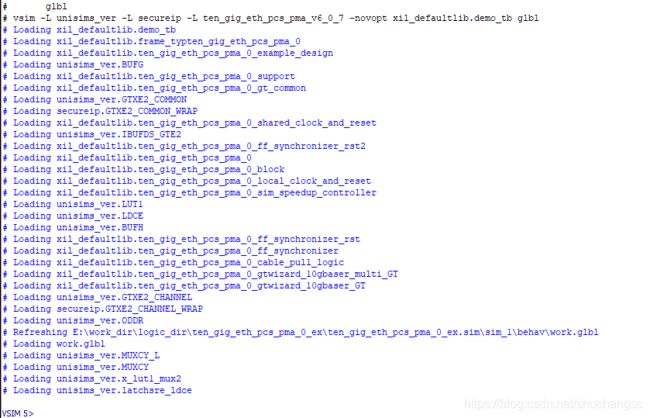

回到modelsim命令串口,再次执行do demo_tb_compile.do ,打印如下:

前面的打印和前一次打印一样,不一样的是这里多了 vsim -gui -t 1ns -novopt xil_defaultlib.demo_tb 打印,然后下面出现 error(vsim-3033) 报错。 错误的原因是找不到仿真库。

do文件里面vmap的目录下,的确找不到BUFG这个库文件, BUFG在unisims_ver 库下面, 于是修改一下vsim命令

vsim -L unisims_ver -gui -t ps -novopt xil_defaultlib.demo_tb

再次执行 do demo_tb_compile.do 。

BUFG得错误消失了,但是还有错误。提示在 GTXE2_COMMON.v下面找不到 实例B_GTXE2_COMMON.

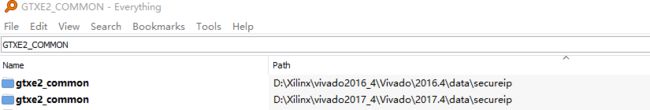

打开提示错误目录下的GTXE2_COMMON.v文件,这个文件里面例化了B_GTXE2_COMMON模块,但是确实找遍了vivado软件所有文件,都找不到B_GTXE2_COMMON模块,只能百度,啥都查不到(垃圾!!!) 。 想办法,在vivado的source窗口找,找不到,最后在电脑上面找 GTXE2_COMMON相关信息(死马当活马医), 找到了这个secureip目录,点进去看看

里面是加密模块,用记事本打开gtxe2_common_001.vp 文件,里面是一个 GTXE2_COMMON_WRAP的模块。 对比接口和B_GTXE2_COMMON的接口,居然是一样的, 这让我有了个大胆的想法, 我直接将 GTXE2_COMMON.v下的例化B_GTXE2_COMMON改成了 GTXE2_COMMON_WRAP(修改时,记得先备份源文件) 。

然后修改do文件,在vsim 里面连接secureip 库

vsim -L unisims_ver secureip -gui -t ns -novopt xil_defaultlib.demo_tb

然后回到modelsim再次执行 do demo_tb_compile.do 命令 。

这里找不到ten_gig_eth_pcs_pma_v6_0_7库,添加一下,这些都是tcl脚本的问题, 由于本人没写过tcl脚本,对这些不熟悉,都是通过错误,一边上网找答案,一边尝试,最终的读脚本如下,新手可以借鉴(大神请跳过)。

基本上找不到模块,就通过vlog编译一下, 找不到库就vmap映射一下库文件路径。

######################################################################

#

# File name : demo_tb_compile.do

# Created on: Wed Sep 25 13:48:38 +0800 2019

#

# Auto generated by Vivado for 'behavioral' simulation

#

######################################################################

vlib work

vlib msim

vlib msim/xil_defaultlib

#vlib msim/ten_gig_eth_pcs_pma_v6_0_7

#vlib msim/unisim

vmap xil_defaultlib msim/xil_defaultlib

vmap ten_gig_eth_pcs_pma_v6_0_7 E:/work_dir/logic_dir/ten_gig_eth_pcs_pma_0_ex/ten_gig_eth_pcs_pma_0_ex.cache/compile_simlib/ten_gig_eth_pcs_pma_v6_0_7

#vmap unisim msim/unisim

#vmap secureip E:/work_dir/logic_dir/ten_gig_eth_pcs_pma_0_ex/ten_gig_eth_pcs_pma_0_ex.cache/compile_simlib/secureip

vlog -64 -incr -work xil_defaultlib \

"../../../imports/ten_gig_eth_pcs_pma_0_ff_synchronizer_rst2.v" \

vlog -64 -incr -work ten_gig_eth_pcs_pma_v6_0_7 \

"../../../ten_gig_eth_pcs_pma_0_ex.ip_user_files/ipstatic/hdl/ten_gig_eth_pcs_pma_v6_0_rfs.v" \

vlog -64 -incr -work xil_defaultlib \

"../../../ten_gig_eth_pcs_pma_0_ex.srcs/sources_1/ip/ten_gig_eth_pcs_pma_0/synth/ten_gig_eth_pcs_pma_0_gtwizard_10gbaser_gt.v" \

"../../../ten_gig_eth_pcs_pma_0_ex.srcs/sources_1/ip/ten_gig_eth_pcs_pma_0/synth/ten_gig_eth_pcs_pma_0_gtwizard_10gbaser_multi_gt.v" \

"../../../ten_gig_eth_pcs_pma_0_ex.srcs/sources_1/ip/ten_gig_eth_pcs_pma_0/synth/ten_gig_eth_pcs_pma_0_ff_synchronizer_rst.v" \

"../../../ten_gig_eth_pcs_pma_0_ex.srcs/sources_1/ip/ten_gig_eth_pcs_pma_0/synth/ten_gig_eth_pcs_pma_0_ff_synchronizer.v" \

"../../../ten_gig_eth_pcs_pma_0_ex.srcs/sources_1/ip/ten_gig_eth_pcs_pma_0/synth/ten_gig_eth_pcs_pma_0_local_clock_and_reset.v" \

"../../../ten_gig_eth_pcs_pma_0_ex.srcs/sources_1/ip/ten_gig_eth_pcs_pma_0/synth/ten_gig_eth_pcs_pma_0_sim_speedup_controller.v" \

"../../../ten_gig_eth_pcs_pma_0_ex.srcs/sources_1/ip/ten_gig_eth_pcs_pma_0/synth/ten_gig_eth_pcs_pma_0_cable_pull_logic.v" \

"../../../ten_gig_eth_pcs_pma_0_ex.srcs/sources_1/ip/ten_gig_eth_pcs_pma_0/synth/ten_gig_eth_pcs_pma_0_block.v" \

"../../../ten_gig_eth_pcs_pma_0_ex.srcs/sources_1/ip/ten_gig_eth_pcs_pma_0/synth/ten_gig_eth_pcs_pma_0.v" \

"../../../imports/ten_gig_eth_pcs_pma_0_shared_clock_and_reset.v" \

"../../../imports/ten_gig_eth_pcs_pma_0_gt_common.v" \

"../../../imports/ten_gig_eth_pcs_pma_0_support.v" \

"../../../imports/ten_gig_eth_pcs_pma_0_example_design.v" \

"../../../imports/demo_tb.v" \

# compile glbl module

vlog -work ".glbl.v"

vsim -L unisims_ver -L ten_gig_eth_pcs_pma_v6_0_7 secureip -gui -t ps -novopt xil_defaultlib.demo_tb glbl

#quit -force

最后一次运行 do demo_tb_compile.do ,

仿真终于跑起来了。添加信号,然后 run -all , 又出错了,

WTF, 什么鬼, 上网搜索了好久,最后才发现我仿真时间单位错误,我这边实际运行命令为:

vsim -L unisims_ver -L secureip -L ten_gig_eth_pcs_pma_v6_0_7 -t ns -novopt xil_defaultlib.demo_tb glbl

这里的-t ns, 设置ns为单位,而tb里面是ps为单位的。 修改后就正常了。