FPGA基础知识(六)UG586 Mermoy Interface Solutions内存接口的生成与使用

背景:FPGA的片上BRAM内存较少,难以实现大量的存储。DDR的内存较多,若可直接用FPGA调用则可以实现很多东西。

目的:运用MIG调用DDR相关文档学习。

参阅的文档:DS176:Zynq-7000 AP SoC and 7 Series FPGAs Memory Interface Solutions Data Sheet

UG586: zynq-7000 AP Soc and 7 Series Devices Memory Interface Solutions

具体操作见:

FPGA实践教程(七)运用IPcore调用DDR https://blog.csdn.net/weixin_36474809/article/details/84942607

FPGA实践教程(五)PS用MIG调用DDR https://blog.csdn.net/weixin_36474809/article/details/80997945

目录

一、简介

二、在vivado中运用MIG(Memory interface generator)

三、定制与生成MIG core

四、其他选项

五、vivado集成设计环境

一、简介

Xilinx 7系列的FPGA的内存接口,MIS(memory interface solutions)core是一个预定制的,控制器和物理层接口,是AXI4(AMBA Advanced eXtensible Interface)DDR3与DDR2 SDRAM设备的从接口。文档UG586: zynq-7000 AP Soc and 7 Series Devices Memory Interface Solutions 提供了定制core和接口的细节。

相比之前的版本,Xilinx 7系列的memory solution接口优化包括:

- 更高性能

- 新的硬件模块被用于physical layer,PHASER_IN,PHASE_OUT,PHY control block,与IO FIFOs。

- 基于硬件block的管脚输出。

- controller与user接口,1/4的时钟周期。

二、在vivado中运用MIG(Memory interface generator)

MIG(Memory interface generator)内存接口生成器,是一个IPcore,运用vivado定制用于调用DDR。

这部分介绍如何生成MIG的IPcore,并且用vivado设计套件进行实现。

2.1 打开vivado,创建新工程,创建RTL工程,添加源,添加IP,添加constraints。

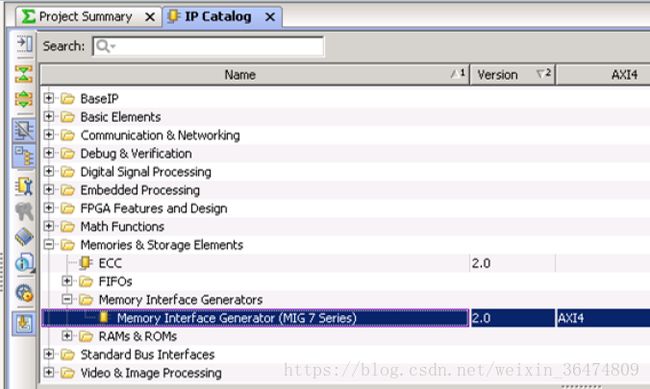

2.2 点击IP catalog,找到目录Memory&storage elements>Memory Interface Generators,找到相应的IP,或者直接搜索MIG

三、定制与生成MIG core

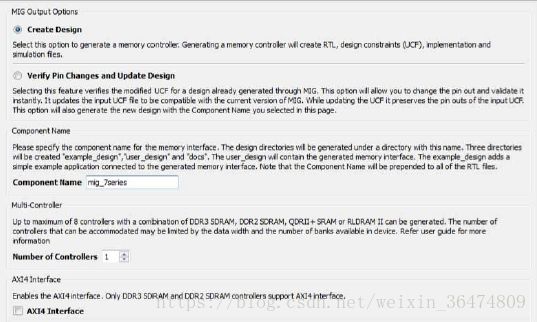

3.1 点击create Design来创建相应的memory controller design,输入Component Name。DDR2与DDR3的SDRAM设计需要支持memory-mapped的AXI4接口,AXI4接口只能用verilog语言来实现。如果需要AXI4接口,就需要在此之前勾选verilog选项。

3.2 Pin compatible FPGAs(没什么用),可兼容的FPGA板子,在这里勾选可以兼容的板子。

3.3 创建7 series FPGA DDR3 Memory Controller Block design

3.3.1 选择DDR3 SDRAM

3.3.2 Controller Options

- Frequency:控制器的操作频率。

- PHY to controller frequency ratio: Physical layer(memory)与controller的时钟频率的比率。2:1可以降低memory的接口的频率,4:1可以提升数据传输率。

- VCCAUX_IO:电压,基于周期与频率。MIG一般需要2。0V, 1.8V和2.0V可以被用于低频率。

- Memory type与memory part:内存的类型与模块。

- Data Width:基于之前的memory type做出选择。

- Data mask:这个选项会分配data mask管脚。这个选项通常是用于AXI设计,并且通常是灰的,即不能被选择。对于AXI而言,RMW(read modify write)是支持的。

- Ordering与Memory details:改善总线性能,显示相应的内存具体信息。

3.3.3 创建定制模块

3.3.4 AXI参数选项

address width与address ID width:引用XPS时,地址与ID宽度会自动的由XPS选择并且不会显示。

Base与High address:创建系统地址空间,必须为2的次方,并且至少4KB。Base addres必须与内存空间的大小对齐。

narrow burst support: 不选此项可以让AXI4总线去掉用于AXI narrow burst的logic,从而节省资源和改善时间。XPS会自动的根据AXI主线来决定是否narrow burst。

Arbitation Scheme:在读地址与写地址之间选择arbitration scheme

四、其他选项

4.1 Setting DDR3 memory parameter option,FPGA options,DCI description,Bank selection

DDR2和DDR3只支持(BL8)burst length 8. Bankselection

Digitally controlled impedance(DCI)数字控制电阻

此部分细节过多,过于繁琐,且涉及过多硬件部分,不太能理解。

4.2 summary

这页给出相应的core selection的总结,关于接口参数,IP catalog选项,FPAG与相应的工程。

后面两个为PCB information与Design Notes

五、vivado集成设计环境

5.1 点击generate之后,generate output products窗口生成,OOC settings窗口弹出。

5.2 点击OOC settings,

5.3 MIG core需要遵从Hierarchial design