STM32F4学习笔记13——ADC part1

ADC 简介

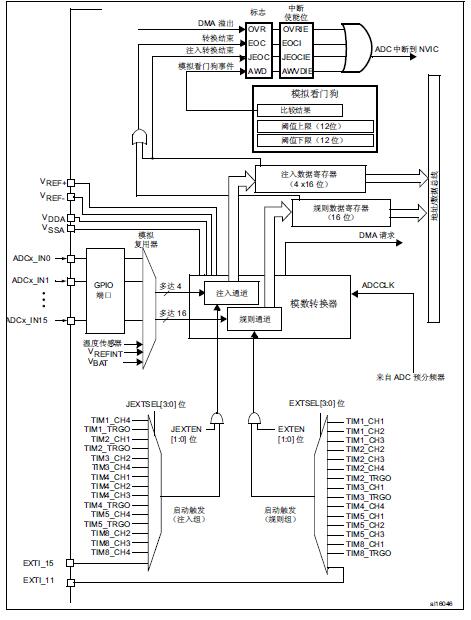

12 位 ADC 是逐次趋近型模数转换器。它具有多达 19 个复用通道,可测量来自 16 个外部 源、两个内部源和 VBAT 通道的信号。这些通道的 A/D 转换可在单次、连续、扫描或不连续 采样模式下进行。ADC 的结果存储在一个左对齐或右对齐的 16 位数据寄存器中。

ADC 具有模拟看门狗特性,允许应用检测输入电压是否超过了用户自定义的阈值上限或下限。

ADC 主要特性

● 可配置 12 位、10 位、8 位或 6 位分辨率

● 在转换结束、注入转换结束以及发生模拟看门狗或溢出事件时产生中断

● 单次和连续转换模式

● 用于自动将通道 0 转换为通道“n”的扫描模式

● 数据对齐以保持内置数据一致性

● 可独立设置各通道采样时间

● 外部触发器选项,可为规则转换和注入转换配置极性

● 不连续采样模式

● 双重/三重模式(具有 2 个或更多 ADC 的器件提供)

● 双重/三重 ADC 模式下可配置的 DMA 数据存储

● 双重/三重交替模式下可配置的转换间延迟

● ADC 转换类型(参见数据手册)

● ADC 电源要求:全速运行时为 2.4 V 到 3.6 V,慢速运行时为 1.8 V

● ADC 输入范围:VREF— VIN VREF+

● 规则通道转换期间可产生 DMA 请求

图 34 显示了 ADC 的框图。

注意:VREF— 如果可用(取决于封装),则必须将其连接到 VSSA

ADC 功能说明

ADC 开关控制

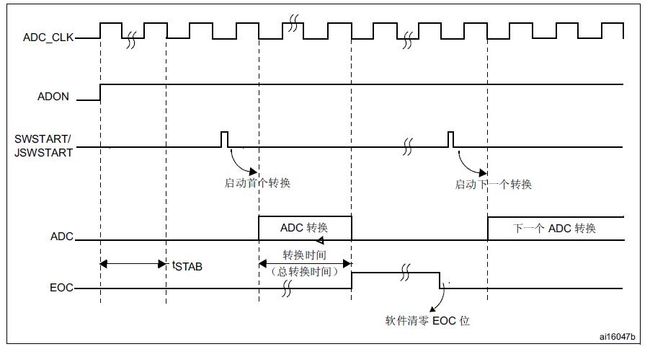

可通过将 ADC_CR2 寄存器中的 ADON 位置 1 来为 ADC 供电。首次将 ADON 位置 1 时, 会将 ADC 从掉电模式中唤醒。

SWSTART 或 JSWSTART 位置 1 时,启动 AD 转换。

可通过将 ADON 位清零来停止转换并使 ADC 进入掉电模式。在此模式下,ADC 几乎不耗电 (只有几 μA)。

ADC 时钟

ADC 具有两个时钟方案:

● 用于模拟电路的时钟:ADCCLK,所有 ADC 共用

此时钟来自于经可编程预分频器分频的 APB2 时钟,该预分频器允许 ADC 在 fPCLK2/2、/4、/6 或 /8 下工作。有关 ADCCLK 的最大值,请参见数据手册。

● 用于数字接口的时钟(用于寄存器读/写访问)

此时钟等效于 APB2 时钟。可以通过 RCC APB2 外设时钟使能寄存器 (RCC_APB2ENR)分别为每个 ADC 使能/禁止数字接口时钟。

通道选择

有 16 条复用通道。可以将转换分为两组:规则转换和注入转换。每个组包含一个转换序列, 该序列可按任意顺序在任意通道上完成。例如,可按以下顺序对序列进行转换:ADC_IN3、ADC_IN8、ADC_IN2、ADC_IN2、ADC_IN0、ADC_IN2、ADC_IN2、ADC_IN15。

● 一个规则转换组最多由 16 个转换构成。必须在 ADC_SQRx 寄存器中选择转换序列的规

则通道及其顺序。规则转换组中的转换总数必须写入 ADC_SQR1 寄存器中的 L[3:0] 位。

● 一个注入转换组最多由 4 个转换构成。必须在 ADC_JSQR 寄存器中选择转换序列的注入

通道及其顺序。注入转换组中的转换总数必须写入 ADC_JSQR 寄存器中的 L[1:0] 位。

如果在转换期间修改 ADC_SQRx 或 ADC_JJSQR 寄存器,将复位当前转换并向 ADC 发送一个新的启动脉冲,以转换新选择的组。

温度传感器、VREFINT 和 VBAT 内部通道

● 对于 STM32F40x 和 STM32F41x 器件,温度传感器内部连接到通道 ADC1_IN16。

内部参考电压 VREFINT 连接到 ADC1_IN17。

● 对于 STM23F42x 和 STM32F43x 器件,温度传感器内部连接到与 VBAT 共用的通道ADC1_IN18。一次只能选择一个转换(温度传感器或 VBAT)。同时设置了温度传感器和 VBAT 转换时,将只进行 VBAT 转换。

内部参考电压 VREFINT 连接到 ADC1_IN17。

VBAT 通道连接到通道 ADC1_IN18。该通道也可转换为注入通道或规则通道。

注意:温度传感器、VREFINT 和 VBAT 通道只在主 ADC1 外设上可用。

单次转换模式

在单次转换模式下,ADC 执行一次转换。CONT 位为 0 时,可通过以下方式启动此模式:

● 将 ADC_CR2 寄存器中的 SWSTART 位置 1(仅适用于规则通道)

● 将 JSWSTART 位置 1(适用于注入通道)

● 外部触发(适用于规则通道或注入通道)

完成所选通道的转换之后:

● 如果转换了规则通道:

— 转换数据存储在 16 位 ADC_DR 寄存器中

— EOC(转换结束)标志置 1

— EOCIE 位置 1 时将产生中断

● 如果转换了注入通道:

— 转换数据存储在 16 位 ADC_JDR1 寄存器中

— JEOC(注入转换结束)标志置 1

— JEOCIE 位置 1 时将产生中断

然后,ADC 停止。

连续转换模式

在连续转换模式下,ADC 结束一个转换后立即启动一个新的转换。CONT 位为 1 时,可通过外部触发或将 ADC_CR2 寄存器中的 SWSTRT 位置 1 来启动此模式(仅适用于规则通道)。

每次转换之后:

● 如果转换了规则通道组:

— 上次转换的数据存储在 16 位 ADC_DR 寄存器中

— EOC(转换结束)标志置 1

— EOCIE 位置 1 时将产生中断

注意:无法连续转换注入通道。连续模式下唯一的例外情况是,注入通道配置为在规则通道之后自动转换(使用 JAUTO 位),请参见自动注入一节。

时序图

ADC 在开始精确转换之前需要一段稳定时间 tSTAB。ADC 开始转换并经过 15 个 时钟周期后,EOC 标志置 1,转换结果存放在 16 位 ADC 数据寄存器中。

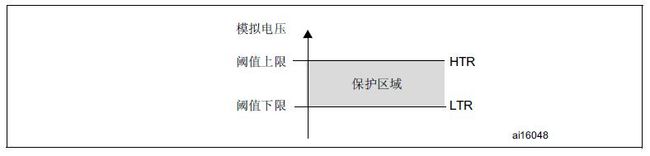

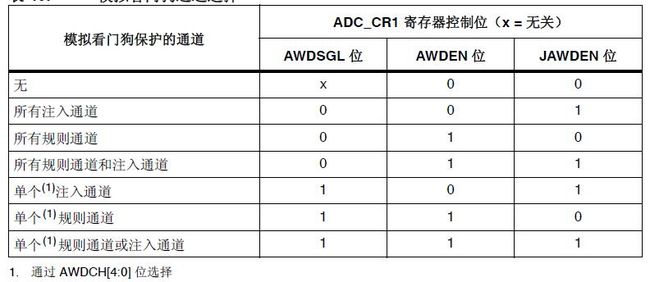

模拟看门狗

如果 ADC 转换的模拟电压低于阈值下限或高于阈值上限,则 AWD 模拟看门狗状态位会置 1。这些阈值在 ADC_HTR 和 ADC_LTR 16 位寄存器的 12 个最低有效位中进行编程。可以 使用 ADC_CR1 寄存器中的 AWDIE 位使能中断。

阈值与 ADC_CR2 寄存器中的 ALIGN 位的所选对齐方式无关。在对齐之前,会将模拟电压 与阈值上限和下限进行比较。

下表介绍了应如何配置 ADC_CR1 寄存器才能在一个或多个通道上使能模拟看门狗。

扫描模式

此模式用于扫描一组模拟通道。

通过将 ADC_CR1 寄存器中的 SCAN 位置 1 来选择扫描模式。将此位置 1 后,ADC 会扫描 在 ADC_SQRx 寄存器(对于规则通道)或 ADC_JSQR 寄存器(对于注入通道)中选择的 所有通道。为组中的每个通道都执行一次转换。每次转换结束后,会自动转换该组中的下一个通道。如果将 CONT 位置 1,规则通道转换不会在组中最后一个所选通道处停止,而是再 次从第一个所选通道继续转换。

如果将 DMA 位置 1,则在每次规则通道转换之后,均使用直接存储器访问 (DMA) 控制器将 转换自规则通道组的数据(存储在 ADC_DR 寄存器中)传输到 SRAM。

在以下情况下,ADC_SR 寄存器中的 EOC 位置 1:

● 如果 EOCS 位清零,在每个规则组序列转换结束时

● 如果 EOCS 位置 1,在每个规则通道转换结束时

从注入通道转换的数据始终存储在 ADC_JDRx 寄存器中。

注入通道管理

触发注入

要使用触发注入,必须将 ADC_CR1 寄存器中的 JAUTO 位清零。

1.通过外部触发或将 ADC_CR2 寄存器中的 SWSTART 位置 1 来启动规则通道组转换。

2. 如果在规则通道组转换期间出现外部注入触发或者 JSWSTART 位置 1,则当前的转换 会复位,并且注入通道序列会切换为单次扫描模式。

3. 然后,规则通道组的规则转换会从上次中断的规则转换处恢复。

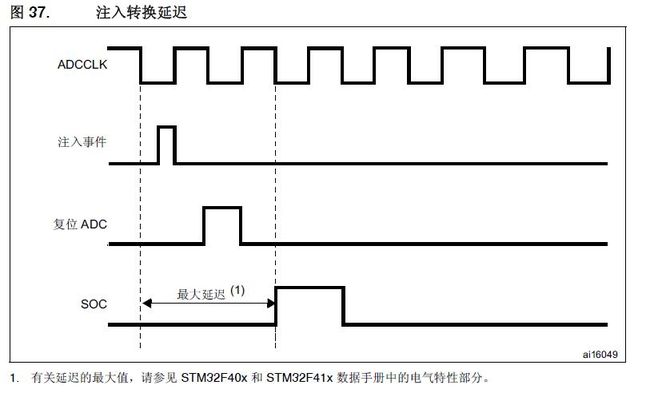

如果在注入转换期间出现规则事件,注入转换不会中断,但在注入序列结束时会执行规则序列。图 37 显示了相应的时序图。

注意:使用触发注入时,必须确保触发事件之间的间隔长于注入序列。例如,如果序列长度为 30 个 ADC 时钟周期(即,采样时间为 3 个时钟周期的两次转换),则触发事件的最小间隔不能 小于 31 个 ADC 时钟周期。

自动注入

如果将 JAUTO 位置 1,则注入组中的通道会在规则组通道之后自动转换。这可用于转换最 多由 20 个转换构成的序列,这些转换在 ADC_SQRx 和 ADC_JSQR 寄存器中编程。

在此模式下,必须禁止注入通道上的外部触发。

如果 CONT 位和 JAUTO 位均已置 1,则在转换规则通道之后会继续转换注入通道。

注意:不能同时使用自动注入和不连续采样模式。

不连续采样模式

规则组

可将 ADC_CR1 寄存器中的 DISCEN 位置 1 来使能此模式。该模式可用于转换含有 n (n 8) 个转换的短序列,该短序列是在 ADC_SQRx 寄存器中选择的转换序列的一部分。可通过写 入 ADC_CR1 寄存器中的 DISCNUM[2:0] 位来指定 n 的值。

出现外部触发时,将启动在 ADC_SQRx 寄存器中选择的接下来 n 个转换,直到序列中的所 有转换均完成为止。通过 ADC_SQR1 寄存器中的 L[3:0] 位定义总序列长度。

示例:

n = 3,要转换的通道 = 0、1、2、3、6、7、9、10

第 1 次触发:转换序列 0、1、2

第 2 次触发:转换序列 3、6、7

第 3 次触发:转换序列 9、10 并生成 EOC 事件

第 4 次触发:转换序列 0、1、2

注意:在不连续采样模式下转换规则组时,不会出现翻转。

转换完所有子组后,下一个触发信号将启动第一个子组的转换。在上述示例中,第 4 次触发 重新转换了第 1 个子组中的通道 0、1 和 2。

注入组

可将 ADC_CR1 寄存器中的 JDISCEN 位置 1 来使能此模式。在出现外部触发事件之后,可 使用该模式逐通道转换在 ADC_JSQR 寄存器中选择的序列。

出现外部触发时,将启动在 ADC_JSQR 寄存器中选择的下一个通道转换,直到序列中的所 有转换均完成为止。通过 ADC_JSQR 寄存器中的 JL[1:0] 位定义总序列长度。

示例:

n = 1,要转换的通道 = 1、2、3

第 1 次触发:转换通道 1 、2、3

第 2 次触发:转换通道 2

第 3 次触发:转换通道 3 并生成 EOC 和 JEOC 事件

第 4 次触发:通道 1

注意:转换完所有注入通道后,下一个触发信号将启动第一个注入通道的转换。在上述示例中,第 4 次触发重新转换了第 1 个注入通道。

不能同时使用自动注入和不连续采样模式。

不得同时为规则组和注入组设置不连续采样模式。只能针对一个组使能不连续采样模式。

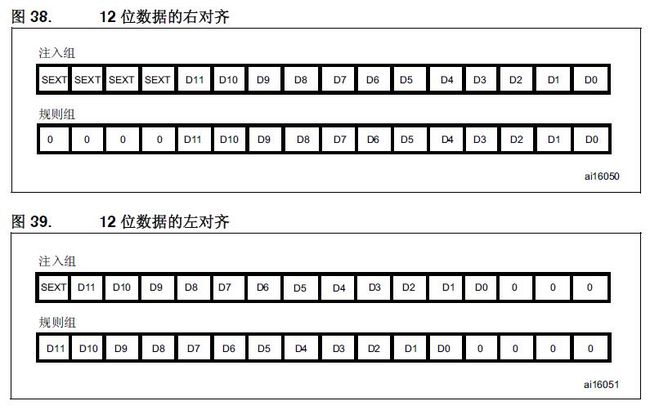

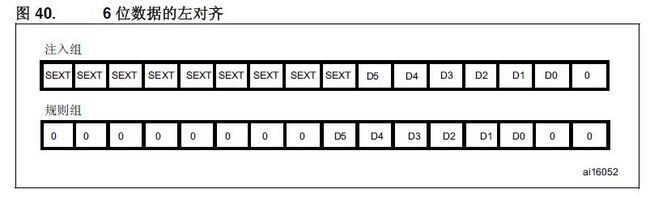

数据对齐

ADC_CR2 寄存器中的 ALIGN 位用于选择转换后存储的数据的对齐方式。可选择左对齐和 右对齐两种方式,如图 38 和图 39 所示。

注入通道组的转换数据将减去 ADC_JOFRx 寄存器中写入的用户自定义偏移量,因此结果可 以是一个负值。SEXT 位表示扩展的符号值。

对于规则组中的通道,不会减去任何偏移量,因此只有十二个位有效。

特例:采用左对齐时,数据基于半字进行对齐,除了分辨率设置为 6 位时。分辨率设置为 6 位 时,数据基于字节进行对齐,如图 40 所示。

可独立设置各通道采样时间

ADC 会在数个 ADCCLK 周期内对输入电压进行采样,可使用 ADC_SMPR1 和 ADC_SMPR2 寄存器中的 SMP[2:0] 位修改周期数。每个通道均可以使用不同的采样时间进行采样。

总转换时间的计算公式如下:

Tconv = 采样时间 + 12 个周期

示例:

ADCCLK = 30 MHz 且采样时间 = 3 个周期时:

Tconv = 3 + 12 = 15 个周期 = 0.5 μs(APB2 为 60 MHz 时)

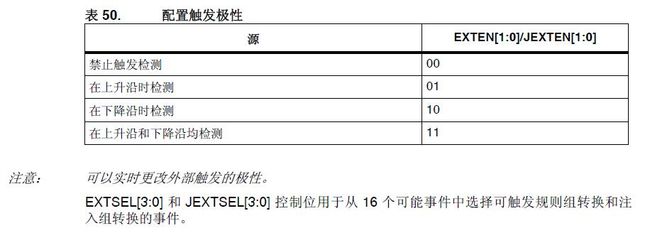

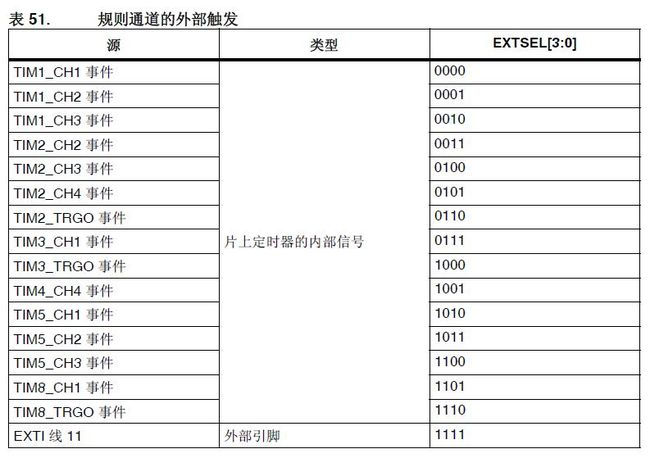

外部触发转换和触发极性

可以通过外部事件(例如,定时器捕获、EXTI 中断线)触发转换。如果 EXTEN[1:0] 控制位 (对于行规转换)或 JEXTEN[1:0] 位(对于注入转换)不等于“0b00”,则外部事件能够 以所选极性触发转换。表 50 提供了 EXTEN[1:0] 和 JEXTEN[1:0] 值与触发极性之间的对应 关系。

可通过将 ADC_CR2 寄存器中的 SWSTART(对于规则转换)或 JSWSTART(对于注入转 换)位置 1 来产生软件源触发事件。

可通过注入触发中断规则组转换。

注意:可以实时更改触发选择。不过,当更改触发选择时,会在 1 个 APB 时钟周期的时间范围内禁 止触发检测。这是为了避免在转换期间出现意外检测。

快速转换模式

可通过降低 ADC 分辨率来执行快速转换。RES 位用于选择数据寄存器中可用的位数。每种 分辨率的最小转换时间如下:

● 12 位:3 + 12 = 15 ADCCLK 周期

● 10 位:3 + 10 = 13 ADCCLK 周期

● 8 位:3 + 8 = 11 ADCCLK 周期

● 6 位:3 + 6 = 9 ADCCLK 周期

使用 DMA

由于规则通道组只有一个数据寄存器,因此,对于多个规则通道的转换,使用 DMA 非常有 帮助。这样可以避免丢失在下一次写入之前还未被读出的 ADC_DR 寄存器中的数据。

在使能 DMA 模式的情况下(ADC_CR2 寄存器中的 DMA 位置 1),每完成规则通道组中的 一个通道转换后,都会生成一个 DMA 请求。这样便可将转换的数据从 ADC_DR 寄存器传输 到用软件选择的目标位置。

尽管如此,如果数据丢失(溢出),则会将 ADC_SR 寄存器中的 OVR 位置 1 并生成一个中 断(如果 OVRIE 使能位已置 1)。随后会禁止 DMA 传输并且不再接受 DMA 请求。在这种 情况下,如果生成 DMA 请求,则会中止正在进行的规则转换并忽略之后的规则触发。随后 需要将所使用的 DMA 流中的 OVR 标志和 DMAEN 位清零,并重新初始化 DMA 和 ADC, 以将需要的转换通道数据传输到正确的存储器单元。只有这样,才能恢复转换并再次使能数据传输。注入通道转换不会受到溢出错误的影响。

在 DMA 模式下,当 OVR = 1 时,传送完最后一个有效数据后会阻止 DMA 请求,这意味着 传输到 RAM 的所有数据均被视为有效。

在最后一次 DMA 传输(DMA 控制器的 DMA_SxRTR 寄存器中配置的传输次数)结束时:

● 如果将 ADC_CR2 寄存器中的 DDS 位清零,则不会向 DMA 控制器发出新的 DMA 请求

(这可避免产生溢出错误)。不过,硬件不会将 DMA 位清零。必须将该位写入 0 然后

写入 1 才能启动新的传输。

● 如果将 DDS 位置 1,则可继续生成请求。从而允许在双缓冲区循环模式下配置 DMA。

要在使用 DMA 时将 ADC 从 OVR 状态中恢复,请按以下步骤操作:

1.重新初始化 DMA(调整目标地址和 NDTR 计数器)

2. 将 ADC_SR 寄存器中的 ADC OVR 位清零

3. 触发 ADC 以开始转换。

在不使用 DMA 的情况下管理转换序列

如果转换过程足够慢,则可使用软件来处理转换序列。在这种情况下,必须将 ADC_CR2 寄 存器中的 EOCS 位置 1,才能使 EOC 状态位在每次转换结束时置 1,而不仅是在序列结束 时置 1。当 EOCS = 1 时,会自动使能溢出检测。因此,每当转换结束时,EOC 都会置 1, ᅠ ᅠ

并且可以读取 ADC_DR 寄存器。溢出管理与使用 DMA 时的管理相同。

要在 EOCS 位置 1 时将 ADC 从 OVR 状态中恢复,请按以下步骤操作:

1.将 ADC_SR 寄存器中的 ADC OVR 位清零

2. 触发 ADC 以开始转换。

在不使用 DMA 和溢出检测的情况下进行转换

ADC 在转换一个或多个通道时不是每次都读取数据的情况下,这可能会很有用(例如,存在 模拟看门狗时)。为此,必须禁止 DMA (DMA = 0) 并且仅在序列结束 (EOCS = 0) 时才将 ᅠ ᅠ ᅠ ᅠ

EOC 位置 1。在此配置中,溢出检测已禁止。