DC综合简单总结

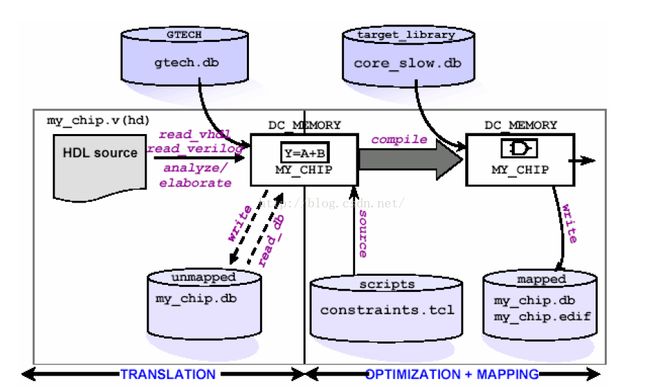

综合分为三个部分:Synthesis= Translate + Mapping + Optimization。

1、 Translate是将 HDL转化为GTECH库元件组成的逻辑电路,这步通过read_verilog进行(verilog代码),verilog代码被读入后,将会被自动translate。GTECH是独立于工艺库的通用元件库。这个时候可以用write -output ./unmapped/design.db输出unmapped的二进制文件。

2、 Mapping是将GTECH映射到某一指定的工艺库,此网表包含了工艺参数。

3、 Optimization 是将网表按设计者的约束进行优化。

后两步通过加约束后使用compile命令完成。完成optimization之后可以通过

write -format verilog -hierarchy -output./p_syn_sim/design.v

写成verilog格式的网表,这是map后的结果。如果输出的是顶层模块,所有模块的module都会输出到同一个文件中。顶层模块一般在最后。

Sysnopsys提供了一个例子,在下面的位置:

$synopsys/doc/syn/guidelines

首先,可以在.synopsys_dc.setup里面设置库的位置和一些环境变量。里面包括所使用库的位置,DC涉及到几个库文件:

1、 工艺库(target_library):工艺库是综合后电路网表要最终映射到的库,读入的HDL代码首先由synopsys自带的GTECH库转换成Design Compiler内部交换的格式,然后经过映射到工艺库和优化生成门级网表。工艺库他是由Foundary提供的,一般是.db的格式。这种格式是DC认识的一种内部文件格式,不能由文本方式打开。.db格式可以由文本格式的.lib转化过来,他们包含的信息是一致的。

2、 链接库(link_library):link_library设置模块或者单元电路的引用,对于所有DC可能用到的库,我们都需要在link_library中指定,其中也包括要用到的IP。此处还要将search_path加进来,这样才能找到.db文件,否则只会搜索当前目录。

3、 符号库 (symbol_library):symbol_library是定义了单元电路显示的Schematic的库。用户如果想启动design_analyzer或design_vision来查看、分析电路时需要设置symbol_library。符号库的后缀是.sdb,加入没有设置,DC会用默认的符号库取代。

4、 综合库(synthetic_library):在初始化DC的时候,不需要设置标准的DesignWare库standard.sldb用于实现Verilog描述的运算符,对于扩展的DesignWare,需要在synthetic_library中设置,同时需要在link_library中设置相应的库以使得在链接的时候DC可以搜索到相应运算符的实现。

读入设计:

read –format verilog[db、vhdl etc.] file //dcsh的工作模式

read_db file.db //TCL工作模式读取DB格式

read_verilog file.v //TCL工作模式读取verilog格式

read_vhdlfile.vhd //TCL工作模式读取VHDL格式

读取源程序的另外一种方式是配合使用analyze命令和elaborate命令:analyze是分析HDL的源程序并将分析产生的中间文件存于work(用户也可以自己指定)的目录下;elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体,缺省情况下,elaborate读取的是work目录中的文件。

Link命令:

当读取完所要综合的模块之后,需要使用link命令将读到Design Compiler存储区中的模块或实体连接起来,如果在使用link命令之后,出现unresolved designreference的警告信息,需要重新读取该模块,或者在.synopsys_dc.setup文件中添加link_library,告诉DC到库中去找这些模块,同时还要注意search_path中的路径是否指向该模块或单元电路所在的目录。

约束:

约束面积:set_max_area 100

单位:定义这个单位有三种可能的标准:一种是将一个二输入与非门的大小作为单位1;第二种是以晶体管的数目规定单位;第三种则是根据实际的面积(平方微米等等)。至于设计者具体用的是哪种单位,可以通过下面的一个小技巧得到——即先综合一个二输入与非门,用report_area看他的面积是多少,如果是1,则是按照第一种标准定义的;如果是4,则是第二种标准;如果是其他的值,则为第三种标准。

约束时序:

DC可以处理的是同步时序电路。

模块内部的,寄存器之间的逻辑的约束(X):

Creat_clock –period 10[get_ports clk]

Set_dont_touch_network[get_clocks clk]

第一句话将clk定义为时钟,并定义周期为10ns,因此可以约束寄存器间组合逻辑的critical path不能大于10ns,进行约束。第二句的意义为,不要在综合的时候对时钟树进行优化,因为时钟树有特别的办法进行综合。

set_output_delay -max 3.0 -clockclk [all_outputs] 用于约束输入段的组合逻辑,在第一个寄存器前的部分(N)。

set_input_delay -max 3.0 -clockclk [all_inputs] 用于约束输出的组合逻辑,最后一个寄存器以后的部分(S)。

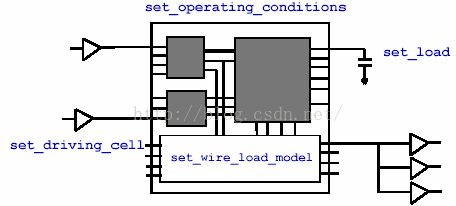

约束环境:

set_load 2[all_outputs] 设置输出的负载(这里的单位也是由Foundry提供,具体的单位,可以通过report_lib命令查看,一般而言是pf。)

set_driving_cell-lib_cell FD1 [all_inputs]设置输入的负载,此处设置为一个模块来驱动。

set_operating_conditions–max slow –min fast????????????????设置工作条件。在默认情况下,Design Compiler不会自动指定工作条件,我们可以先通过report_lib命令来列出在当前的工艺库里提供了哪几种工作条件。然后指定需要用到的工作条件,在做建立时间分析的时候需要用到最差情况的条件。

setauto_wire_load_selection true 设置线负载模型,它是也是由Foundry提供的。Foundry根据其他用这个工艺流片的芯片的连线延时进行统计,从而得到这个值。此处设置的是自动选择。也可以设置成其他,如:set_wire_load_model–name 160KGATES。还可以通过set_wire_load_mode enclosed设置负载模式。

在定义完环境属性之后,我们可以使用下面的几个命令检查约束是否施加成功——

check_timing检查设计是否有路径没有加入约束

check_design检查设计中是否有悬空管脚或者输出短接的情况

write_script将施加的约束和属性写出到一个文件中,可以检查这个文件看看是否正确

DesignWare选择:DW选择是结构级优化的一个很主要的特点,在这个阶段DC能够根据设计者施加的时序或者面积的约束在DW的不同实现方式中找到它认为最佳的实现方案。比如一个加法运算,DC会根据约束选择最合适的加法器,如lookahead还是选择carry bypass。

Characterize命令:

用characterize这个命令将约束条件传递到子模块,然后保存这些传递下来的约束条件,再用这样条件对这个子模块再重新编译。

报告(report):

report_timing 生成时序报告

综合策略:

Top-down 方式的层次化编译策略有这样三个步骤:

1. 读入整个设计。

2. 处理多次引用的模块;基于设计要求在顶层加约束条件以及定义属性。

3. 编译。

Bottom-up有下面七个步骤:

1. 独立编译子模块,用估计的驱动和负载。用一个缺省的脚本文件来估计驱动和负载。

2. 将整个编译好的设计读入。

3. 对一个子模块用characterize命令来获得端口信息。

4. 用write_script来将这些传递过来的信息保存下来。

5. 清除内存,将前面得到传递信息的子模块调入并且用保存下来的脚本文件重新编译。为了这些描述信息能够应用,需要将db格式的文件读入。

6. 将这个新编译的子模块和其余的子模块全部再次调入DC。

7. 选择另外一个子模块,重复3~7步,直到所有的子模块都重新编译过了。