高速串行总线系列(3)GTX/GTH 物理层结构分析

文章目录

-

- 前言

- Transceiver总览

-

- MGT BANK

- QUAD

- GTX CHANNEL

-

- TRANSMITTER

-

- FPGA TX Interface

- TX 8B/10B Encoder

- TX Gearbox

- TX Buffer

- TX Pattern Generator

- TX Polarity Control

- RECEIVER

-

- RX Out-of-Band Signaling

- RX CDR

- RX Fabric Clock Output Control

- RX Polarity Control

- RX Pattern Checker

- RX 8B/10B Decoder

- RX Buffer Bypass

- RX Elastic Buffer

- RX Clock Correction

- FPGA RX Interface

- Pin Description and Design Guidelines

- Use Model

前言

GTX/GTH是FPGA内部的高速串行收发器,后面为了方便,统称为MGT以及多吉比特收发器,它是集成在FPGA芯片内的可配置硬核资源,与FPGA内部的OSERDESE2以及ISERDESE2原语类似,均可实现数据的串行转换以及并串转换,但与OSERDESE2等相比,GTX结构更加复杂,增加了适应高速串行传输的优化措施,例如8B/10B编码等。

我们熟知的各种高速串行总线,例如SRIO,Aurora,以及PCIE等都是以MGT为物理层实现的,因此,了解MGT是很有必要的。

本文以数据手册UG476为参考资源,来简单记录下对MGT硬核资源的理解。

Transceiver总览

Transceiver,顾名思义,就是收发器,固然包含Transmitter以及Receiver,也即常见的TX以及RX。

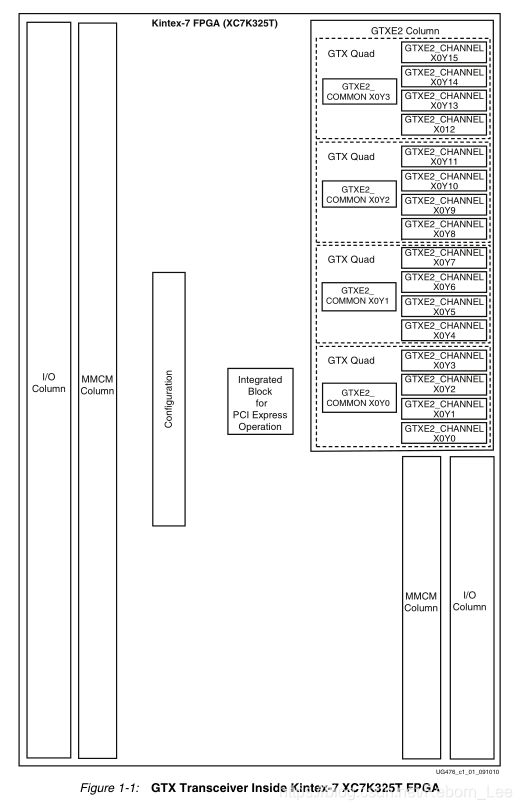

以K7系列的FPGA芯片,XC7K325t为例,来看看其物理结构。

MGT BANK

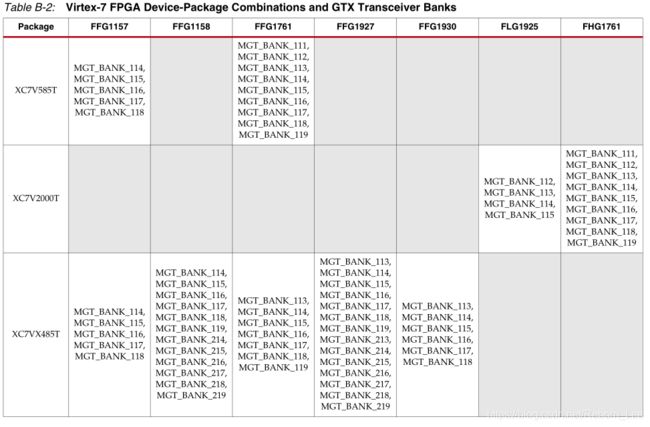

下图为XC7K325t内部的MGT Bank分布图,和上表对应,可知应该是封装为ffg900的fpga:

上图为GTX收发器的布局总览图。

可见,XC7K325t这种FPGA包含4个MGT Bank,每个Bank上有4个GTX通道(GTXE2_CHANNEL)。

每个MGT Bank的内部结构图如下:

QUAD

四个GTX通道以及一个GTXE2_COMMON原语一起称为一个QUAD,或者叫做Q。GTXE2_COMMON包含一个QPLL。

包含2个专用的差分时钟输入BUFFER(IBUFDS_GTE2),还有4个GTX通道(GTXE2_CHANNEL),和一个QPLL模块(GTXE2_COMMON)。

QPLL(QUAL PLL)与CPLL(Channel PLL)为GTX的时钟电路,分别为4个GTX通道提供时钟。

可以选择QPLL或者CPLL之一为所使用的GTX CHANNEL提供时钟,如下为使用QPLL的情况:

具体参见数据手册。

GTX CHANNEL

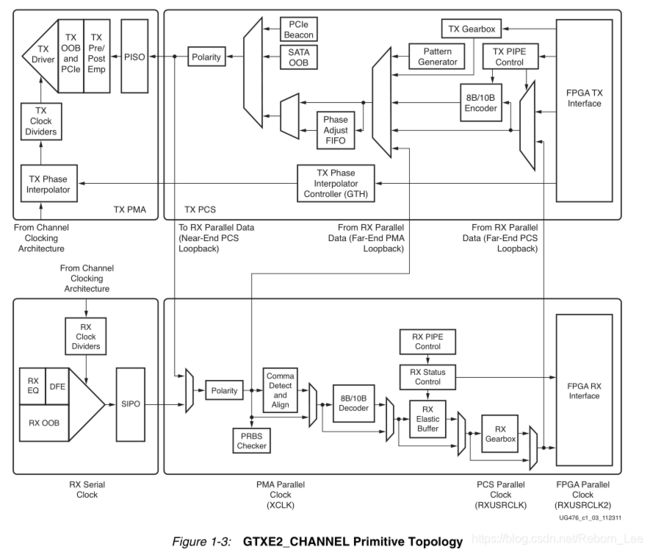

GTX通道是专用的高速数据传输通道,包含了数据传输的发送端以及接收端,是一种全双工结构,设计的具体电路功能有串并转换,8B/10B编码等。

GTXE2_CHANNEL原语的结构图如下:

下面简单分析下GTX通道中的功能部件:

TRANSMITTER

TX部分的电路功能框图如下:

其内部各功能模块的简单介绍如下:

FPGA TX Interface

这是与用户逻辑进行交互的并行数据接口,用户逻辑设计好之后通过与此交互,一直到最后转换成高速串行比特流发送出去。

用户数据TXDATA在用户时钟TXUSRCLK2上升沿采样,支持的端口宽度为2byte、4byte以及8byte。

并行时钟TXUSRCLK2大小由TX线速率决定。第二并行时钟TXUSRCLK必须由发送端内部PCS逻辑提供。

这里提到了名词PCS,那就顺带着后面也要提及的PMA一起交代下:

- 在Xilinx的高速串行收发器中,包含PMA(物理媒介适配层)和PCS(物理编码子层)两个子层其中PMA子层主要用于串行化和解串,PCS主要包括线路编码和CRC校验编码。

- PMA子层中集成了SERDES,发送和接收缓冲,时钟发生器及时钟恢复电路。SERDES是一个串并转换器,负责FPGA中本地的32位并行数据(也可以是16位或8位)与RocketIO接口的串行数据之间的转换。

下面的内容推荐详细阅读数据手册理解。

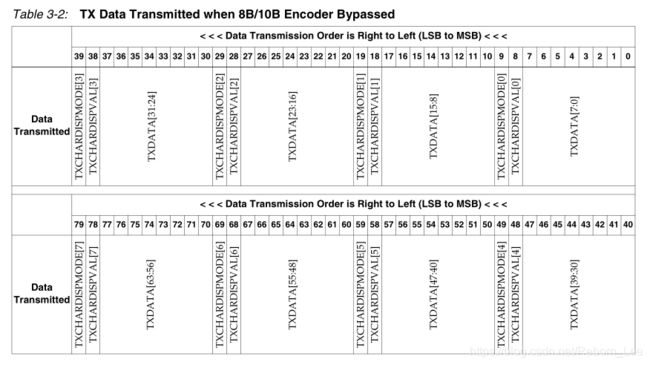

当忽略8B/10B编码时,下面显示了要发送的数据顺序等信息。

这样看不舒服,那就转过来看:

这里不得不介绍下TX interface端的时钟关系,TX Interface端包含两个并行时钟,TXUSECLK以及TXUSRCLK2。

TXUSRCLK上面已经介绍过了,是为发送端PCS逻辑提供的时钟。

TXUSRCLK2是所有数据进入Tx端的主要同步时钟。

如何产生上述时钟呢?

见下图:

上图中TXOUTCLK来自于差分输入时钟MGTREFCLK0[P/N]或者MGTREFCLK1[P/N],以及TXOUTCLKSEL为011,选择TXPLLREFCLK_DIV1路径得到,如下图:

TX 8B/10B Encoder

有关8B/10B 的原理在其他篇博客里面已经介绍过:

8B/10B编码技术

8B/10B编码在内嵌在GTX通道内的,不消耗FPGA逻辑资源,可以在定制GTX的时候根据需要选择。

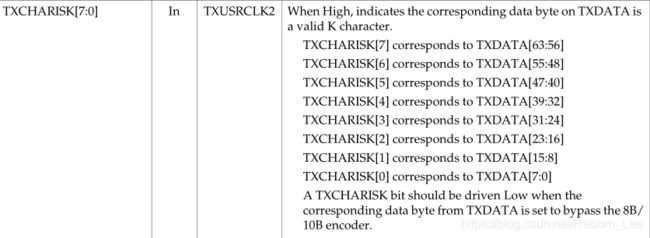

本以为这样就算结束了介绍,但是不得不说的一个关键信号:TX 8B/10B Encoder Ports

当你尝试过使用GTX IP核的时候,会意识到这个信号的重要性。

TX Gearbox

一些高速接口协议要求使用64B/66B编码,就会使用到TX Gearbox这个结构,这里暂不多说。

TX Buffer

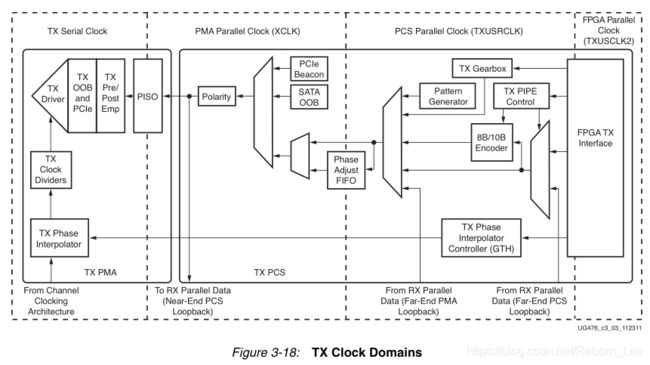

GTX收发器TX路径有两个内部并行时钟域用于PCS,分别为PMA并行时钟XCLK以及TXUSRCLK时钟域。

为了发送数据,XCLK速率必须匹配TXUSRCLK,二者之间的相位差必须处理好,如下图,为这两个时钟的时钟域示意图:

GTX收发器解决这种跨时钟域的问题的方法有两种,一种是常见的TX buffer,类似于异步FIFO,一种是TX Phase alignment电路,用于解决TXUSRCLK和XCLK时钟域之间的跨时钟域传输问题。

两者使用一种,是必须的。

TX Pattern Generator

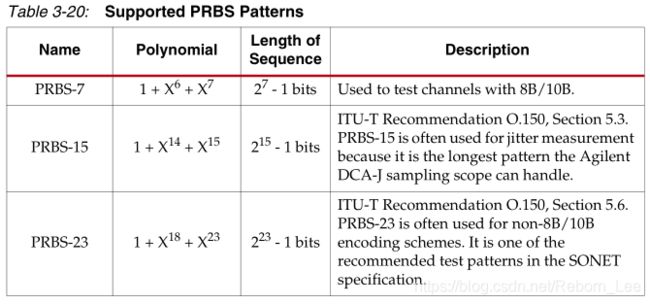

伪随机位序列(PRBS)通常用于测试高速链路的信号完整性。 这些序列看起来是随机的,但是具有可用于测量链接质量的特定属性。 GTX / GTH收发器码型生成器模块可以生成表3-20中列出的几种行业标准的PRBS码型。

TX Polarity Control

如果在PCB上意外交换了TXP和TXN差分走线,则GTX / GTH收发器TX传输的差分数据将反转。 一种解决方案是在串行化和传输之前反转并行数据,以抵消差分对上的反向极性。 可以通过光纤用户界面中的TXPOLARITY输入来访问TX极性控件。 它被驱动为高电平以反转输出数据的极性。

RECEIVER

RX部分的电路框图如下:

Receiver与Transmitter是一对,共同称为Transceiver,Receiver由PCS和PMA构成,这里在此解释下这两个名词,加深印象:

- 在Xilinx的高速串行收发器中,包含PMA(物理媒介适配层)和PCS(物理编码子层)两个子层其中PMA子层主要用于串行化和解串,PCS主要包括线路编码和CRC校验编码。

高速串行数据从电路板上的走线流入GTX / GTH收发器RX的PMA,PCS,最后进入FPGA逻辑。

RX Out-of-Band Signaling

GTX / GTH接收器提供了对串行ATA(SATA)和串行连接SCSI(SAS)规范中描述的带外(OOB)序列的解码的支持,并支持PCI Express规范中描述的信标。 GTX / GTH接收器对SATA / SAS OOB信号的支持包括:对OOB信号状态进行解码所需的模拟电路,以及对SATA / SAS COM序列的OOB信号突发进行解码的状态机。

可见,RX OOB这个功能模块是和SATA以及PCIE协议相关的,这里不细说。

RX CDR

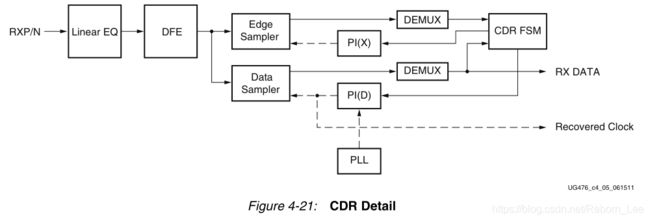

每个GTXE2_CHANNEL / GTHE2_CHANNEL收发器中的RX时钟数据恢复(CDR)电路从传入的数据流中提取恢复的时钟和数据。 图4-21说明了CDR块的体系结构。 为了清楚起见,时钟路径以虚线显示。

GTXE2_CHANNEL / GTHE2_CHANNEL收发器采用相位旋转器CDR架构。 传入数据首先经过接收器均衡阶段。 边缘和数据采样器捕获均衡后的数据。 数据采样器捕获的数据被馈送到CDR状态机和下游收发器模块。

GTXE2_CHANNEL / GTHE2_CHANNEL收发器采用相位旋转器CDR架构。 传入数据首先经过接收器均衡阶段。 边缘和数据采样器捕获均衡后的数据。 数据采样器捕获的数据被馈送到CDR状态机和下游收发器模块。

CDR状态机使用来自边缘和数据采样器的数据来确定输入数据流的相位并控制相位插值器(PI)。 边缘采样器的相位被锁定到数据流的过渡区域,而数据采样器的相位位于数据眼的中间。

CPLL或QPLL为相位插值器提供基本时钟。 相位内插器又会产生精细,均匀间隔的采样相位,以允许CDR状态机具有精细的相位控制。 CDR状态机可以跟踪输入数据流,这些输入数据流可能与本地PLL参考时钟有频率偏移。

RX Fabric Clock Output Control

Fabric这个词很难翻译成中文,要体会这个词,在FPGA中很常用,可以理解成某某组成,例如FPGA的Fabric,就是FPGA的结构,例如LUT等。

这里的RX Fabric呢?自己体会下:

下图是RX中相关的时钟逻辑详情:

具体看看UG476.

我目前只知道有这个东西存在就OK。

RX Polarity Control

如果PCB连线或者原理图上RXP以及PXN连线接反了,也就是二者交换了,还有办法补救吗?

看如下描述:

- 如果在板上意外交换了RXP和RXN差分走线,则GTX / GTH收发器RX接收到的差分数据将反转。 GTX / GTH收发器RX允许在SIPO之后对PCS中的并行字节进行反转,以抵消差分对上的反向极性。 极性控制功能使用RXPOLARITY输入,该信号从结构用户界面驱动为高电平以反转极性。

如果需要将RXP和RXN的极性颠倒,则RXPOLARITY可以拉高。

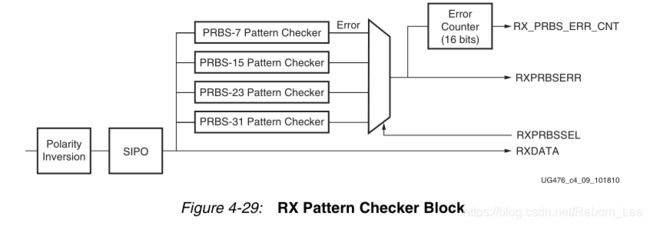

RX Pattern Checker

GTX / GTH接收器包括一个内置的PRBS检查器(见图4-29)。 可以将该检查器设置为检查四种行业标准PRBS模式之一。 该检查器是自同步的,并在comma对齐或解码之前处理传入的数据。 此功能可用于测试通道的信号完整性。

RX 8B/10B Decoder

如果RX接收的数据是8B / 10B编码的,则必须对其进行解码。 GTX / GTH收发器在GTX / GTH收发器TX中具有内置的8B / 10B编码器,在GTX / GTH收发器RX中具有8B / 10B解码器,在数据路径上包括四个1字节的8B / 10B解码器模块。 解码数据而不消耗FPGA资源。

RX Buffer Bypass

绕过RX弹性缓冲区是7系列GTX / GTH收发器的高级功能。 RX相位对齐电路用于调整SIPO并行时钟域和RX XCLK域之间的相位差,以实现从SIPO到PCS的可靠数据传输。 它还通过调整RXUSRCLK来执行RX延迟对齐,以补偿温度和电压变化。 组合的RX相位和延迟对齐可以由GTX / GTH收发器自动执行,也可以由用户手动控制。 图4-49显示了XCLK和RXUSRCLK域,表4-39显示了缓冲和相位对齐之间的权衡。

当使用RX恢复的时钟作为RXUSRCLK和RXUSRCLK2的源时,可以绕过RX弹性缓冲区以减少等待时间。 绕过RX弹性缓冲区时,通过RX数据路径的等待时间很短并且是确定的,但是时钟校正和通道绑定不可用。

图4-40显示了RX相位对齐如何允许绕过RX弹性缓冲器。 在RX相位对齐之前,在SIPO并行时钟域和RX XCLK域之间没有保证的相位关系。 使用RX相位对齐时,RX XCLK配置为使用RXUSRCLK。 RX相位对齐从CDR(XCLK)中选择RX恢复时钟的相移版本,以便SIPO并行时钟和RX XCLK之间没有明显的相位差。 当使用RX buffer bypass 并将RXSLIDE_MODE设置为AUTO或PMA时,RXOUTCLK必须来自SIPO恢复时钟,而RXUSRCLK必须来自RXOUTCLK。

RX Elastic Buffer

GTX / GTH收发器RX数据路径具有PCS中使用的两个内部并行时钟域:PMA并行时钟域(XCLK)和RXUSRCLK域。 为了接收数据,PMA并行速率必须足够接近RXUSRCLK速率,并且必须解决两个域之间的所有相位差。 图4-49显示了两个并行时钟域:XCLK和RXUSRCLK。

GTX / GTH收发器包括一个RX弹性缓冲区,用于解决XCLK和RXUSRCLK域之间的差异。 也可以通过使用来自收发器的RX恢复时钟来驱动RXUSRCLK,并在绕过RX缓冲器时调整其相位以匹配XCLK,以匹配两个域的相位(请参见第242页的RX缓冲器旁路)。

GTX / GTH收发器包括一个RX弹性缓冲区,用于解决XCLK和RXUSRCLK域之间的差异。 也可以通过使用来自收发器的RX恢复时钟来驱动RXUSRCLK,并在绕过RX缓冲器时调整其相位以匹配XCLK,以匹配两个域的相位(请参见第242页的RX缓冲器旁路)。

所有RX数据路径必须使用以下方法之一。 每种方法的成本和收益如表4-39所示。

RX Clock Correction

RX弹性缓冲区旨在桥接两个不同的时钟域RXUSRCLK和XCLK,这是从CDR恢复的时钟。 即使RXUSRCLK和XCLK以相同的时钟频率运行,也总是存在很小的频率差。 由于XCLK和RXUSRCLK并不完全相同,因此,如果不加以纠正,则可能会累积该差值,从而导致RX弹性缓冲区最终发生上溢或下溢。 为了进行校正,每个GTX / GTH收发器TX会定期发送一个或多个特殊字符,并根据需要允许GTX / GTH收发器RX在RX弹性缓冲区中删除或复制。 通过在RX弹性缓冲区太满时删除字符并在RX弹性缓冲区太空时复制字符,接收器可以防止上溢或下溢。

FPGA RX Interface

对应于TX Interface,暂时不多介绍。

Pin Description and Design Guidelines

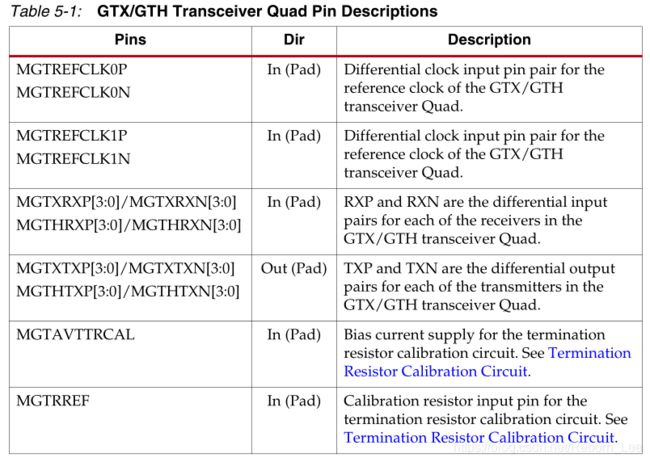

不同型号、不同封装的FPGA具有不同数量的MGT Bank,但共同的是,每一个MGT Bank有一个Quad,包括四个GTX CHANNEL,如下是一个MGT Bank上的管脚介绍:

供电链接方式:

Use Model

这个就不介绍了,最后还有一些参考的附录,请移步UG476,可以判断你究竟要使用那一个通道,如何和你的原理图对应。