[转] XILINX_FPGA内DCM全局时钟的使用详解

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。

图1.Xilinx FPGA全局时钟分配树结构

针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

Virtex- 4系列FPGA利用1.2V、90nm三栅极氧化层技术制造而成,与前一代器件相比,具备灵活的时钟解决方案,多达80个独立时钟与20个数字时钟管理 器,差分全局时钟控制技术将歪斜与抖动降至最低。以全铜工艺实现的全局时钟网络,加上专用时钟缓冲与驱动结构,从而可使全局时钟到达芯片内部所有的逻辑可配置单元,且I/O单元以及块RAM的时延和抖动最小,可满足高速同步电路对时钟触发沿的苛刻需求。

在FPGA设计中,FPGA全局时钟路径 需要专用的时钟缓冲和驱动,具有最小偏移和最大扇出能力,因此最好的时钟方案是由专用的全局时钟输入引脚驱动的单个主时钟,去钟控设计项目中的每一个触发器。只要可能就应尽量在设计项目中采用全局时钟,因为对于一个设计项目来说,全局时钟是最简单和最可预测的时钟。

在软件代码中,可通过调用原语 IBUFGP来使用全局时钟。IBUFGP的基本用法是:

IBUFGP U1(.I(clk_in), .O(clk_out));

全局时钟网络对FPGA设计性能的影响很大,所以本书在第11章还会更深入、更全面地介绍全局时钟网络以及相关使用方法。

DCM模块的使用

1.DCM模块的组成和功能介绍

数 字时钟管理模块(Digital ClockManager,DCM)是基于Xilinx的其他系列器件所采用的数字延迟锁相环(DLL,Delay Locked Loop)模块。在时钟的管理与控制方面,DCM与DLL相比,功能更强大,使用更灵活。DCM的功能包括消除时钟的延时、频率的合成、时钟相位的调整等 系统方面的需求。DCM的主要优点在于:①实现零时钟偏移(Skew),消除时钟分配延迟,并实现时钟闭环控制;②时钟可以映射到PCB上用于同步外部芯 片,这样就减少了对外部芯片的要求,将芯片内外的时钟控制一体化,以利于系统设计。对于DCM模块来说,其关键参数为输入时钟频率范围、输出时钟频率范 围、输入/输出时钟允许抖动范围等。

DCM共由四部分组成,如图2所示。其中最底层仍采用成熟的DLL模块;其次分别为数字频率合成器(DFS,Digital Frequency Synthesizer)、数字移相器(DPS,Digital Phase Shifter)和数字频谱扩展器(DSS,Digital Spread Spectrum)。不同的芯片模块的DCM输入频率范围是不同的,例如:。

图2 DCM功能块和相应的信号

1)DLL模块

DLL 主要由一个延时线和控制逻辑组成。延时线对时钟输入端CLKIN产生一个延时,时钟分布网线将该时钟分配到器件内的各个寄存器和时钟反馈端CLKFB;控 制逻辑在反馈时钟到达时采样输入时钟以调整二者之间的偏差,实现输入和输出的零延时,如图3所示。具体工作原理是:控制逻辑在比较输入时钟和反馈时钟的偏 差后,调整延时线参数,在输入时钟后不停地插入延时,直到输入时钟和反馈时钟的上升沿同步,锁定环路进入“锁定”状态,只要输入时钟不发生变化,输入时钟 和反馈时钟就保持同步。DLL可以被用来实现一些电路以完善和简化系统级设计,如提供零传播延迟,低时钟相位差和高级时钟区域控制等。

图3 DLL简单模型示意图

在Xilinx芯片中,典型的DLL标准原型如图4所示,其管脚分别说明如下:

图4 Xilinx DLL的典型模型示意图

CLKIN(源时钟输入):DLL输入时钟信号,通常来自IBUFG或BUFG。

CLKFB(反馈时钟输入):DLL时钟反馈信号,该反馈信号必须源自CLK0或CLK2X,并通过IBUFG或BUFG相连。

RST(复位):控制DLL的初始化,通常接地。

CLK0(同频信号输出):与CLKIN无相位偏移;CLK90与CLKIN 有90度相位偏移;CLK180与CLKIN 有180度相位偏移;CLK270与CL KIN有270度相位偏移。

CLKDV(分频输出):DLL输出时钟信号,是CLKIN的分频时钟信号。DLL支持的分频系数为1.5,2,2.5,3,4,5,8 和16。

CLK2X(两倍信号输出):CLKIN的2倍频时钟信号。

LOCKED(输出锁存):为了完成锁存,DLL可能要检测上千个时钟周期。当DLL完成锁存之后,LOCKED有效。

在FPGA 设计中,消除时钟的传输延迟,实现高扇出最简单的方法就是用DLL,把CLK0 与CLKFB相连即可。利用一个DLL可以实现2倍频输出,如图5所示。利用两个DLL 就可以实现4倍频输出,如图6所示。

图5Xilinx DLL 2倍频典型模型示意图

图6 Xilinx DLL 4倍频典型模型示意图

2)数字频率合成器

DFS 可以为系统产生丰富的频率合成时钟信号,输出信号为CLKFB和CLKFX180,可提供输入时钟频率分数倍或整数倍的时钟输出频率方案,输出频率范围为1.5~320 MHz(不同芯片的输出频率范围是不同的)。这些频率基于用户自定义的两个整数比值,一个是乘因子(CLKFX_ MULTIPLY),另外一个是除因子(CLKFX_ DIVIDE),输入频率和输出频率之间的关系为:

比如取CLKFX_MULTIPLY = 3,CLKFX_DIVIDE = 1,PCB上源时钟为100 MHz,通过DCM3倍频后,就能驱动时钟频率在300 MHz的FPGA,从而减少了板上的时钟路径,简化板子的设计,提供更好的信号完整性。

3) 数字移相器

DCM 具有移动时钟信号相位的能力,因此能够调整I/O信号的建立和保持时间,能支持对其输出时钟进行0度、90度、180度、270度的相移粗调和相移细调。 其中,相移细调对相位的控制可以达到1%输入时钟周期的精度(或者50 ps),并且具有补偿电压和温度漂移的动态相位调节能力。对DCM输出时钟的相位调整需要通过属性控制PHASE_SHIFT来设置。PS设置范围为 -255到+255,比如输入时钟为200MHz,需要将输出时钟调整+ 0.9 ns的话,PS =(0.9ns/ 5ns)?56 = 46。如果PHASE_ SHIFT值是一个负数,则表示时钟输出应该相对于CLKIN向后进行相位移动;如果PHASE_SHIFT是一个正值,则表示时钟输出应该相对于 CLKIN向前进行相位移动。

移相用法的原理图与倍频用法的原理图很类似,只用把CLK2X输出端的输出缓存移到CLK90、CLK180或者CLK270端即可。利用原时钟和移相时钟与计数器相配合也可以产生相应的倍频。

4) 数字频谱合成器

Xilinx 公司第一个提出利用创新的扩频时钟技术来减少电磁干扰(EMI)噪声辐射的可编程解决方案。最先在FPGA中实现电磁兼容的EMIControl技术,是 利用数字扩频技术(DSS)通过扩展输出时钟频率的频谱来降低电磁干扰,减少用户在电磁屏蔽上的投资。数字扩频(DSS)技术通过展宽输出时钟的频谱,来减少EMI和达到FCC要求。这一特点使设计者可极大地降低系统成本,使电路板重新设计的可能性降到最小,并不再需要昂贵的屏蔽,从而缩短了设计周期。

2.DCM模块IP Core的使用

例:在ISE中调用DCM模块,完成50MHz时钟信号到75MHz时钟信号的转换。

1) 在源文件进程中,双击“Create New Source”;然后在源文件窗口,选择“IP (CoreGen & Architecture Wizard)”,输入文件名“my_dcm”;再点击“Next”,在选择类型窗口中,“FPGA Features and Design –>Clocking ->Virtex-4”,然后选择“Single DCM ADV v9.1i”,如图7所示。

图7 新建DCM模块IP Core向导示意图

<2> 点击“Next”,“Finish”进入Xilinx 时钟向导的建立窗口,如图8所示。ISE默认选中CLK0和 LOCKED这两个信号,用户根据自己需求添加输出时钟。在“Input Clock Frequency”输入栏中敲入输入时钟的频率或周期,单位分别是MHz和ns,其余配置保留默认值。为了演示,这里添加了CLKFX 信号,并设定输入时钟为单端信号,频率为50MHz,其余选项保持默认值。

图8 DCM模块配置向导界面

<3> 点击“Next”,进入时钟缓存窗口,如图9所示。默认配置为DCM输出添加全局时钟缓存以保证良好的时钟特性。如果设计全局时钟资源,用户亦可选择“Customizebuffers”自行编辑输出缓存。一般选择默认配置即可。

图9 DCM模块时钟缓存配置向导界面

<4> 点击“Next”,进入时钟频率配置窗口,如图10所示。键入输出频率的数值,或者将手动计算的分频比输入。最后点击 “Next”,“Finish”即可完成DCM模块IP Core的全部配置。本例直接键入输出频率为75MHz即可。

图10 指定 DCM 模块的输出频率

<5> 经过上述步骤,即可在源文件进程中看到“my_dcm.xaw”文件。剩余的工作就是在设计中调用该DCM IP Core,其例化代码如下:

module dcm_top(

CLKIN_IN,

RST_IN,

CLKFX_OUT,

CLKIN_IBUFG_OUT,

CLK0_OUT,

LOCKED_OUT);

input CLKIN_IN;

input RST_IN;

output CLKFX_OUT;

output CLKIN_IBUFG_OUT;

output CLK0_OUT;

output LOCKED_OUT;

mydcm dcm1(

.CLKIN_IN(CLKIN_IN),

.RST_IN(RST_IN),

.CLKFX_OUT(CLKFX_OUT),

.CLKIN_IBUFG_OUT(CLKIN_IBUFG_OUT),

.CLK0_OUT(CLK0_OUT),

.LOCKED_OUT(LOCKED_OUT)

);

endmodule<6> 上述代码经过综合Synplify Pro综合后,得到的RTL级结构图如图11所示。

图11 DCM模块的RTL结构示意图

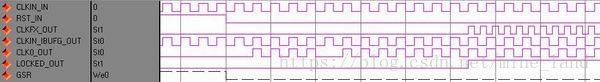

上 述代码经过ModelSim仿真后,其局部仿真结果如图12所示。从中可以看出,当LOCKED_OUT信号变高时,DCM模块稳定工作,输出时钟频率 CLKFX_OUT为输入时钟CLK_IN频率的1.5倍,完成了预定功能。需要注意的是,复位信号RST_IN是高有效。

图12 DCM的仿真结果示意图

在 实际中,如果在一片FPGA内使用两个DCM,那么时钟从一个clk输入,再引到两个DCM的clk_in。这里,在DCM模块操作时,需要注意两点:首先,用CoreGen生成DCM模块的时候,clk_in源是内部的,不能直接连接到管脚,需要添加缓冲器;其次,手动例化一个IBUFG,然后把 IBUFG的输入连接到两个DCM的clk_in。通常,如果没有设置clk_in 源为内部的,而是完全按照单个DCM的使用流程,就会造成clk_in信号有多个驱动。此时,ISE不能做到两个DCM模块输出信号的相位对齐,只能做到 一个DCM的输出是相位对齐的。而时钟管脚到两个DCM的路径和DCM输出的路径都有不同的延时,因此如果用户对相位还有要求,就需要自己手动调整DCM 模块在芯片中的位置。

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第1张图片](http://img.e-com-net.com/image/info8/2f35ef9807754d42ad0dc2ea77d8c9fb.jpg)

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第2张图片](http://img.e-com-net.com/image/info8/3d191eca7f874bb9b867628ffc5c53e4.jpg)

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第3张图片](http://img.e-com-net.com/image/info8/b8b85632b5374646ad912a3792cd8604.jpg)

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第4张图片](http://img.e-com-net.com/image/info8/c6ff7dcca7124cc5b55da7cd0ce2e791.jpg)

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第5张图片](http://img.e-com-net.com/image/info8/f736c4cffba64fea84c17443996506e2.jpg)

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第6张图片](http://img.e-com-net.com/image/info8/eae622157fd24e5e9f64e3f21a600511.jpg)

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第7张图片](http://img.e-com-net.com/image/info8/7997e30dddbf453fba89ffc501c63b53.jpg)

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第8张图片](http://img.e-com-net.com/image/info8/807c34f2b0e24af4bba8d3bd9388eb8b.jpg)

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第9张图片](http://img.e-com-net.com/image/info8/7f17dec8219943d7a0a81da60d165539.jpg)

![[转] XILINX_FPGA内DCM全局时钟的使用详解_第10张图片](http://img.e-com-net.com/image/info8/ff8941cf904f401882a84174a13fe7aa.jpg)