基于DE2-115 FPGA开发板的VGA显示

基于DE2-115 FPGA开发板的VGA显示

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

完成一行扫描的时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描的时间称为垂直扫描时间,其倒数称为场频率,即刷新一屏的频率,常见的有60Hz,75Hz等等。标准的VGA显示的场频60Hz,行频31.5KHz。

行场消隐信号:是针对老式显像管的成像扫描电路而言的。电子枪所发出的电子束从屏幕的左上角开始向右扫描,一行扫完需将电子束从右边移回到左边以便扫描第二行。在移动期间就必须有一个信号加到电路上,使得电子束不能发出。不然这个回扫线会破坏屏幕图像的。这个阻止回扫线产生的信号就叫作消隐信号,场信号的消隐也是一个道理。

显示带宽:带宽指的显示器可以处理的频率范围。如果是60Hz刷新频率的VGA,其带宽达640x480x60=18.4MHz,70Hz的刷新频率1024x768分辨率的SVGA,其带宽达1024x768x70=55.1MHz。

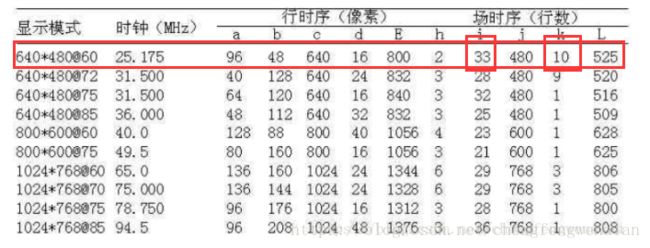

时钟频率:以[email protected](60Hz)为例,每场对应525个行周期(525=10+2+480+33),其中480为显示行。每场有场同步信号,该脉冲宽度为2个行周期的负脉冲,每显示行包括800点时钟,其中640点为有效显示区,每一行有一个行同步信号,该脉冲宽度为96个点时钟。由此可知:行频为525*59.94=31469Hz,需要点时钟频率:525*800*59.94约25MHz.

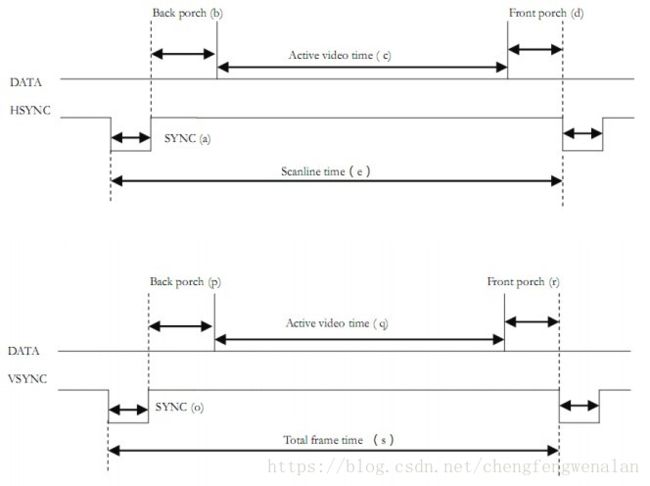

图1.VGA时序图

VESA中定义行时序和场时序都需要同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四部分。VGA工业标准显示模式要求:行同步,场同步都为负极性,即同步脉冲要求是负脉冲。

由VGA的行时序可知:没一行都有一个负极性行同步脉冲(Sync a),是数据行的结束标志,同时也是下一行的开始标志。在同步脉冲之后为显示后沿(Back porch b),在显示时序段(Display interval c)显示器为亮的过程,RGB数据驱动一行上的每一个像素点,从而显示一行。在一行的最后为显示前沿(Front porch d)。在显示时间段(Display interval c)之外没有图像投射到屏幕是插入消隐信号。同步脉冲(Sync a)、显示后沿(Back porch b)和显示前沿(Front porch d)都是在行消隐间隔内(Horizontal Blanking Interval),当消隐有效时,RGB信号无效,屏幕不显示数据。

VGA的场时序与行时序基本一样,每一帧的负极性脉冲(Sync a)是一帧的结束标志,同时也是下一帧的开始标志。而显示数据是一帧的所有行数据。

下面以640*480@60Hz分辨率威力详细讲解VGA时序:

图2.VGA参数

只需要看第一行就可以了。

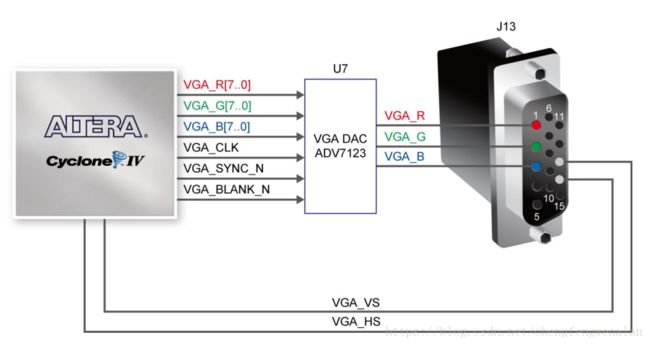

图3.FPGA与VGA的连接图

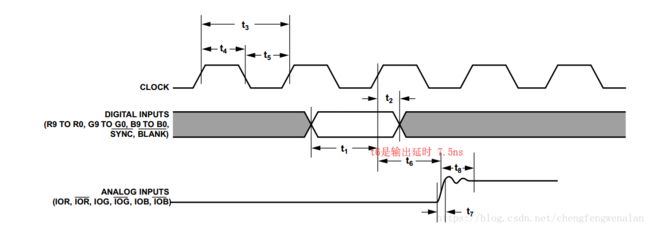

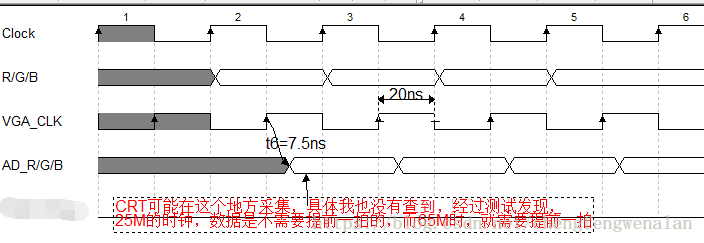

图4.ADV7123时序图

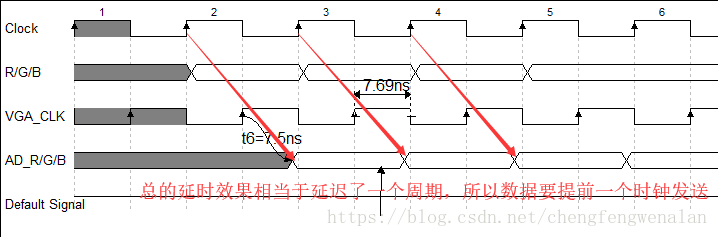

DE2-115开发板是使用了AD的,与其他的使用电阻网络的有点不一样,因为他的数据先经过AD,而AD输出延时t6=7.5ns,当使用640*480@60Hz时,VGA带宽为640*480*60=25MHz,周期为40ns,因为AD的时钟是经过取反的,而40/2>7.5ns,所以不需要提前一个时钟发数据,但是1024*768@60Hz时,带宽变为了65MHz,周期为15.38ns,15.38/2已经很接近7.5ns了,所以这时需要提前一个时钟发数据,具体还是以自己测试为准,提前一个时钟不行就试试二个。

图5. 640*480@60Hz,25MHz时序图

图6. 1024*768@60Hz,65MHz时序图

具体的要不要提前一个时钟发送还是以实际为准,具体测试方法如下

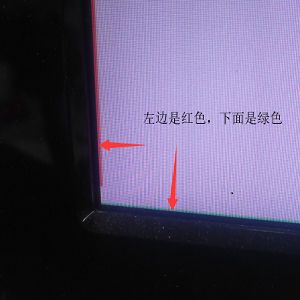

写个测试程序,只显示边框(上下左右都只显示一个像素),如果边框都有那就正确的,少了一边就说明是错了,效果图如下:

图7.边框定位测试法

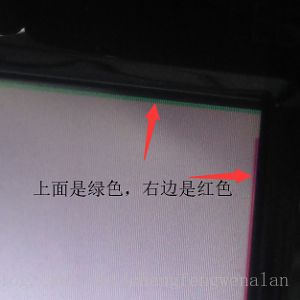

本实验的最终是要显示一个四周20像素的红色边框,然后中间为100*100的绿色方块,测试发现竖线要比横线粗,所以100*100的方块看起来居然是长方形。这个可能跟分辨率有关,因为电脑显示器是建议1920*1080的,而我们使用的640*480,

这个就是DVI,HDMI里的支持的分辨率:1920/1080=1.77777,

这个是VGA协议里有的分辨率:1024/768=800/600=640/480=1.33333<1.77777,

所以竖线会看起来比横线粗,查了一些资料都没有找到有说这个事情的,这些都是我个人理解,欢迎有详细知道的能留言说一下,效果图如下:

图8.最终实验效果图

源码链接:https://github.com/wenalan123/VGA