Threadx 中断处理-ARM

文章目录

-

- ARM寄存器

- ARM两种状态

- ARM 工作模式

- 工作模式切换

- ARM 异常

- ARM异常处理

基于arm v7分析Threadx操作系统的中断处理。

ARM寄存器

ARM V7体系结构共有37个32位寄存器,其中r0-r12为通用寄存器;r13(sp)为栈寄存器,指向栈顶,向下(低地址)增长;r14(LR)是连接寄存器,用来函数调用时存储返回地址,或者中断异常点;r15(pc)为程序计数器,存储当前执行指令下一条指令地址;CPSR寄存器保存程序执行时处理器状态信息;SPSR寄存器用来存储CPSR备份值。

ARM有多种工作模式,每种模式下有自己特殊寄存器,例如,每种模式下都有自己的SPSR物理寄存器。

任何模式下都可以访问R0-R12和CSPR寄存器,只有一份物理寄存器。FIQ模式下可以访问R8_fiq-R14_fiq, 是物理寄存器。

每种模式下(除了sys模式)都有自己的物理寄存器SP,LR,只能在自己的模式下访问对应寄出器。模式切换是,SPSR寄存器用来备份CPSR寄存器。

例如:当前ARM从User模式切换到FIQ模式时,CPSR寄出器值备份到SPSR_fiq,使用SP_fiq,LR_fiq作为当前模式下程序执行的栈寄存器和链接寄存器。

总之,R0-R12为通用寄存器,每种模式都可以访问,每种模式下又有自己的栈寄存器和链接寄存器,以及特有寄存器。

每种模式下特有寄存器好处时,模式切换时可以使用之前寄存器中存储的值,不需要保存或恢复,加快模式切换速率。

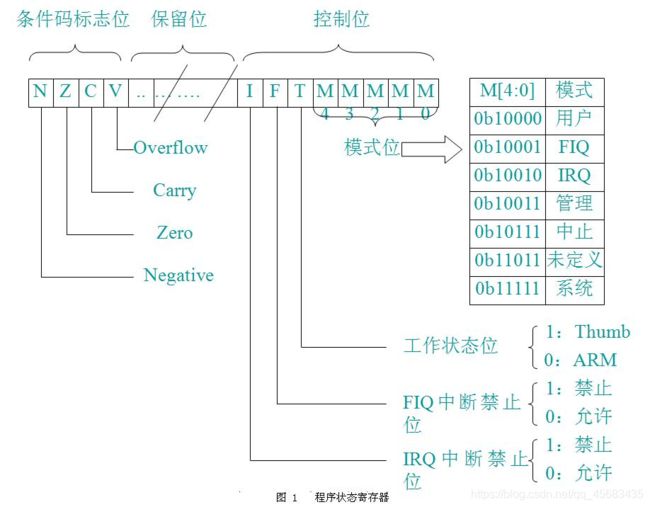

** CPSR寄存器 **

所有处理器模式下都可访问当前程序状态寄存器CPSR。CPSR中包含条件码标志、中断禁止位、当前处理器模式以及其他状态和控制信息。在每种异常模式下都有一个对用的程序状态寄存器SPSR。当异常出现时,SPSR用于保存CPSR的状态,以便异常返回后恢复异常发生时的工作状态。

条件码标志

N、Z、C、V,最高4位称为条件码标志。ARM的大多数指令可以条件执行的,即通过检测这些条件码标志来决定程序指令如何执行。

各个条件码的含义如下:

N:在结果是有符号的二进制补码情况下,如果结果为负数,则N=1;如果结果为非负数,则N=0。

Z:如果结果为0,则Z=1;如果结果为非零,则Z=0。

C:其设置分一下几种情况:

对于加法指令(包含比较指令CMN),如果产生进位,则C=1;否则C=0。

对于减法指令(包括比较指令CMP),如果产生借位,则C=0;否则C=1。

对于有移位操作的非法指令,C为移位操作中最后移出位的值。

对于其他指令,C通常不变。

V:对于加减法指令,在操作数和结果是有符号的整数时,如果发生溢出,则V=1;如果无溢出发生,则V=0;对于其他指令,V通常不发生变化。

ARM两种状态

ARM状态:32位,ARM状态执行字对齐的32位ARM指令。

Thumb状态,16位,执行半字对齐的16位指令。

用Bx Rn指令来进行两种状态的切换:

其中Bx是跳转指令,而Rn是寄存器(1个字,32位),如果Rn的位0为1,则进入Thumb状态;如果Rn的位为0,这进入ARM状态。

原 因:ARM指令的后两位始终为0,没有用,而Thumb指令的后一位始终为0,没有用,因此采用位0来表示ARM指令与Thumb指令的切换标志位。

注:ARM和Thumb两种状态之间的切换不影响处理器的工作模式和寄存器的内容。

ARM处理器在处理异常时,不管处理器处于什么状态,则都将切换到ARM状态。

ARM 工作模式

ARM体系架构有7种工作模式,CPSR的低5位定义了当前的处理器模式。

| M[4:0] | 模式 | 意义 |

|---|---|---|

| 10000 | User | 用户模式 |

| 10001 | FIQ | FIQ快速中断模式 |

| 10001 | IRQ | IRQ普通中断模式 |

| 10011 | SVC | 管理模式 |

| 10111 | ABORT | 中止模式 |

| 11011 | UND | 未定义模式 |

| 11111 | SYS | 系统模式 |

用户模式 User

用户模式通常用来执行普通程序,在改模式下不能访问系统寄存器,所以这种模式通常被操作系统来执行应用程序。

快速中断模式 FIQ

快速中断模式用来处理fiq类型中断,通常是高频或低延迟中断。FIQ模式有特有的r8_fiq-r12_fiq等寄存器,因此可以不用存储和恢复自身的环境就可以执行,能够提升处理中断的速度。

普通中断模式 IRQ

大部分中断在普通中断模式处理,中断发生时不能自动备份某些寄存器内容,需要软件在堆栈中备份寄存器,再判断中断来源并处理中断。

管理模式 SVC

管理模式运行操作系统的保护模式,高权限,可以操作系统寄存器。linux系统中内核运行在SVC模式,中断发生后进入FIQ或IRQ,保存好环境会切换到SVC模式,继续进行中断处理。

这里多说一下,linux内核可以运行在SVC,FIQ, IRQ模式,因为从程序角度看,底层代码包括BSP都属于内核,而应用程序运行在用户模式,权限低。

Threadx应用程序和操作系统都运行在SVC模式。

中止模式 ABORT

中止模式用来处理指令预取中止和数据内存访问中止,中止的地址保存在r14_abt中。

未定义模式 UND

未定义模式用来处理由未定义的指令产生的错误,未定义指令保存在r14_abt中。

系统模式 SYS

运行具有特权的任务

工作模式切换

ARM 异常

异常是指是指打断当前处理流程的异步事件或错误条件。发生异常后,ARM处理器试图执行完当前指令,然后暂停指令执行去处理异常,异常处理完后返回继续处理指令。异常又成为中断,中断向量。

arm有七种异常,异常的处理地址从0x0000000到0x000001c,每个字(32位)存放一个中断向量。

| 异常 | 地址 | 工作模式 | 描述 |

|---|---|---|---|

| reset | 0x0000000 | SVC | 复位异常,复位或上电后,arm此开始执行指令 |

| Undefine(undefined instruction) | 0x0000004 | UND | 未定义,当arm试图执行未定义指令时,arm跳转到此处执行 |

| Swi(Software Interrupt ) | 0x0000008 | SVC | 软中断,swi指令执行后,arm跳转到此处执行 |

| Prefetch Abort | 0x00000C | ABT | 当指令预取失败时,arm跳转到此处执行 |

| Data Abort | 0x000010 | ABT | 当数据访问失败时,arm跳转到此处执行 |

| IRQ (Interrupt Request ) | 0x000018 | IRQ | 当普通中断发生时,arm跳转到此处执行 |

| FIQ(Fast Interrupt Request) | 0x00001C | FIQ | 当快速中断发生时,arm跳转到此处执行 |

ARM异常处理

发生异常后处理器硬件执行:

1 ,保存CPSR到新模式的SPSR寄存器中

2,修改CPSR中模式位,切换到新模式

3,修改CPSR:清除Thumb位,中断必须在32位模式处理;如果异常是IRQ,则置I位,禁止IRQ中断;如果异常是FIQ,则置F位和I位,禁止IRQ和FIQ中断。

4,保存PC值到新模式下r14寄存器

5,把对应异常中断向量地址保存到PC程序计数器,后续软件开始处理,从PC地址开始执行。

软件处理;