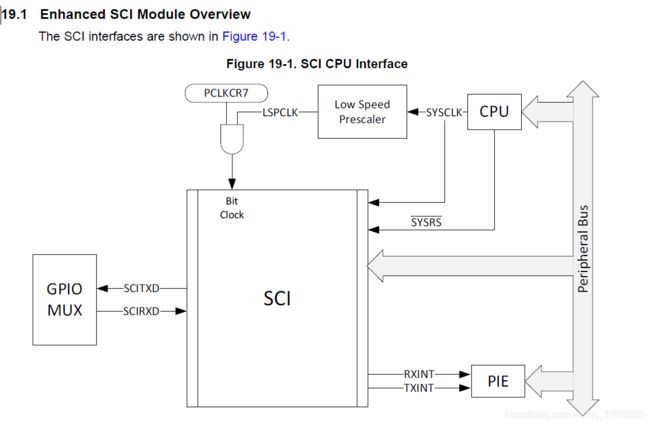

TMS320F28377学习笔记——SCI串行通信接口

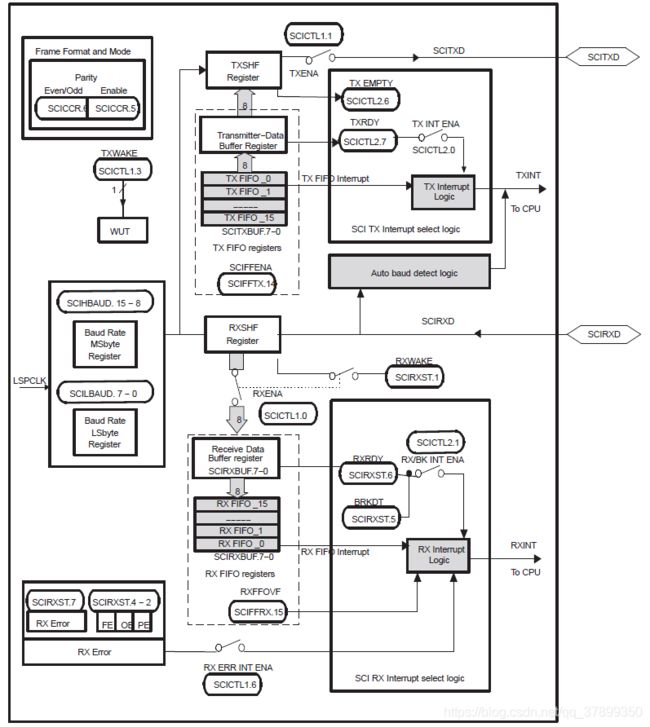

本章介绍串行通信接口(SCI)模块的功能和操作。 SCI是一种双线异步串行端口,通常称为UART。 SCI模块支持CPU和使用标准非归零(NRZ)格式的其他异步外设之间的数字通信。 SCI接收器和发送器每个都有一个16级深FIFO,用于减少服务开销,每个都有自己独立的使能和中断位。 两者都可以独立操作以进行半双工通信,或同时进行全双工通信。

为了指定数据完整性,SCI检查接收到的数据是否存在中断检测,奇偶校验,溢出和帧错误。 比特率可通过16位波特选择寄存器编程为不同的速度。

SCI模块的功能包括:

•两个外部引脚:

- SCITXD:SCI发送输出引脚

- SCIRXD:SCI接收输入引脚

如果不用于SCI,则两个引脚都可以用作GPIO。

•波特率可编程为64K不同速率

•数据字格式

- 一个开始位

- 数据字长度可编程为1至8位

- 可选偶数/奇数/无奇偶校验位

- 一个或两个停止位

•四个错误检测标志:奇偶校验,溢出,成帧和中断检测

•两种唤醒多处理器模式:空闲线和地址位

•半双工或全双工操作

•双缓冲接收和发送功能

•发送器和接收器操作可以通过具有状态标志的中断驱动或轮询算法来完成

•发送器和接收器中断的独立使能位(BRKDT除外)

•NRZ(不归零)格式

•13个SCI模块控制寄存器位于控制寄存器帧中,从地址7050h开始

该模块中的所有寄存器都是8位寄存器,连接到外设帧2.当访问寄存器时,寄存器数据位于低位字节(7-0),高位字节(15-8)读取为零。写入高位字节无效。

增强功能:

•自动波特率检测硬件逻辑

•16级发送/接收FIFO

SCI模块框图如图所示:

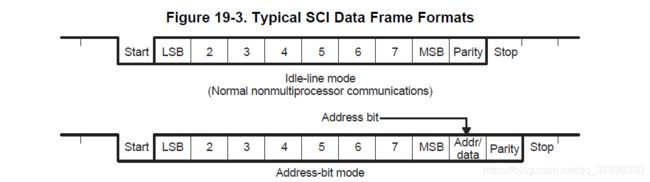

SCI可编程数据格式

接收和发送的SCI数据采用NRZ(非归零)格式。 NRZ数据格式如图19-3所示,包括:

•一个起始位

•一到八个数据位

•偶数/奇数奇偶校验位(可选)

•一个或两个停止位

•用于区分地址和数据的额外位(仅限地址位模式)

基本数据单元称为字符,长度为1到8位。 每个数据字符都使用起始位,一个或两个停止位以及可选的奇偶校验和地址位进行格式化。 带有格式信息的数据字符称为帧,如图19-3所示。

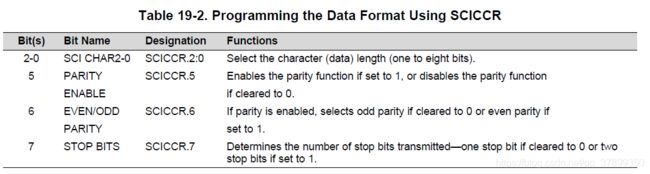

要编程数据格式,请使用SCICCR寄存器。 用于编程数据格式的位如表19-2所示。

SCI通信格式

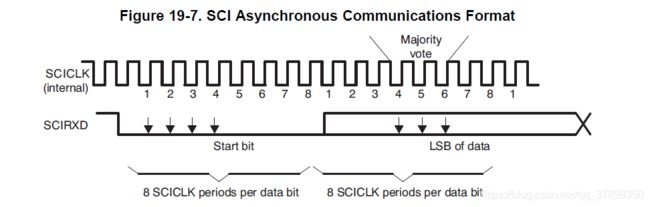

SCI异步通信格式使用单线(单向)或双线(双向)通信。在此模式下,帧由起始位,1到8个数据位,可选的偶数/奇数奇偶校验位以及一个或两个停止位组成(如图19-7所示)。每个数据位有8个SCICLK周期。

接收器在接收到有效起始位时开始操作。有效起始位由四个连续的零位内部SCICLK周期标识,如图19-7所示。如果任何位不为零,则处理器重新开始并开始寻找另一个起始位。

对于起始位之后的位,处理器通过在位中间产生三个样本来确定位值。这些采样发生在第四,第五和第六SCICLK周期,并且位值确定基于多数(三分之二)。图19-7说明了此异步通信格式,其中一个起始位显示了多数表决的位置。

由于接收器将自身同步到帧,因此外部发送和接收设备不必使用同步的串行时钟。时钟可以在本地生成。

通信模式下的接收器信号

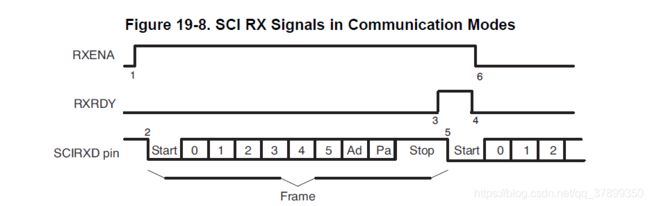

图19-8说明了接收器信号时序的示例,它假设了以下条件:

•地址位唤醒模式(地址位不会出现在空闲线路模式下)

•每个字符六位

(1)数据到达SCIRXD引脚,检测到起始位。

(2)位RXENA变为低电平以禁用接收器。数据继续在RXSHF中组装,但不会传输到接收器缓冲寄存器。

注意:

1.标志位RXENA(SCICTL1,位0)变为高电平以使能接收器。

2.数据到达SCIRXD引脚,检测到起始位。

3.数据从RXSHF移位到接收缓冲寄存器(SCIRXBUF);请求中断。标志位RXRDY(SCIRXST,位6)变为高电平,表示已收到新字符。

该程序读取SCIRXBUF;标志RXRDY自动清除。

5.下一个数据字节到达SCIRXD引脚;检测到起始位,然后清除。

6.位RXENA变为低电平以禁用接收器。数据继续在RXSHF中组装,但不会传输到接收器缓冲寄存器。

通信模式下的发射机信号

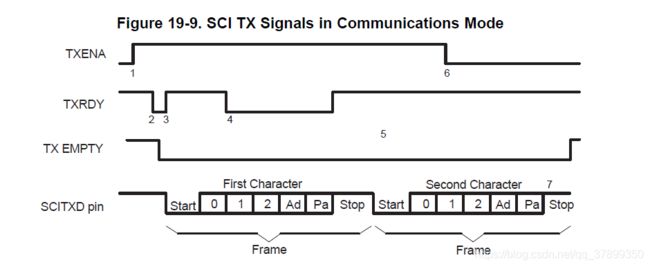

图19-9说明了发送器信号时序的示例,它假设了以下条件:

•地址位唤醒模式(地址位不会出现在空闲线路模式下)

•每个字符三位

注意:

1. TXENA位(SCICTL1,位1)变为高电平,使发送器能够发送数据。

2. SCITXBUF写入;因此,(1)发射机不再为空,(2)TXRDY变低。

3. SCI将数据传输到移位寄存器(TXSHF)。发送器准备好第二个字符(TXRDY变为高电平),并请求中断(使能中断,TX INT ENA位 - SCICTL2,位0 - 必须置1)。

4.在TXRDY变为高电平后,程序将第二个字符写入SCITXBUF(第3项)。 (第二个字符写入SCITXBUF后,TXRDY再次变为低电平。)

5.完成第一个字符的传输。将第二个字符传输到移位寄存器

TXSHF开始了。

6. TXENA位变为低电平以禁用发送器; SCI完成传输当前字符。

7.完成第二个字符的传输;发射器是空的,准备好新角色。

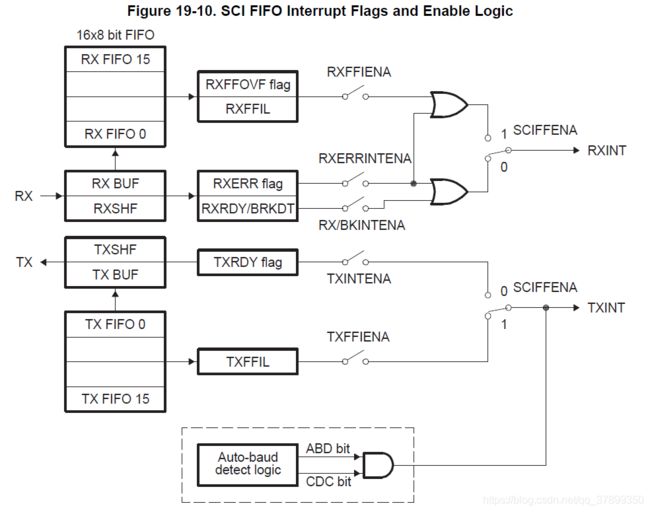

SCI端口中断

SCI接收器和发送器可以被中断控制。 SCICTL2寄存器有一个标志位(TXRDY),表示有效的中断条件,SCIRXST寄存器有两个中断标志位(RXRDY和BRKDT),加上RX ERROR中断标志,它是FE,OE,BRKDT的逻辑或,和PE条件。发送器和接收器具有独立的中断使能位。未使能时,中断未被置位;但是,条件标志仍然有效,反映了传输和接收状态。

SCI具有用于接收器和发送器的独立外设中断向量。外设中断请求可以是高优先级或低优先级。这由从外设输出到PIE控制器的优先级位表示。当RX和TX中断请求都以相同的优先级进行时,接收器的优先级始终高于发送器,从而降低了接收器溢出的可能 性。

外设中断的操作在外部外设接口(ePIE)章节的外设中断扩展控制器部分进行了描述。

•如果RX / BK INT ENA位(SCICTL2,位1)置1,则在发生以下事件之一时,将断言接收器外设中断请求:

- SCI接收完整帧并将RXSHF寄存器中的数据传送到SCIRXBUF寄存器。此操作设置RXRDY标志(SCIRXST,位6)并启动中断。

- 发生中断检测条件(SCIRXD在丢失停止位后的10位周期内为低电平)。此操作将BRKDT标志位(SCIRXST,位5)置1并启动中断。

•如果TX INT ENA位(SCICTL2.0)置1,只要SCITXBUF寄存器中的数据被传送到TXSHF寄存器,就会置位发送器外设中断请求,表示CPU可以写入SCITXBUF;此操作将TXRDY标志位(SCICTL2,位7)置1并启动中断。

注:由RXRDY和BRKDT位产生的中断由RX / BK INT ENA位(SCICTL2,位1)控制。 RX ERROR位产生的中断由RX ERR INT ENA位(SCICTL1,位6)控制。

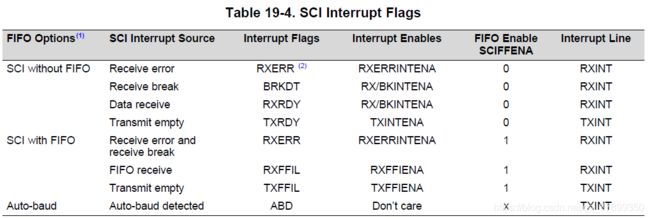

图19-10和表19-4说明了nonFIFO / FFO模式下SCI中断的操作/配置。

(1)FIFO模式TXSHF在延迟值后直接加载,不使用TXBUF。

(2)RXERR可以通过BRKDT,FE,OE,PE标志设置。 在FIFO模式下,BRKDT中断仅通过RXERR标志