【SoC FPGA学习】十、SoC FPGA 开发板的 FPGA 配置数据下载和固化

一、SoC FPGA 启动配置方式介绍

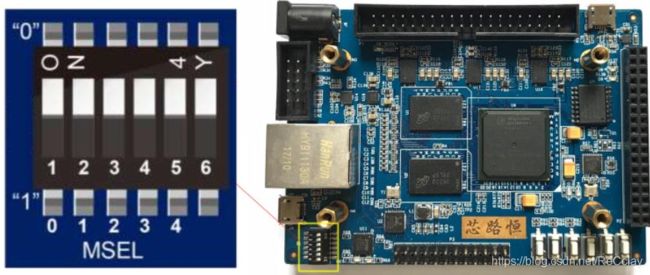

Intel Cyclone V SoC FPGA 支持在上电时根据启动设置引脚的电平状态选择从 EPCS 或者 HPS 中启动。一般的硬件板卡在设计时,都使用拨码开关来设置启动设置引脚的电平。具体是通过 EPCS 还是 HPS 启动,由一个 6 位拨码开关通过设置不同的值来决定。 下图所示为 AC501-SoC 开发板上的启动设置拨码开关。

Cyclone V SoC FPGA 有 5 位的启动设置引脚用于启动方式的设置,为MSEL0~MSEL4。这四个引脚的不同状态,会设定不同的启动方式,详细的启动方式与 MSEL 脚状态如下表所示:

配置方式 描述

| 配置方式 | MSEL4…0 | 描述 |

|---|---|---|

| AS | 10010 | FPGA从EPCS快速配置 |

| AS | 10011 | FPGA从EPCS标准速度配置 |

| FPPx32/CompressionEnabled /Fast POR | 01010 | FPGA 从 HPS 软件配置,在 应用程序中 读取存储在 SD 卡上的 rbf 文件,然后配置 FPGA |

| FPPx16/CompressionDisable /Fast POR | 00000 | FPGA 从 HPS 软件配置,在 U-Boot 阶段读取存储在 SD 卡上的 rbf 文件,然后配置 FPGA |

常见的基于 Intel Cyclone V SoC FPGA 器件的开发板都支持两种方式来配置 FPGA:

- 1、使用 JTAG 编程:此种方式下, FPGA 的配置 bit 流文件直接被下载入Cyclone V SoC FPGA 中,下载之后 FPGA 就会按照该配置文件的信息运行。 但是一旦 FPGA 的供电被关闭了,配置信息也就丢失了。

- 2、使用 AS 方式: AS 方式全称为主动串行配置(Active Serialconfiguration), 此种方式下 FPGA 的配置 bit 流文件会被下载进串行配置器件(EPCS) 中, EPCS 是一种 SPI 接口的 Nor Flash 存储器,即使掉电之后,数据依然存在不会丢失。当开发板下次上电时,如果 MSEL 设置了从 EPCS 中启动,则 Cyclone V SoC FPGA 会自动从 EPCS 中加载配置数据。

一般的原厂或第三方合作厂商在设计硬件板卡时, 都直接在板卡上集成了对应的 USB Blaster II 下载调试电路,该电路实现了 USB 转 JTGA 协议的功能,使用该电路就能实现 PC 通过 JTAG 协议和 SoC FPGA 芯片通信的功能。而在 AC501-SoC 开发板上, 并未设计板载的 USB Blaster II 下载调试电路, 但是提供了标准的 IDC3-10 的 USB Blaster 接口, 使用时可以使用独立的 USB Blaster 设备, 通过该接口与 AC501-SoC 开发板上的 SoC FPGA 器件相连, 以支持 PC 使用 JTAG 协议连接 FPGA 和 HPS,并完成配置 bit 流的传输以及运行调试的功能。

和传统的单芯片纯 FPGA 方式不同, Cyclone V SoC FPGA 上的 JTAG 链同时连接了 FPGA 和 HPS。 因此在使用 JTAG 配置 FPGA 时过程也有一定的差别。 接下来以一个具体的例子分别讲解配置 sof 到 FPGA 中和烧写 jic 格式的配置文件到 EPCS 中的方法。

二、USB Blaster 驱动安装

USBBlaster驱动是给FPGA下载程序时候用的,不安装的话会无法下载程序到FPGA。需要注意的是,安装USB Blaster之前,确保自己安装好了Quartus软件。

驱动安装参考梅哥:http://www.corecourse.cn/forum.php?mod=viewthread&tid=27738

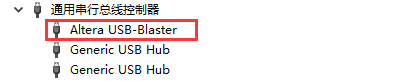

注意,当USB Blaster 的USB一端连接上PC端后,理论上在设备管理器中就会更新出USB Blaster,无论下面哪种形式都可以:

如果并没有出现上述两种图标,要么是线坏了(我的就是这种情况,多谢小庆帮忙解决!),要么就是USB Blaster坏了!

如果出现的是标黄的USB-Blaster,![]() 说明是驱动没有安装好,这时可以右击USB-Blaster,选择其中的“更新驱动程序”

说明是驱动没有安装好,这时可以右击USB-Blaster,选择其中的“更新驱动程序”

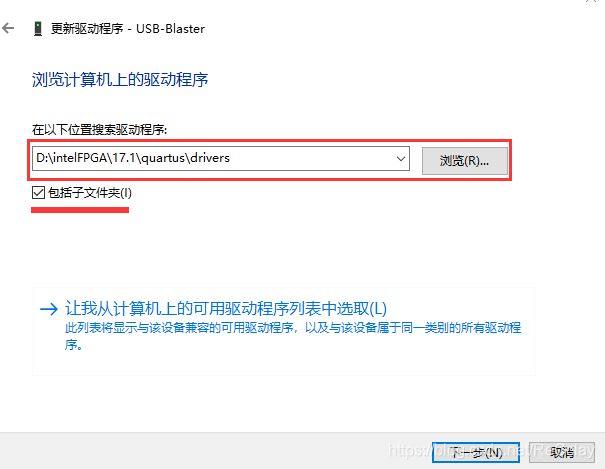

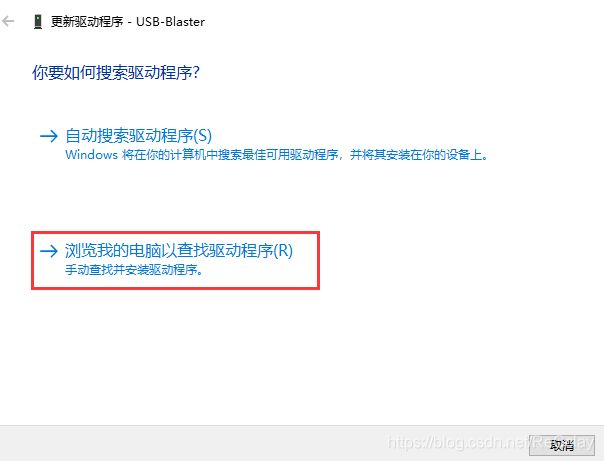

然后选择“浏览我的电脑以查找驱动程序(R)”

接着选择quartus安装目录下的drivers所在目录【注意一定是drivers所在目录】,并勾选下面的“包括子文件夹(I)”后,点击下一步,即可自自动安装。

而后再看设备管理器,会发现标黄的USB-Blaster会变成如下图所示

至此USB-Blaster的驱动安装完毕。

三、sof 文件生成与烧写

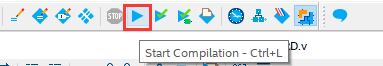

在sof文件烧写之前,还是有必要再回顾一下生成sof文件的方法,如下图所示:

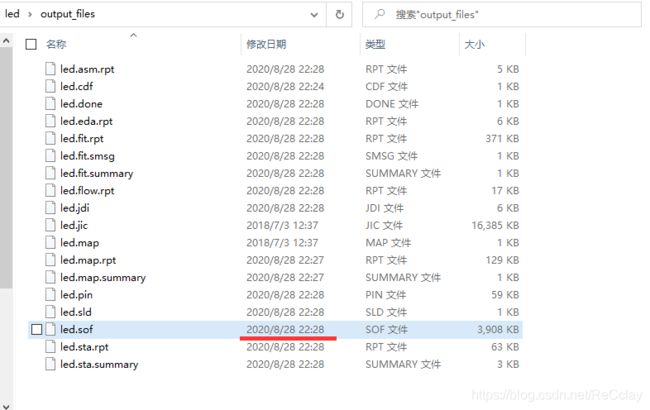

我们可以根据时间戳,判断sof文件是否是最新生成的

接下来便是下载sof文件,在下载 sof 时,对 FPGA 的启动方式设置无任何要求,任意一种状态都可以,因为 JTAG 模式配置 FPGA 的优先等级最高, 不受启动方式设置的影响。

打开一个 FPGA 工程,如本例以 FPGA 的 LED 测试工程“led”为例。(该工程位于:AC501-SoC开发板资料文件夹版\Demos\FPGA下,注意要将其拷贝到没有中文的目录下。)

在菜单栏中依次点击 Tools > Programmer 或直接点击 Programer 图标以打开下载界面,如下图所示。

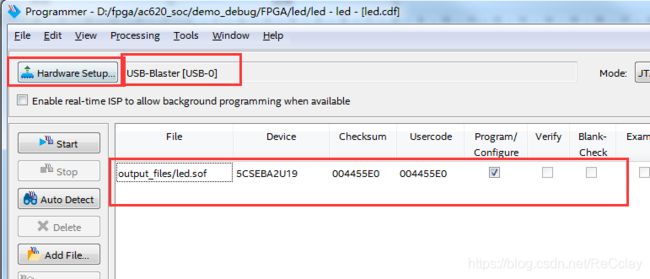

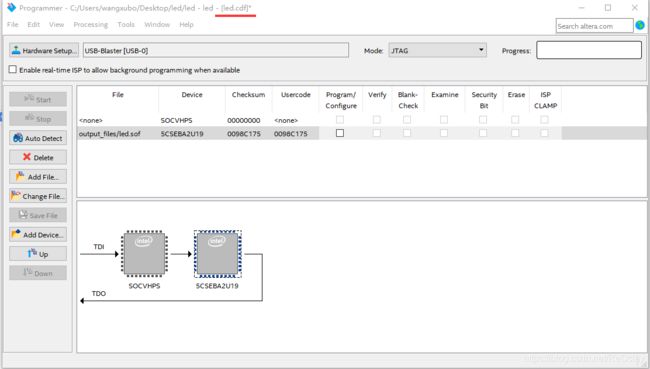

打开之后,软件可能会默认搜索到工程下的 led.sof 文件并添加进来了,如下图所示。如果没有添加也没有关系, 因为添加的内容我们后面操作时也会手动将其删除的。

需要我们关注的是其中的USB-Blaster[USB-0]一栏是否正常显示,如果 Hardware Setup 一栏没有自动找到 USB Blaster,则可能需要检查以下两个方面

单击其中的![]() ,然后双击下图中的USB-Blaster,双击完毕后该界面上方的 Currently selected hardware会显示,最后Close。

,然后双击下图中的USB-Blaster,双击完毕后该界面上方的 Currently selected hardware会显示,最后Close。

close出来再看,会发现此时USB-Blaster[USB-0]便显示出来了!

![]()

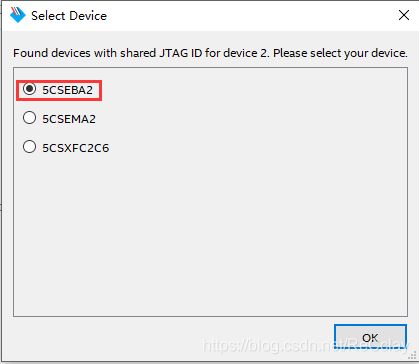

如果 USB Blaster 就绪了, 此刻我们直接点击 Start 来下载添加的 sof 文件是会失败的,这是因为 JTAG 链上连接了 FPGA 和 HPS 两个设备,下载器不知道需要将文件下载到哪个设备中。首先点击左侧的 Auto Detect 按钮,以使用 JTAG 链检测其连接的设备型号。会提示同一个 JTAG ID 对应的多个设备, 根据我们使用的器件型号为 5CSEBA2, 因此选择第一个然后 OK, 如下图所示:

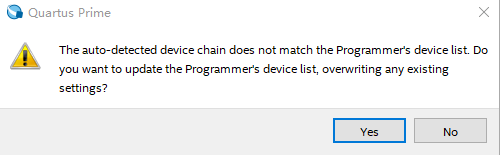

此时软件会提示自动检测到的设备和 Programer 中已经添加的设备不匹配,询问是否更新,点击 YES 更新即可, 如下图所示。

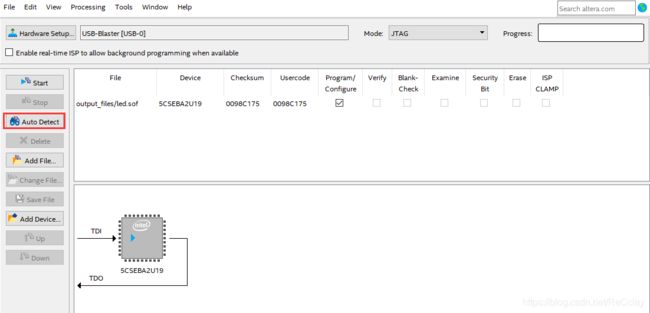

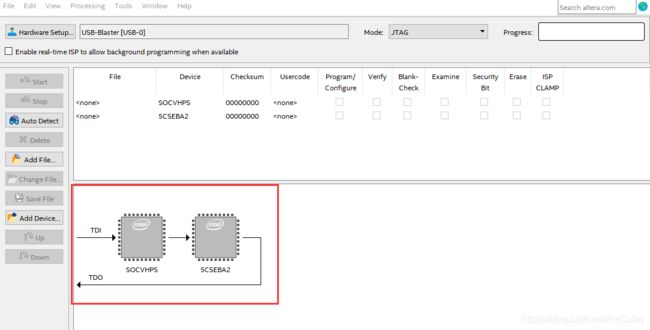

更新完成后可以看到, Programer 窗口的下方展示了 JTAG 链上的设备关系, 如下图所示。 主要是 TDI 这个信号线, 首先进入 SOCVHPS 中, 然后从SOCVHPS 的 TDO 端口流出,进入 FPGA(5CSEBA2) 的 TDI 端口,再从FPGA 的 TDO 端口流出,回到 JTAG 接口的 TDO 信号上。

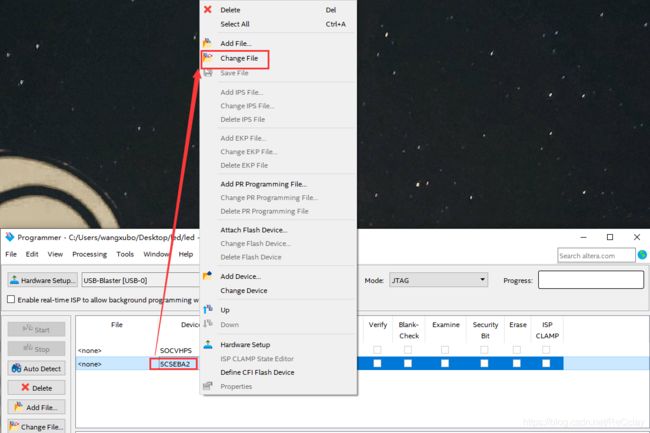

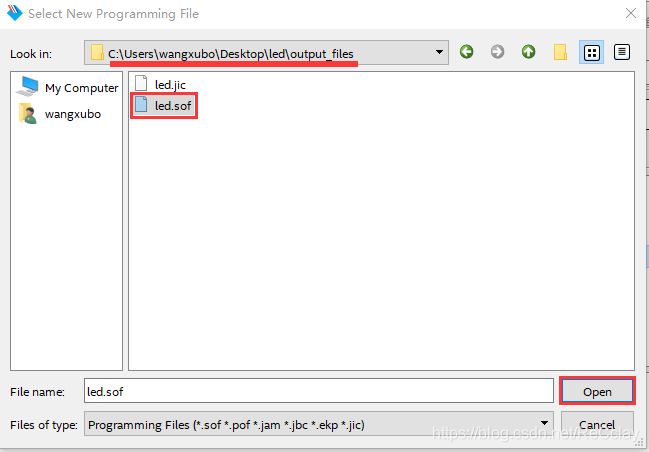

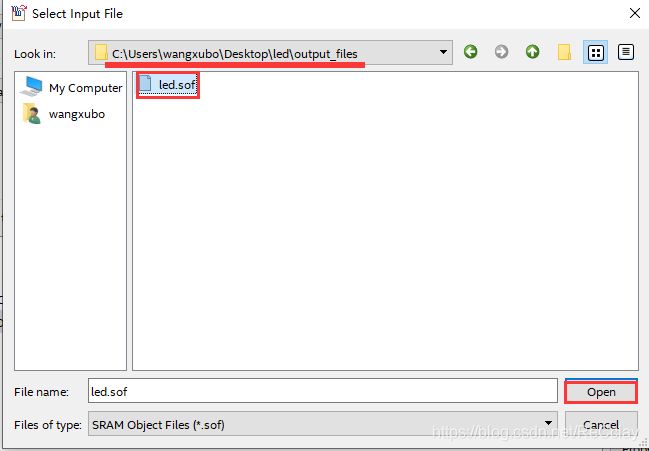

选中 Device 一栏中的 5CSEBA2 项, 右键单击,在弹出的对话框中选择 Change File,然后找到该工程output_files目录下的 led.sof 文件并添加,如下图所示:

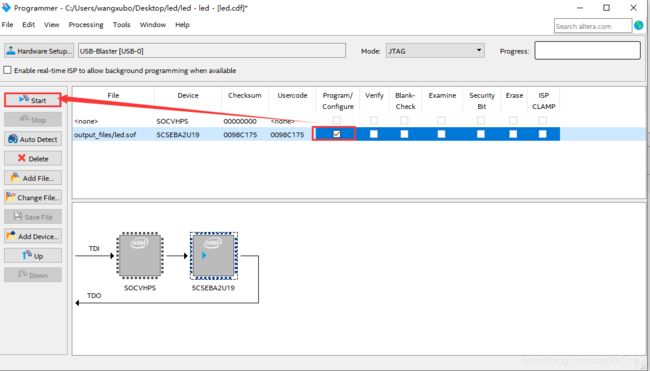

选择后的显示效果如下图所示,同时此时led.cdf后面会显示一个*,表示修改了未保存,可以通过ctrl+s进行保存!

点击 sof 文件对应的 Program/Configure 复选框以选中(最后修改完毕后,别忘了保存led.cdf文件),然后点击 Start 按钮,就可以开始配置 sof 文件到 FPGA 中了,如下图所示:

烧写成功后,右上角会显示Successful!

配置完成后, 可以看到开发板上的两个 FPGA_LED 灯分别闪烁,其中 FPGA_LED0 的闪烁频率是 FPGA_LED1的两倍。

四、jic 文件生成与烧写

通过以上方式,完成了 sof 文件下载到 FPGA 中的功能。但是此时下载的数据是保存在 FPGA 的 SRAM 中的,掉电之后数据就丢失了,为了能够实现FPGA 上电自动配置的功能,可以将配置数据 bit 文件转化为 jic 文件,烧写到 EPCS 存储器中,并设置 FPGA 从 EPCS 中启动,这样 FPGA 下次上电时就能够自动从 EPCS 中加载配置数据了, 无需再用 JTAG 下载。

接下来讲解 AC501-SoC 开发板上所用 Cyclone V SoC FPGA 器件的 jic 文件生成以及烧写方式。

当需要烧写 jic 文件到 epcs 中时,需要首先设置 FPGA 从 EPCS 中启动,即设置 MSEL[4…0]为 10010 ,即 FPGA从EPCS快速配置。

同样还是打开一个设计好的 FPGA 工程,如 led,然后在菜单栏中依次点击 File > Convert Programming Files,如下图所示。

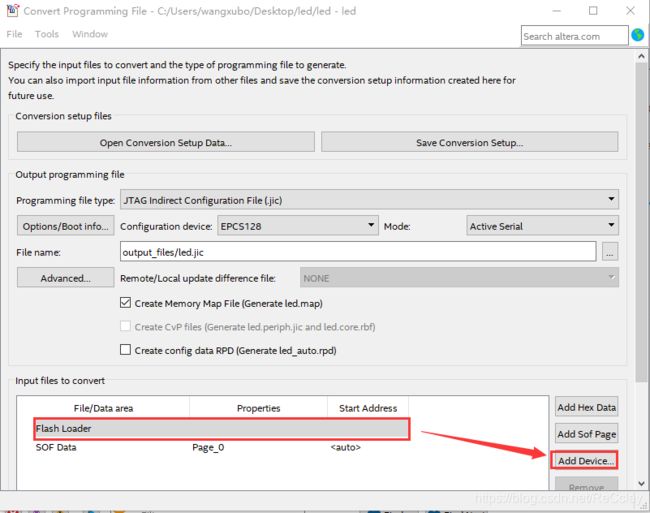

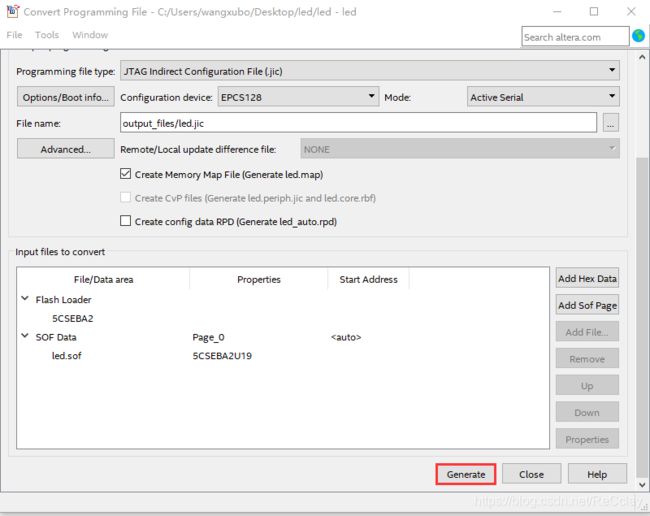

在打开的窗口中, 选择 Programming file type 为 JTAG Indirect ConfigurationFile(jic)、 Configuration device 为 EPCS16, 注意, 是 EPCS128, 不是EPCQ128, File name 设置一个有辨识度的名字,例如 led.jic,如下图所示:

接着选中下方的 Flash Loader,然后点击右侧的 Add Device, 如下图所示:

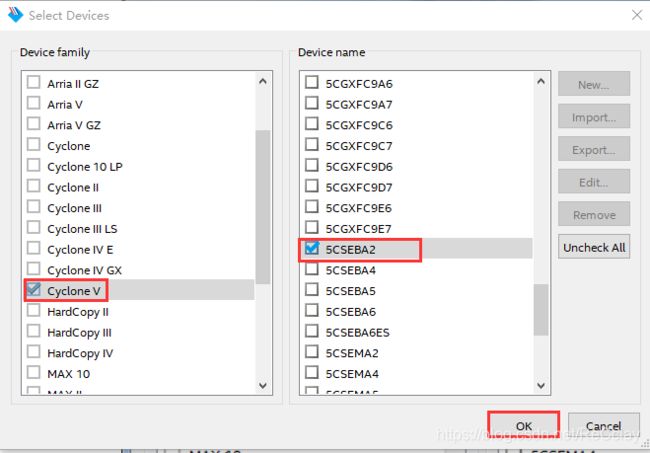

在弹出的对话框中选择用户使用的开发板上使用的 FPGA 器件。例如对于AC501-SoC,应该选择 5CSEBA2。 而如果用户使用的是 DE10-Nano-SoC 开发板,则应该选择 5CSEBA6, 然后点击 OK,如下图所示:

选中 SOF Data 选项,然后点击右侧的 Add File,添加 led.sof 并确认,如下图所示:

然后选择output_files文件夹下的led.sof文件,并单击Open。

添加好之后,点击右下角的 Generate 按钮, 就能生成 jic 文件了,如下图所示:

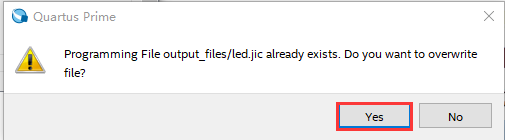

在生成过程中,会弹出问你是否要覆盖led.jic文件,选择Yes即可!

生成完毕后,弹出如下图所示提示框,点击OK即可关闭,如下图所示:

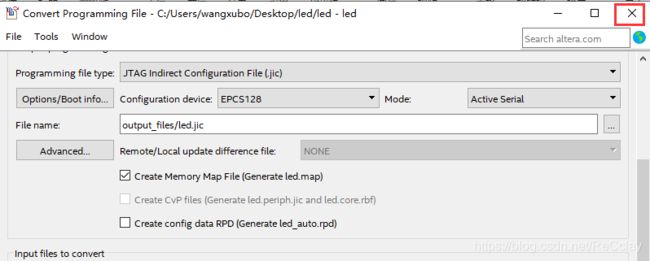

而后点击叉号关闭Convert Programming File窗口,如下图所示:

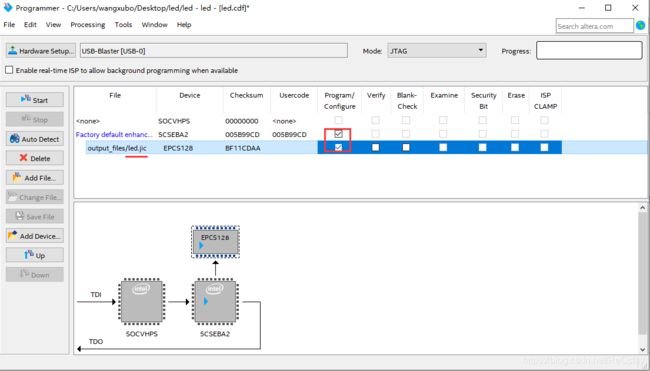

接着进行烧写,依然是先通过 Auto Detect 检测器件,然后选中 FPGA 器件右击以Change File,只是添加 File 的时候,选择刚刚 generate 好的 led.jic 文件。 勾选Program/Configure 选项,然后点击 Start,就能够完成烧写到 EPCS 的功能了。如下图所示:

烧写完成后,给开发板重新上电, 可以看到开发板上的两个 FPGA_LED 灯分别闪烁,其中 FPGA_LED0 的闪烁频率是 FPGA_LED1的两倍,并且断电再上电后仍可以保持程序不丢失!