FPGA原语之ISERDES/OSERDES

ISERDES/OSERDES

ISERDES模块的作用在于实现高速源同步输入数据的串并转换。

OSERDES模块的作用在于实现高速源同步输出数据的并串转换。

- SERDES支持SDR和DDR两个模式。

- SDR模式支持2、3、4、5、6、7、8bit位宽;

- DDR模式支持4、6、8bit位宽,10或14bit位宽需要两个模块级联。

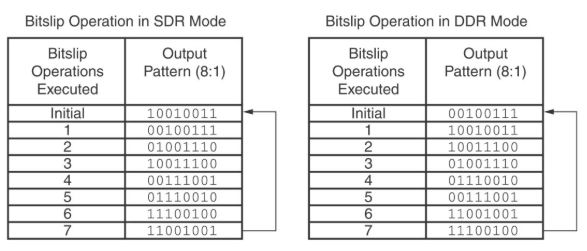

- Bitslip模块可以使设计者重新排列输入的并行数据,可用于源同步。

1. ISERDES

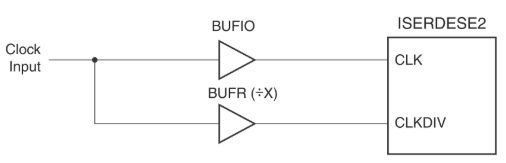

ISERDES接收外部输入FPGA的高速源同步串行信号,再FPGA内部将其转换成用户需要的并行数据。ISERDES的功能框图如下所示。

-

串行数据输入端

该部分接收外部输入的高速源同步数据,数据模式可以是SDR或者DDR。在SDR模式下,数据转换的位宽可以胃2,3,4,5,6,7,8bit。在DDR模式下,数据位宽可以是4,6,8bit。如果是两个iserdes模块级联使用,DDR模式还可以支持10,14bit。 -

并行数据输出端

该部分输出用户所需的并行数据,SDR模式下,位宽为2,3,4,5,6,7,8bit;DDR模式下,位宽为4,6,8,10,14bit。 -

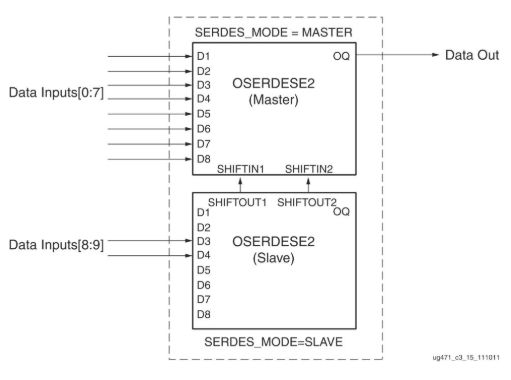

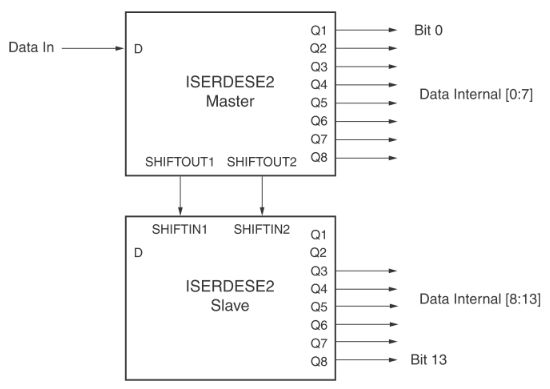

级联接口

该部分是实现DDR模式下10,14bit位宽的关键接口,通过该接口与两外一个ISERDES2级联,两者共同完成10bit,14bit数据的串并转换。如下图所示。

注意:对于级联模式下的slave,数据接口从Q3开始有效,Q1,Q2无效。

对于SDR模式,Bislip使能一次,数据会左移1次,对于8bit的并行数据,移动8次完成一个循环,可以无止境的循环,直到用户找到定义的并行数据;对于DDR模式,Bitslip工作方式不同,Bitslip使能1次,数据右移1次或者左移3次,两者交替进行,对与8bit位宽的数据,同样移动8次完成一个循环。

ISERDES的例化如下。

Library UNISIM;

use UNISIM.vcomponents.all;

-- <-----Cut code below this line and paste into the architecture body---->

-- ISERDESE2: Input SERial/DESerializer with Bitslip

-- Kintex-7

-- Xilinx HDL Language Template, version 2018.2

ISERDESE2_inst : ISERDESE2

generic map (

DATA_RATE => "DDR", -- DDR, SDR

DATA_WIDTH => 4, -- Parallel data width (2-8,10,14)

DYN_CLKDIV_INV_EN => "FALSE", -- Enable DYNCLKDIVINVSEL inversion (FALSE, TRUE)

DYN_CLK_INV_EN => "FALSE", -- Enable DYNCLKINVSEL inversion (FALSE, TRUE)

-- INIT_Q1 - INIT_Q4: Initial value on the Q outputs (0/1)

INIT_Q1 => '0',

INIT_Q2 => '0',

INIT_Q3 => '0',

INIT_Q4 => '0',

INTERFACE_TYPE => "MEMORY", -- MEMORY, MEMORY_DDR3, MEMORY_QDR, NETWORKING, OVERSAMPLE

IOBDELAY => "NONE", -- NONE, BOTH, IBUF, IFD

NUM_CE => 2, -- Number of clock enables (1,2)

OFB_USED => "FALSE", -- Select OFB path (FALSE, TRUE)

SERDES_MODE => "MASTER", -- MASTER, SLAVE

-- SRVAL_Q1 - SRVAL_Q4: Q output values when SR is used (0/1)

SRVAL_Q1 => '0',

SRVAL_Q2 => '0',

SRVAL_Q3 => '0',

SRVAL_Q4 => '0'

)

port map (

O => O, -- 1-bit output: Combinatorial output

-- Q1 - Q8: 1-bit (each) output: Registered data outputs

Q1 => Q1,

Q2 => Q2,

Q3 => Q3,

Q4 => Q4,

Q5 => Q5,

Q6 => Q6,

Q7 => Q7,

Q8 => Q8,

-- SHIFTOUT1, SHIFTOUT2: 1-bit (each) output: Data width expansion output ports

SHIFTOUT1 => SHIFTOUT1,

SHIFTOUT2 => SHIFTOUT2,

BITSLIP => BITSLIP, -- 1-bit input: The BITSLIP pin performs a Bitslip operation synchronous to

-- CLKDIV when asserted (active High). Subsequently, the data seen on the

-- Q1 to Q8 output ports will shift, as in a barrel-shifter operation, one

-- position every time Bitslip is invoked (DDR operation is different from

-- SDR).

-- CE1, CE2: 1-bit (each) input: Data register clock enable inputs

CE1 => CE1,

CE2 => CE2,

CLKDIVP => CLKDIVP, -- 1-bit input: TBD

-- Clocks: 1-bit (each) input: ISERDESE2 clock input ports

CLK => CLK, -- 1-bit input: High-speed clock

CLKB => CLKB, -- 1-bit input: High-speed secondary clock

CLKDIV => CLKDIV, -- 1-bit input: Divided clock

OCLK => OCLK, -- 1-bit input: High speed output clock used when INTERFACE_TYPE="MEMORY"

-- Dynamic Clock Inversions: 1-bit (each) input: Dynamic clock inversion pins to switch clock polarity

DYNCLKDIVSEL => DYNCLKDIVSEL, -- 1-bit input: Dynamic CLKDIV inversion

DYNCLKSEL => DYNCLKSEL, -- 1-bit input: Dynamic CLK/CLKB inversion

-- Input Data: 1-bit (each) input: ISERDESE2 data input ports

D => D, -- 1-bit input: Data input

DDLY => DDLY, -- 1-bit input: Serial data from IDELAYE2

OFB => OFB, -- 1-bit input: Data feedback from OSERDESE2

OCLKB => OCLKB, -- 1-bit input: High speed negative edge output clock

RST => RST, -- 1-bit input: Active high asynchronous reset

-- SHIFTIN1, SHIFTIN2: 1-bit (each) input: Data width expansion input ports

SHIFTIN1 => SHIFTIN1,

SHIFTIN2 => SHIFTIN2

);

-- End of ISERDESE2_inst instantiation

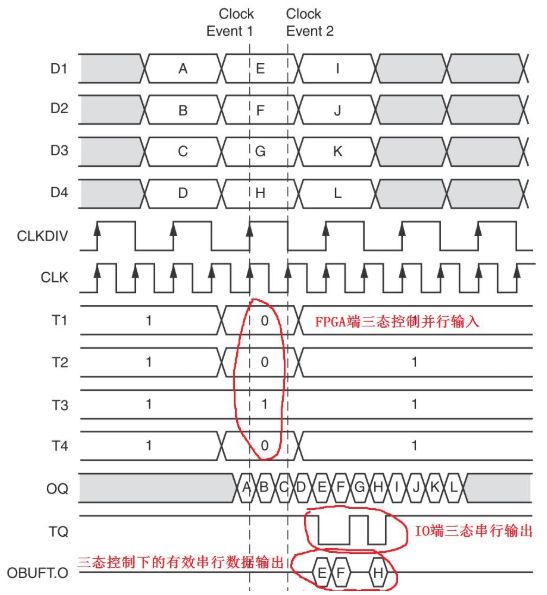

2. OSERDES

OSERDES模块与ISERDES不同,少了Bitslip模块,多了一个三态控制模块,可以实现三态控制并串转换功能。下图为OSERDES2的功能框图。

与ISERDES2的级联用法类似,用于slave的OSERDES2有效数据位从Q3开始,Q1,Q2无效。

OSERDES的例化如下。

Library UNISIM;

use UNISIM.vcomponents.all;

-- <-----Cut code below this line and paste into the architecture body---->

-- OSERDESE2: Output SERial/DESerializer with bitslip

-- Kintex-7

-- Xilinx HDL Language Template, version 2018.2

OSERDESE2_inst : OSERDESE2

generic map (

DATA_RATE_OQ => "DDR", -- DDR, SDR

DATA_RATE_TQ => "DDR", -- DDR, BUF, SDR

DATA_WIDTH => 4, -- Parallel data width (2-8,10,14)

INIT_OQ => '0', -- Initial value of OQ output (1'b0,1'b1)

INIT_TQ => '0', -- Initial value of TQ output (1'b0,1'b1)

SERDES_MODE => "MASTER", -- MASTER, SLAVE

SRVAL_OQ => '0', -- OQ output value when SR is used (1'b0,1'b1)

SRVAL_TQ => '0', -- TQ output value when SR is used (1'b0,1'b1)

TBYTE_CTL => "FALSE", -- Enable tristate byte operation (FALSE, TRUE)

TBYTE_SRC => "FALSE", -- Tristate byte source (FALSE, TRUE)

TRISTATE_WIDTH => 4 -- 3-state converter width (1,4)

)

port map (

OFB => OFB, -- 1-bit output: Feedback path for data

OQ => OQ, -- 1-bit output: Data path output

-- SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each)

SHIFTOUT1 => SHIFTOUT1,

SHIFTOUT2 => SHIFTOUT2,

TBYTEOUT => TBYTEOUT, -- 1-bit output: Byte group tristate

TFB => TFB, -- 1-bit output: 3-state control

TQ => TQ, -- 1-bit output: 3-state control

CLK => CLK, -- 1-bit input: High speed clock

CLKDIV => CLKDIV, -- 1-bit input: Divided clock

-- D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each)

D1 => D1,

D2 => D2,

D3 => D3,

D4 => D4,

D5 => D5,

D6 => D6,

D7 => D7,

D8 => D8,

OCE => OCE, -- 1-bit input: Output data clock enable

RST => RST, -- 1-bit input: Reset

-- SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each)

SHIFTIN1 => SHIFTIN1,

SHIFTIN2 => SHIFTIN2,

-- T1 - T4: 1-bit (each) input: Parallel 3-state inputs

T1 => T1,

T2 => T2,

T3 => T3,

T4 => T4,

TBYTEIN => TBYTEIN, -- 1-bit input: Byte group tristate

TCE => TCE -- 1-bit input: 3-state clock enable

);