VHDL编写8-3线优先编码器

VHDL编写8-3线优先编码器

先简单介绍一下什么是"8-3线优先编码器":

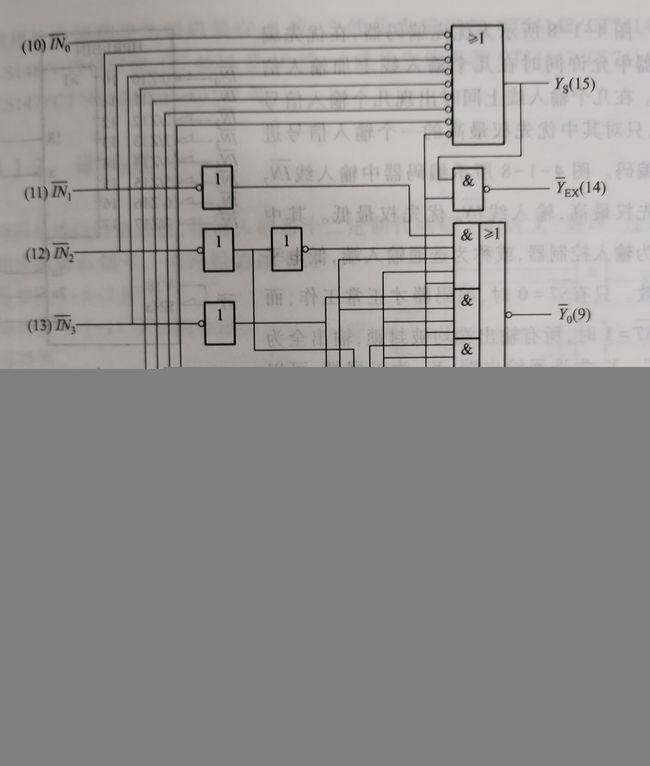

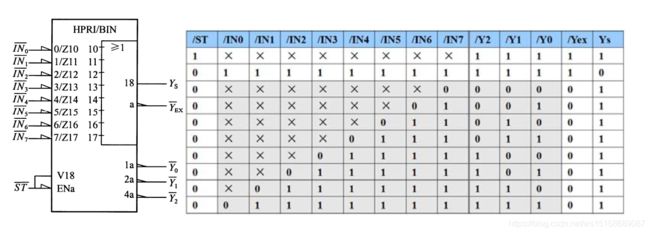

8-3线优先编码器由9个输入端和五个输出端组成,允许同时在几个输入端输入信号。当有多个输入信号传入时,只对其中优先权最高的一个输入信号进行编码(输出的二进制代码以反码形式表示)

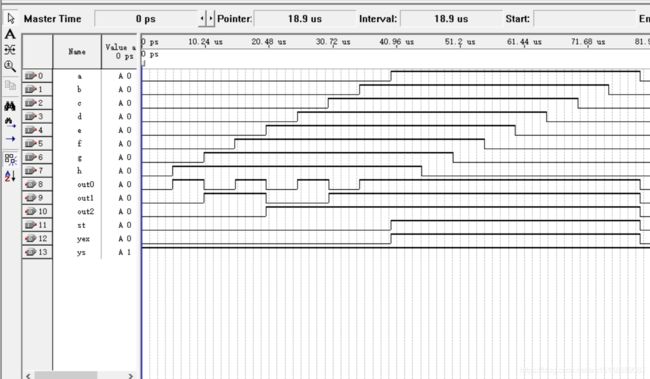

如图所示:

因此,我们可以进行实体定义:

定义八个输入端(由权低到权高):a,b,c,d,e,f,g,h

定义一个选通输入端(0时才正常工作):st

定义三个输出端:out0,out1,out2

定义一个扩展端:yex

定义一个无编码指示器:ys

下面我给出两种语句来实现它:

1.IF…ELSE语句

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY homework3 IS

PORT(a,b,c,d,e,f,g,h:IN BIT; --定义八个输入端(由权低到权高):a,b,c,d,e,f,g,h

st:IN BIT; --定义一个选通输入端(0时才正常工作):st

out0,out1,out2:OUT BIT; --定义三个输出端:out0,out1,out2

yex:OUT BIT; --定义一个扩展端:yex

ys:OUT BIT); --定义一个无编码指示器:ys

END homework3;

ARCHITECTURE yejiayu OF homework3 IS

SIGNAL tmp_in:BIT_VECTOR(7 DOWNTO 0); --信号数组

SIGNAL tmp_out:BIT_VECTOR(4 DOWNTO 0);

BEGIN

tmp_in <= h&g&f&e&d&c&b&a; --用&连接8个输入值并赋值给tmp_in

PROCESS(st,tmp_in)

BEGIN

IF(st='0')THEN --IF…ELSE语句

IF(tmp_in="11111111")THEN

tmp_out<="11110";

ELSIF(tmp_in(7)='0')THEN

tmp_out<="00001";

ELSIF(tmp_in(6)='0')THEN

tmp_out<="00101";

ELSIF(tmp_in(5)='0')THEN

tmp_out<="01001";

ELSIF(tmp_in(4)='0')THEN

tmp_out<="01101";

ELSIF(tmp_in(3)='0')THEN

tmp_out<="10001";

ELSIF(tmp_in(2)='0')THEN

tmp_out<="10101";

ELSIF(tmp_in(1)='0')THEN

tmp_out<="11001";

ELSIF(tmp_in(0)='0')THEN

tmp_out<="11101";

END IF;

ELSE

tmp_out<="11111";

END IF;

out2<=tmp_out(4);out1<=tmp_out(3);out0<=tmp_out(2);yex<=tmp_out(1);ys<=tmp_out(0);

END PROCESS;

END yejiayu;

2.条件信号赋值语句

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY homework4 IS

PORT(a,b,c,d,e,f,g,h:IN STD_LOGIC; --定义八个输入端(由权低到权高):a,b,c,d,e,f,g,h

st:IN STD_LOGIC; --定义一个选通输入端(0时才正常工作):st

out0,out1,out2:OUT STD_LOGIC; --定义三个输出端:out0,out1,out2

yex:OUT STD_LOGIC; --定义一个扩展端:yex

ys:OUT STD_LOGIC); --定义一个无编码指示器:ys

END homework4;

ARCHITECTURE yejiayu OF homework4 IS

SIGNAL tmp_in:STD_LOGIC_VECTOR(7 DOWNTO 0); --信号数组

SIGNAL tmp_out:STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

tmp_in <= h&g&f&e&d&c&b&a; --用&连接8个输入值并赋值给tmp_in

tmp_out <= "11110" WHEN (st='0' AND tmp_in="11111111") ELSE

"00001" WHEN (st='0' AND tmp_in(7)='0') ELSE

"00101" WHEN (st='0' AND tmp_in(6)='0') ELSE

"01001" WHEN (st='0' AND tmp_in(5)='0') ELSE

"01101" WHEN (st='0' AND tmp_in(4)='0') ELSE

"10001" WHEN (st='0' AND tmp_in(3)='0') ELSE

"10101" WHEN (st='0' AND tmp_in(2)='0') ELSE

"11001" WHEN (st='0' AND tmp_in(1)='0') ELSE

"11101" WHEN (st='0' AND tmp_in(0)='0') ELSE

"11111" WHEN (st='1');

out2<=tmp_out(4);out1<=tmp_out(3);out0<=tmp_out(2);yex<=tmp_out(1);ys<=tmp_out(0);

END yejiayu;