AHB-SRAM简单设计之架构图解

前言

还是慢慢来,比较快!在接触这个小项目时,就有种想法,吃透项目!

参考文章:基于AHB总线的sram控制器设计、AHB—SRAMC项目(结构图,核心代码、Testbench架构)

- 问:对于小白,该项目有哪些模块?如何着手?

- 答:这个项目分为三个模块,一个顶层模块sram_top.v,两个内部模块sram_slave_if.v和sram_core.v。其中sram_core.v,一般是公司买的,不用自己写,所以大家可以直接拿来用;sram_slave_if.v是总线控制单元,我们主要是设计这个内部模块;sram_top顶层模块,就是把前面这两个模块例化并连接即可。因此,这个项目的核心部分就是设计sram_slave_if.v

AHB-SRAM介绍

SRAM在整个系统中作为缓存,SRAM控制器实现SRAM存储器与AHB总线的数据信息交换,其一端连接AHB总线,另一端连接SRAM(8k*8两个bank),将AHB总线上的读写操作转换成标准的SRAM读写操作(将控制信号和地址信号及数据信号进行转化,并将其发送给相应的SRAM存储器,进行实际的数据存取)。

本项目中的SRAM控制器具有较低的功耗和较小的面积,其一端连接AHB总线,另一端连接大小为64K的SRAM存储器,该存储器为单端口。本项目的SRAM控制器的作用就是实现SRAM存储器与AHB总线的数据信息交换。其简单结构示意图如图所示:

AHB-SRAM结构图(详细版)

SRAM 控制器各模块详细描述

01. 内部模块 | AHB总线控制单元 ahb_slave_if.v

AHB总线控制单元 ahb_slave_if.v部分的详细设计,点击链接跳转!

总线的控制单元,在设计上称为slave interface(从机端口),用来连接总线与SRAM控制器。所有AHB总线传输过来的数据信号都必须经过总线控制单元的转换处理,才能驱动对应的模块(这里是sram模块)。总线控制单元的接口图如图所示:

小白请注意,上面这张图是AMBA协议中的原图—— AHB bus slave interface(AHB总线从机端口),不是什么玄学!

图中左侧的数据信号为AHB总线传输到总线控制单元的信号,包括地址和数据信号。图中右侧为控制单元反馈给AHB总线的信号。这些信号都是与AHB总线兼容的。当HSEL信号有效时,总线控制单元与 SRAM存储器控制单元之间可以进行信息传输,实现对SRAM存储器的读写操作。

总线控制单元的主要作用就是接收来自AHB总线的地址和数据信息等,将这些总线访问的指令信息处理后送到其他单元:将读写地址信息传送到地址路径,将写数据送到数据路径,同时接收数据路径返回的读数据。

02. 内部模块 sram_core.v

内部模块 sram_core.v部分的详细设计,点击链接跳转!

一般地,此部分代码不需要自己写。如需此部分代码,请点击链接跳转博客了解

03. 顶层模块 | SRAM控制单元 sram_top.v

SRAM控制单元 sram_top.v部分的详细设计,点击链接跳转!

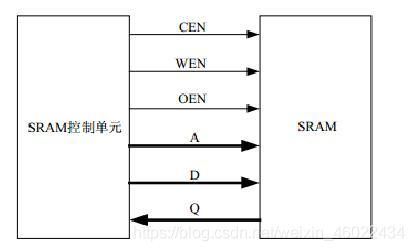

SRAM控制单元直接控制SRAM存储器进行存取操作,因此,SRAM 控制单元与SRAM存储器连接的接口信号也很重要。SRAM存储控制单元和SRAM存储器的信号接口图如下所示:

SRAM的工作原理很简单,SRAM控制单元根据接收到的总线控制信号,将这些信号处理转化为SRAM存储器可以识别的信号,发送到 SRAM存储器;之后,将经过地址译码的物理地址传送到存储器的地址总线,并将数据路径处理的数据送到SRAM存储器的数据总线。最后,SRAM存储器进行相应的读写访问。如果是写操作,SRAM 控制单元的任务就完成了,SRAM 存储器已将数据信息按照要求写入。如果是读操作,SRAM控制单元需要接收返回的读数据,将其送到数据路径,由数据路径将信息传输给AHB总线,最终实现总线对SRAM的读操作。

AHB-SRAMC设计规格:

支持8位、16位和32位的SRAM数据读写操作;

支持SRAM单周期读写(直接影响Soc性能);

支持在多块SRAM组成的存储器中,根据不同地址系统选择一块或者多块SRAM。未被选中的SRAM则处于 low power standby状态。(低功耗)

主要注意2个问题:

AHB总线传输,数据位宽有 8/16/32的传输模式,而sram不一定支持。这里采用4个sram来实现,每块sram对应一个byte。

AHB总线时序和sram时序的转化。AHB总线数据传输具有地址周期和数据周期,AHB的地址和控制信号发送完毕后,下一个周期才发送数据,而sram的写时序是同时输入地址和数据,所以这里对AHB的地址和控制信号做打拍处理。

sram_tb.v跑出来的波形图

生成波形的相关文件,已打包上传至github,请点击跳转,并自行下载!

后记

这是AHB-SRAM项目的架构,如果需要看其他部分,请点击跳转

AHB-SRAM简单设计之架构图解

这篇文章,涉及到的所有文件,已打包上传至博客,请点击跳转,并自行免费下载!

AHB-SRAM简单设计之总线控制单元 ahb_slave_if.v

AHB-SRAM简单设计之内部模块 sram_core.v

AHB-SRAM简单设计之 顶层模块sram_top.v

笔者是小白,自学输出过程中,难免有错误,请大家指正!

github上有一个类似的项目,就是memory_bist不一样,大家可以点击跳转下载