《STM32从零开始学习历程》——SPI物理层及FLASH芯片介绍

《STM32从零开始学习历程》@EnzoReventon

SPI物理层及FLASH芯片介绍

相关链接:

SPI协议层

SPI特性及架构

SPI固件库

参考资料:

[野火EmbedFire]《STM32库开发实战指南——基于野火霸天虎开发板》

[正点原子]STM32F4开发指南-库函数版本_V1.2

[ST]《STM32F4xx中文参考手册》

SPI协议及总线协议介绍

W25Q128产品数据手册

SPI协议介绍

- SPI 协议是由摩托罗拉公司提出的通讯协议(Serial Peripheral Interface),即串行外围设备接口,是一种高速、全双工的通信总线。它被广泛地使用在ADC、LCD 等设备与MCU 间,要求通讯速率较高的场合。

物理层介绍

SS: 从设备选择信号线,常称为片选信号线,也称为NSS,CS。

- 每个从设备都有独立的这一条SS信号线,本信号线独占主机的一个引脚,即有多少个从设备,就有多少条片选信号线。I2C协议中通过设备地址来寻址、选中总线上的某个设备并与其进行通讯;

- 而SPI协议中没有设备地址,它使用SS信号线来寻址,当主机要选择从设备时,把该从设备的SS信号线设置为低电平,该从设备即被选中,即片选有效,接着主机开始与被选中的从设备进行SPI通讯。

- 所以SPI通讯以SS线置低电平为开始信号,以SS线被拉高作为结束信号。

SCK: 时钟信号线,用于通讯数据同步。

- 它由通讯主机产生,决定了通讯的速率,不同的设备支持的最高时钟频率不一样,如STM32的SPI时钟频率最大为fpclk/2(选APB1或APB2,最大为42MHz或者21MHz),两个设备之间通讯时**,通讯速率受限于低速设备**。

MOSI:(Master Output,Slave Input) 主设备输出/从设备输入引脚。

- 主机的数据从这条信号线输出,从机由这条信号线读入主机发送的数据,即这条线上数据的方向为主机到从机。

MISO:(Master Input,Slave Output) 主设备输入/从设备输出引脚。

- 主机从这条信号线读入数据,从机的数据由这条信号线输出到主机,即在这条线上数据的方向为从机到主机。

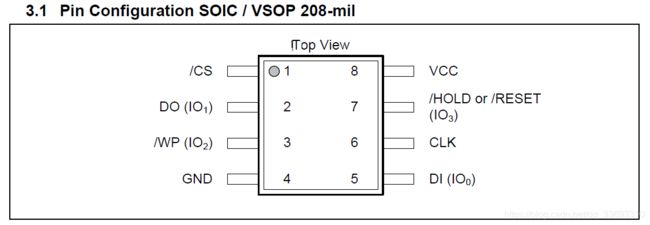

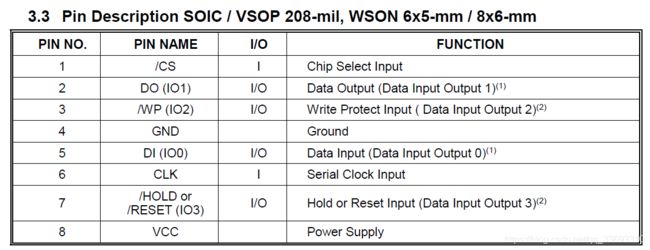

WP:

- 写保护。低电平有效。

HOLD:

- 暂停功能,处理比当前任务更重要的任务时,把当前任务暂停,保持当前状态,先处理另一个任务。

W25Q128产品数据手册解读

W25Q128产品数据手册

The W25Q128FV (128M-bit) Serial Flash memory provides a storage solution for systems with limited space, pins and power. The 25Q series offers flexibility and performance well beyond ordinary Serial Flash devices. They are ideal for code shadowing to RAM, executing code directly from Dual/Quad SPI (XIP) and storing voice, text and data. The device operates on a single 2.7V to 3.6V power supply with current consumption as low as 4mA active and 1μA for power-down. All devices are offered in space-saving packages.

W25Q128FV(128M位,16兆字节)串行闪存为空间、引脚和电源有限的系统提供存储解决方案。25Q系列提供的灵活性和性能远远超过普通串行闪存设备。它们非常适合于将代码存储到RAM中,直接从双/四SPI(XIP)执行代码并存储语音、文本和数据(NOR FLASH)。该装置采用2.7V至3.6V的单电源供电,电流消耗低至4mA,断电时为1μa。所有设备均采用节省空间的包装。

ps:F407芯片内部有一个1MB的NOR FLASH用来存储程序,且不支持将程序存储到外部的NOR FLASH中。

The W25Q128FV array is organized into 65,536 programmable pages of 256-bytes each. Up to 256 bytes can be programmed at a time. Pages can be erased in groups of 16 (4KB sector erase), groups of 128 (32KB block erase), groups of 256 (64KB block erase) or the entire chip (chip erase). The W25Q128FV has 4,096 erasable sectors and 256 erasable blocks respectively. The small 4KB sectors allow for greater flexibility in applications that require data and parameter storage.

W25Q128FV阵列被组织成65536个可编程页,每个页256字节。一次最多可编程256字节。页面可以按16组(4KB扇区擦除)、128组(32KB块擦除)、256组(64KB块擦除)或整个芯片(芯片擦除)擦除(可以按页、字节写入,擦除的最小单位为扇区 4096字节)。W25Q128FV分别有4096个可擦除扇区和256个可擦除块。小的4KB扇区允许在需要数据和参数存储的应用程序中具有更大的灵活性。

The W25Q128FV support the standard Serial Peripheral Interface (SPI), Dual/Quad I/O SPI as well as 2-clocks instruction cycle Quad Peripheral Interface (QPI): Serial Clock, Chip Select, Serial Data I/O0 (DI), I/O1 (DO), I/O2 (/WP), and I/O3 (/HOLD). SPI clock frequencies of up to 104MHz are supported allowing equivalent clock rates of 208MHz (104MHz x 2) for Dual I/O and 416MHz (104MHz x 4) for Quad I/O when using the Fast Read Dual/Quad I/O and QPI instructions. These transfer rates can outperform standard Asynchronous 8 and 16-bit Parallel Flash memories. The Continuous Read Mode allows for efficient memory access with as few as 8-clocks of instruction-overhead to read a 24-bit address, allowing true XIP (execute in place) operation.

W25Q128FV 支持标准串行外围接口(SPI)、双/四I/O SPI 以及2时钟指令循环四外围接口(QPI):串行时钟、芯片选择、串行数据I/O0(DI)、I/O1(DO)、I/O2(/WP)和I/O3(/HOLD)。支持最多104MHz的SPI时钟频率,当使用快速读取双/四输入/四输入/输出和QPI指令时,允许双I/O的等效时钟速率208MHz(104MHz x 2),四I/O的等效时钟速率为416MHz(104MHz x 4)。这些传输速率可以优于标准的异步8位和16位并行闪存。连续读取模式允许高效的内存访问,只需8个时钟的指令开销,即可读取24位地址,从而允许真正的XIP(就地执行)操作。

====================================================================================

STATUS AND CONFIGURATION REGISTERS

Three Status and Configuration Registers are provided for W25Q128FV. The Read Status Register-

1/2/3 instructions can be used to provide status on the availability of the flash memory array, whether

the device is write enabled or disabled, the state of write protection, Quad SPI setting, Security Register

lock status, Erase/Program Suspend status, output driver strength, power-up and current Address

Mode. The Write Status Register instruction can be used to configure the device write protection features,

Quad SPI setting, Security Register OTP locks, Hold/Reset functions, output driver strength and powerup

Address Mode. Write access to the Status Register is controlled by the state of the non-volatile Status

Register Protect bits (SRP0, SRP1), the Write Enable instruction, and during Standard/Dual SPI

operations, the /WP pin.

状态和配置寄存器W25Q128FV提供三个状态和配置寄存器。读取状态寄存器-1/2/3指令可用于提供闪存阵列可用性的状态,无论该设备是写启用或禁用,写保护状态,四SPI设置,安全寄存器锁定状态、擦除/程序挂起状态、输出驱动程序强度、通电和当前地址模式。写状态寄存器指令可用于配置设备写保护功能,四SPI设置,安全寄存器OTP锁,保持/复位功能,输出驱动器强度和通电地址模式。对状态寄存器的写访问由非易失性状态的状态控制寄存器保护位(SRP0、SRP1)、写启用指令和标准/双SPI期间操作,/WP引脚。

S0 BUSY 标志位:表示擦除或者写入操作是否已经完成。(只读)

BUSY is a read only bit in the status register (S0) that is set to a 1 state when the device is executing a Page Program, Quad Page Program, Sector Erase, Block Erase, Chip Erase, Write Status Register or Erase/Program Security Register instruction. During this time the device will ignore further instructions except for the Read Status Register and Erase/Program Suspend instruction (see tW, tPP, tSE, tBE, and tCE in AC Characteristics). When the program, erase or write status/security register instruction has completed, the BUSY bit will be cleared to a 0 state indicating the device is ready for further instructions.

BUSY是状态寄存器(S0)中的只读位,当设备执行页程序、四页程序、扇区擦除、块擦除、芯片擦除、写状态寄存器或擦除/程序安全寄存器指令时,该位被设置为1状态。在此期间,设备将忽略除读取状态寄存器和擦除/程序挂起指令外的其他指令(参见AC特性中的tW、tPP、tSE、tBE和tCE)。当程序、擦除或写入状态/安全寄存器指令完成时,忙位将被清除为0状态,表示设备已准备好接受进一步指令。

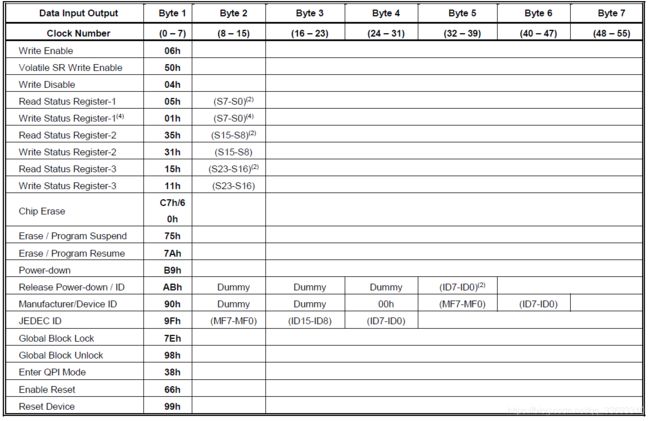

FLASH指令

INSTRUCTIONS

The Standard/Dual/Quad SPI instruction set of the W25Q128FV consists of 45 basic instructions that are fully controlled through the SPI bus (see Instruction Set Table1-2). Instructions are initiated with the falling edge of Chip Select (/CS). The first byte of data clocked into the DI input provides the instruction code. Data on the DI input is sampled on the rising edge of clock with most significant bit (MSB) first.

W25Q128FV的标准/双/四SPI指令集由45条基本指令组成,这些指令通过SPI总线完全控制(见指令集表1-2)。指令通过芯片选择的下降沿(/CS)启动。进入DI输入的第一个数据字节提供指令代码。DI输入端上的数据首先在时钟上升沿进行采样,最高有效位(MSB)。

Instructions vary in length from a single byte to several bytes and may be followed by address bytes, data bytes, dummy bytes (don’t care), and in some cases, a combination. Instructions are completed with the rising edge of edge /CS. Clock relative timing diagrams for each instruction are included in Figures 5 through 57. All read instructions can be completed after any clocked bit. However, all instructions that Write, Program or Erase must complete on a byte boundary (/CS driven high after a full 8-bits have been clocked) otherwise the instruction will be ignored. This feature further protects the device from inadvertent writes. Additionally, while the memory is being programmed or erased, or when the Status Register is being written, all instructions except for Read Status Register will be ignored until the program or erase cycle has completed.

指令的长度从一个字节到几个字节不等,后面可能是地址字节、数据字节、伪字节(不在乎),在某些情况下,还可能是一个组合。指令以edge/CS的上升沿完成。每个指令的时钟相对时序图包含在图5到57中。所有读取指令都可以在任何时钟位之后完成。但是,所有写入、编程或擦除的指令都必须在字节边界上完成(/CS在完成8位时钟后高电平驱动),否则该指令将被忽略。此功能进一步保护设备不受意外写入的影响。此外,当存储器被编程或擦除时,或当状态寄存器被写入时,除读取状态寄存器外的所有指令将被忽略,直到编程或擦除周期完成。