Verilog编程在线练习

目录

- 一、门电路联系

-

- 1.非门问题

- 2.与门

- 3.或非门

- 二、组合逻辑练习

-

- 1.2对1多路复用

- 2.全加器

- 3.卡诺地图

- 三、时序逻辑相关练习

-

- 1.D触发器

- 2.D锁存器

- 3.1~12计数器

- 四、参考资料

以下实验均在HDLBits — Verilog Practice 在线练习网站完成

一、门电路联系

1.非门问题

解决代码

module top_module( input in, output out );

assign out=~in;

endmodule

仿真结果

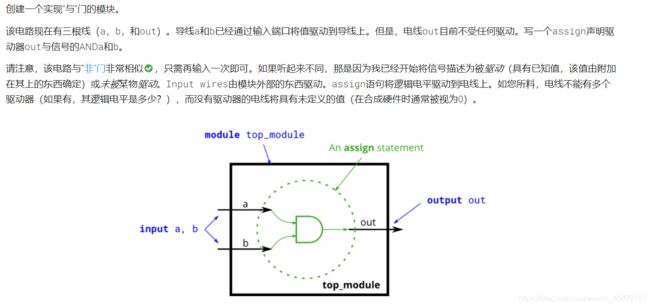

2.与门

问题描述

解决代码

module top_module(

input a,

input b,

output out );

assign out=a&b;

endmodule

仿真结果

3.或非门

问题描述

解决代码

module top_module(

input a,

input b,

output out );

assign out=~(a|b);

endmodule

仿真结果

二、组合逻辑练习

1.2对1多路复用

解决代码

module top_module(

input a, b, sel,

output out );

assign out = (sel) ? b : a;

endmodule

2.全加器

问题描述

解决代码

module top_module(

input a, b, cin,

output cout, sum );

assign{cout,sum} = a + b + cin;

endmodule

仿真结果

3.卡诺地图

问题描述

解决代码

module top_module (

input [4:1] x,

output f );

assign f = (~x[1] & x[3]) | (x[1] & x[2] & ~x[3]);

endmodule

三、时序逻辑相关练习

1.D触发器

解决代码

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

always@(posedge clk) begin

q <= d;

end

endmodule

2.D锁存器

问题描述

解决代码

module top_module (

input d,

input ena,

output q);

always@(*)begin

if(ena)begin

q<=d;

end

end

endmodule

仿真结果

成功

3.1~12计数器

问题描述

解决代码

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

); //

count4 the_counter (clk, c_enable, c_load, c_d /*, ... */ );

reg [3:0] temp;

//4-bit计数器的控制信号

assign c_enable = enable;

//带复位和置位,

assign c_load = reset | (Q == 4'd12 & enable == 1'b1);

assign c_d = 4'b1;

// count4 the_counter (clk, c_enable, c_load, c_d, Q );

count4 Inst_count4

(

.clk(clk),

.enable(c_enable),

.load(c_load),

.d(c_d),

.Q(Q)

);

endmodule

仿真结果

四、参考资料

1.HDLBits在线Verilog编程练习

2.HDLBits 中文导学