i2c总线(iic总线/ I square C)

I2C(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。I2C 总线产生于在80年代,最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。例如管理员可对各个组件进行查询,以管理系统的配置或掌握组件的功能状态,如电源和系统风扇。可随时监控内存、硬盘、网络、系统温度等多个参数,增加了系统的安全性,方便了管理。

1 I2C总线特点

I2C总线最主要的优点是其简单性和有效性。由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。总线的长度可高达25英尺(762cm),并且能够以10Kbps的最大传输速率支持40个组件。I2C总线的另一个优点是,它支持多主控(multimastering), 其中任何能够进行发送和接收的设备都可以成为主总线。一个主控能够控制信号的传输和时钟频率。当然,在任何时间点上只能有一个主控。

2 I2C总线工作原理

2.1 总线的构成及信号类型

I2C 总线是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。在CPU与被控IC之间、IC与IC之间进行双向传送,最高传送速率 100kbps。各种被控制电路均并联在这条总线上,但就像电话机一样只有拨通各自的号码才能工作,所以每个电路和模块都有唯一的地址,在信息的传输过程中,I2C总线上并接的每一模块电路既是主控器(或被控器),又是发送器(或接收器),这取决于它所要完成的功能。CPU发出的控制信号分为地址码和控制量两部分,地址码用来选址,即接通需要控制的电路,确定控制的种类;控制量决定该调整的类别(如对比度、亮度等)及需要调整的量。这样,各控制电路虽然挂在同一条总线上,却彼此独立,互不相关。

I2C总线在传送数据过程中共有三种类型信号, 它们分别是:开始信号、结束信号和应答信号。

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为低电平时,SDA由低电平向高电平跳变,结束传送数据。

应答信号:接收数据的IC在接收到8bit数据后,向发送数据的IC发出特定的低电平脉冲,表示已收到数据。CPU向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU接收到应答信号后,根据实际情况作出是否继续传递信号的判断。若未收到应答信号,由判断为受控单元出现故障。

目前有很多半导体集成电路上都集成了I2C接口。带有I2C接口的单片机有:CYGNAL的 C8051F0XX系列,PHILIPSP87LPC7XX系列,MICROCHIP的PIC16C6XX系列等。很多外围器件如存储器、监控芯片等也提供I2C接口。

2 I2C总线的基本原理

2.1 I2C总线基本结构

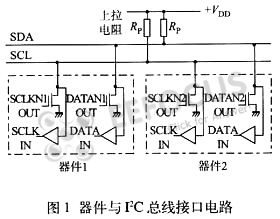

I2C总线系统结构灵活,易于模块化、标准化设计。I2C总线只有两根信号线,一根是数据线SDA,另一根是时钟线SCL。所有进入I2C总线系统中的器件都带有I2C总线接口,符合I2C总线电气规范的特性;而且采用纯软件寻址方法,无需器件片选线的连接。CPU不仅能通过指令将某个功能器件挂靠或摘离总线,还可对其工作状况进行检测,从而实现对硬件系统即简单又灵活的扩展与控制。各器件供电可不同,但需共地。另外,SDA、SCL需分别接上拉电阻。

SDA、SCL都是双向的,输出电路用于向总线上发送数据,输入电路用于接收总线上的数据。当总线空闲时,两根线都是高电平。连接总线的器件的输出端电路必须是集电极开路输出或开漏输出,以具有线“与”功能。I2C总线的数据传送速率在标准模式下可达100kbit/s,快速模式下可达400kbit/s,高速模式下则可达3.4Mbit/s。

I2C总线接口电路结构如图1所示。

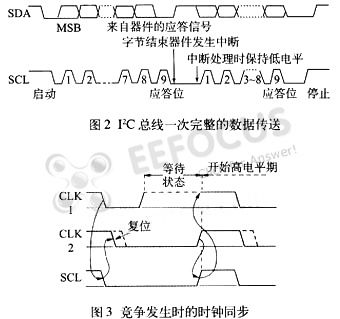

2.2 I2C总线数据传送

I2C总线数据传输时必须遵循规定的数据传送格式,如图2所示为一次完整的数据传送格式。启动信号表明一次传送的开始,其后为寻址字节,该寻址字节由高7位地址和最低1位方向位组成:方向位为“0”表明写操作,“1”表明读操作;在寻址字节后是由方向位指定读、写操作的数据字节与应答位;在数据传送完成后为停止信号。在“启动”与“停止”之间传送的数据字节数从理论上来说没有限制,但每个字节必须为8位,而且每个传送的字节后面必须跟一个应答位。

当SCL为高电平时,SDA由高电平跳变为低电平,定义为启动信号;当SCL为低电平时,SDA由低电平跳变为高电平,定义为停止信号。

在SCL为高电平时,SDA上数据需保持稳定方被认为有效;只有在SCL为低电平时,才允许SDA电平状态变化。

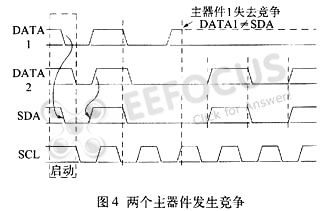

2.3时钟信号的同步

在I2C总线上传送信息时的时钟同步信号是由挂接在SCL线上的所有器件的逻辑“与”完成的。SCL线上由高电平到低电平的跳变将影响到这些器件,一旦某个器件的时钟信号下跳为低电平,将使SCL线一直保持低电平,使SCL线上的所有器件开始低电平期。此时,低电平周期短的器件的时钟由低至高的跳变并不能影响SCL线的状态,于是这些器件将进入高电平等待的状态。当所有器件的时钟信号都上跳为高电平时,低电平期结束,SCL线被释放返回高电平,即所有的器件都同时开始它们的高电平期。其后,第一个结束高电平期的器件又将SCL线拉成低电平。这样就在SCL线上产生一个同步时钟。可见,时钟低电平时间由时钟低电平期最长的器件确定,而时钟高电平时间由时钟高电平期最短的器件确定。

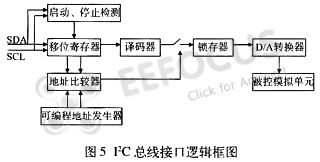

2.4 总线竞争的仲裁

总线上可能挂接有多个器件,有时会发生两个或多个主器件同时想占用总线的情况,这种情况叫做总线竞争。I2C总线具有多主控能力,可以对发生在SDA线上的总线竞争进行仲裁,其仲裁原则是这样的:当多个主器件同时想占用总线时,如果某个主器件发送高电平,而另一个主器件发送低电平,则发送电平与此时SDA总线电平不符的那个器件将自动关闭其输出级。总线竞争的仲裁是在两个层次上进行的。首先是地址位的比较,如果主器件寻址同一个从器件,则进入数据位的比较,从而确保了竞争仲裁的可靠性。由于是利用I2C总线上的信息进行仲裁,因此不会造成信息的丢失。

3 I2C总线接口逻辑的构成

3.1 I2C总线接口电路的结构

I2C总线接口逻辑框图如图5所示。

在电路设计中,各功能块的硬件实现介绍如下。

启动、停止检测电路应用两个D触发器来分别响应SDA在SCL为高电平时的电平跳变。

移位寄存器电路由9个D触发器串联成9级移位寄存器,包括8位字节和1位应答位,实现SDA上数据的串并行转换。寄存器复位值为“111111110”,接收8位字节后为“0D7D6D5D4D3D2D1D0”,即应答位为“0”,在第9个时钟时输出低电平作为应答信号。

可编程地址发生器电路生成器件地址,7位器件地址由器件编号地址(高4位)和引脚地址(低3位)组成。通过改变器件引脚的连接方式,就可改变器件地址,因此使应用方便灵活。

地址比较器电路由门电路组成布尔代数式逻辑,对寻址字节进行判断。若地址正确则将RS触发器置“1”,使能译码器输出。

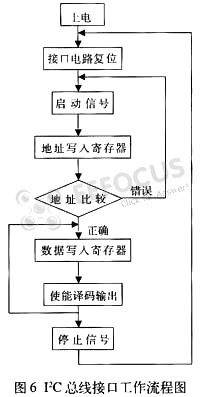

3.2 I2C总线接口工作流程

I2C总线接口工作流程如图6所示。

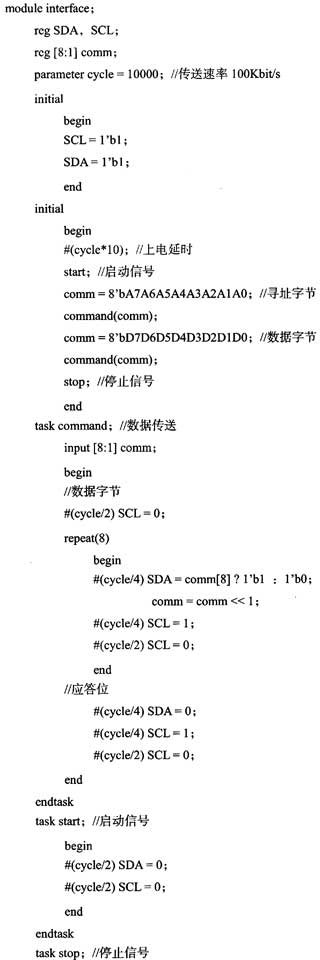

3.3 Verilog仿真程序

4 结束语

目前采用I2C技术的单片机以及外围器件已广泛应用于家用电器、通讯设备及各类电子产品中,而且应用范围将会越来越广。

本文简单介绍了I2C总线接口电路,希望对相关从业人员有所帮助。

3 总线基本操作

I2C规程运用主/从双向通讯。器件发送数据到总线上,则定义为发送器,器件接收数据则定义为接收器。主器件和从器件都可以工作于接收和发送状态。总线必须由主器件(通常为微控制器)控制,主器件产生串行时钟(SCL)控制总线的传输方向,并产生起始和停止条件。SDA线上的数据状态仅在SCL为低电平的期间才能改变,SCL为高电平的期间,SDA状态的改变被用来表示起始和停止条件。参见图1。

3.1 控制字节

在起始条件之后,必须是器件的控制字节,其中高四位为器件类型识别符(不同的芯片类型有不同的定义,EEPROM一般应为1010),接着三位为片选,最后一位为读写位,当为1时为读操作,为0时为写操作。如图2所示。

3.2 写操作

写操作分为字节写和页面写两种操作,对于页面写根据芯片的一次装载的字节不同有所不同。关于页面写的地址、应答和数据传送的时序参见图3。

3.3 读操作

读操作有三种基本操作:当前地址读、随机读和顺序读。图4给出的是顺序读的时序图。应当注意的是:最后一个读操作的第9个时钟周期不是“不关心”。为了结束读操作,主机必须在第9个周期间发出停止条件或者在第9个时钟周期内保持SDA为高电平、然后发出停止条件。

三.基本操作

下面我们以ATMEL公司的AT24C02来介绍I2C的基本操作

AT24C02是美国ATMEL公司的低功耗CMOS串行EEPROM,它是内含256×8bit存储空间,具有工作电压宽(2.5~5.5V)、擦写次数多(大于10000次)、写入速度快(小于10ms)等特点。他在系统中始终为从动器件。

对AT24C02的操作主要有:字节读,字节写,页面读,页面写

首先发送起始信号,如下图,起始信号后必须是控制字,

控制字格式如下,其中高四位为器件类型识别符(不同的芯片类型有不同的定义,EEPROM一般应为1010),接着三位为片选,也就是三个地址位,最后一位为读写控制位,当为1(Input)时为读操作,为0(Output)时为写操作。

控制字后就是相应的操作,读或写,一定不要结束,因为这个操作还没有完成,如果结束就等于放弃操作。

先来看写操作,写操作分为字节写和页面写两种操作,对于页面写根据芯片的一次装载的字节不同有所不同,AT24C02为8字节,每写一个字节后,地址自动加1。关于页面写的地址、应答和数据传送的时序参见图3,字节写可以看成是只有一个字节的页面写,也就是写一个数据后停止。注意:写一次需要一定时间,一般为10ms,要等侍这个操作完成。时序如下图:

说明:对于AT24C02,在控制字后还必须写入地址,这个地址是以后读写的起始地址。

读操作有三种基本操作:当前地址读、随机读和顺序读。三种操作方法类似,只是读的数据个数不同,可连续读8个字节,图4给出的是顺序读的时序图,图中共读了四个数据,需要注意的是当前的地址,如果不是想要的,可以用写操作,重新写入地址。非常重要的是,每读一个数据后,必须置低SDA,作为应答,否则,只能读一个数据,后面的数据,因为收到不应答信号,AT24C02就会认为出错,停止操作。特别提醒的是,当SCL为低电平时,数据是可变的,因些只有SCL为高电平时,才能读数。(相关时序,请看例程序的,读功能函数)

4 实例:X24C04与MCS-51单片机软硬件的实现

X24C04是XICOR公司的CMOS 4096位串行EEPROM,内部组织成512×8位。16字节页面写。与MCS-51单片机接口如图5所示。由于SDA是漏极开路输出,且可以与任何数目的漏极开路或集电极 开路输出“线或”(wire-Ored)连接。上拉电阻的选择可参考X24C04的数据手册。下面是通过I2C接口对X24C04进行单字节写操作的例程。流程图及源程序如下:

;名称:BSENT

;描述:写字节

;功能:写一个字节

;调用程序:无

;输入参数:A

;输出参数:无

BSEND: MOV R2,#08H ;1字节8位

SENDA: CLR P3.2 ;

RLC A ;左移一位

MOV P3.3,C ;写一位

SETB P3.2

DJNZ R2,SENDA ;写完8个字节?

CLR P3.2 ;应答信号

SETB P3.3

SETB P3.2

RET

5 结束语

在I2C总线的应用中应注意的事项总结为以下几点 :

1) 严格按照时序图的要求进行操作,

2) 若与口线上带内部上拉电阻的单片机接口连接,可以不外加上拉电阻。

3) 程序中为配合相应的传输速率,在对口线操作的指令后可用NOP指令加一定的延时。

4) 为了减少意外的干扰信号将EEPROM内的数据改写可用外部写保护引脚(如果有),或者在EEPROM内部没有用的空间写入标志字,每次上电时或复位时做一次检测,判断EEPROM是否被意外改写。