一文认识PYNQ

以下内容摘自正点原子的:《领航者 ZYNQ 之 PYNQ 开发指南》

PYNQ 可以认为是 Python+ZYNQ,但不是简单的相加。在使用上,可以说 PYNQ 开发是 ZYNQ 开发的集大成,也可以说 PYNQ 是 ZYNQ 的全栈式开发,里面涉及到的内容不仅包括 FPGA 设计、PS 与 PL 的协同交互、HLS、linux 驱动开发,而且还要熟悉 Python开发并且使用 Python 各种库。

PYNQ 是 Xilinx 推出的一个开源项目,目的是使用 Python 开发 Xilinx 平台更加容易。使用 Python 语言和库,设计人员可以利用 Xilinx SOC 器件如 ZYNQ 的可编程逻辑 PL 和微处理器 PS 的优势来构建功能更强大的电子系统。PYNQ 可与 Zynq、Zynq UltraScale +、Zynq RFSoC、Alveo 加速卡以及 AWS-F1 一起使用,以创建高性能应用程序,如并行硬件执行、高帧率视频处理、硬件加速算法以及实时信号处理等。

一、PYNQ 是什么

很多人会认为 PYNQ 是一款开发板,比如 Pynq Z1 开发板。其实呢,PYNQ 是 Python Productivity for Zynq 的缩写,即 Zynq 的 Python 生产力,可以认为 PYNQ=Python + ZYNQ,是 Xilinx 推出的一种开放源代码框架,使用 Python 语言和库,使设计人员可以利用 zynq 中可编程逻辑和微处理器的优势来快速构建高性能的嵌入式应用程序。

PYNQ 的主要目标是使嵌入式系统的设计人员更容易在其应用程序中利用 Xilinx 器件的独特优势。具体来说,PYNQ 使设计嵌入式系统的架构师、工程师和程序员可以使用 Zynq 器件,而不必使用 ASIC 风格的设计工具来设计可编程逻辑电路。PYNQ 通过三种方式实现此目标:

-

可编程逻辑电路作为名为 overlay 的硬件库提供。这些 overlays 类似于软件库。软件工程师可以选择最适合其应用程序的 overlay,并且可以通过应用程序编程接口(API)访问 overlay。创建新的overlay 仍然需要具有设计可编程逻辑电路专业知识的工程师。然而,关键的区别是一次构建,多次使用。Overlay 像软件库一样,被设计为可配置并在许多不同的应用程序中尽可能频繁地重复使用。

注:这是一种从软件社区的最佳实践中借鉴来的方法。每天,成千上万的嵌入式设计人员都使用 Linux内核。内核由不到一千名高技能的软件架构师和工程师开发和维护。这些相对少量的才华横溢的工程师的工作被大量重复使用,使更多的软件工程师可以进行更高级别的抽象。硬件库或 overlay 的灵感来自 Linux内核模型的成功,该模型成功地提取了底层的、与硬件相关的软件的许多细节。 -

PYNQ 使用 Python 对嵌入式处理器和 overlay 进行编程。Python 是一种“生产力级别”的语言。迄今为止,C 或 C++是最常见的嵌入式编程语言。相反,Python 提高了编程抽象水平和程序员的生产力。但是,这些不是互斥的选择。PYNQ 使用用 C 编写的 CPython,并集成了成千上万的 C 库,并且可以使用用 C 编写的优化代码进行扩展。在可行的情况下,应使用生产力更高的 Python 环境,并且在效率要求时,可以使用较低级别的 C 代码。

-

PYNQ 是一个开源项目,旨在在任何计算平台和操作系统上工作。通过采用基于 Web 的体系结构可以实现此目标,该体系结构与浏览器无关。PYNQ 并入了开源的 Jupyter notebook 基础架构,以直接在 Zynq 设备的 ARM 处理器上运行 Interactive Python(IPython)内核和 Web 服务器。Web 服务器通过一组基于浏览器的工具代理访问内核,这些工具提供了 dashboard、bash 终端、代码编辑器和 Jupyter notebooks。浏览器工具通过 JavaScript、HTML 和 CSS 的组合实现,并且可以在任何现代浏览器上运行。

总而言之,PYNQ 是第一个结合以下要素来简化和改进 APSoC 设计的项目:

- 一种高级生产力语言(Python)

- 带有全面 API 的 FPGA overlays 公开为 Python 库

- 由嵌入式处理器提供服务的基于 Web 的体系结构,以及在嵌入式上下文中部署的 Jupyter Notebook框架

需要说明的是PYNQ并不是通过Python语言直接对FPGA进行编程。笔者相信很多人第一次听说PYNQ时会觉得 PYNQ 可直接对 FPGA 进行编程以实现硬件加速。事实上,在 PYNQ 框架下并不能通过 Python 对FPGA 进行编程来取代传统的 RTL 编程方式。PYNQ 框架是为软件开发者提供了访问 FPGA 资源的 Python接口,Python 开发者可以忽略这些实现细节,通过 Python 即可轻松访问 FPGA,动态加载各种预编译好的各种 FPGA 应用,像调用函数一样去调用各种通过 FPGA 加速的应用或者访问连接到 FPFA 的外设。让软件工程师能轻松享受 FPGA 并行计算和可灵活配置的诸多好处。至于各种 FPGA 应用,依然需要专业的硬件工程师使用 Vivado 工具进行开发。

二、PYNQ 架构

PYNQ 作为一个开源框架,其设计初衷是通过高层次的封装,将底层硬件 FPGA 实现细节与上层应用层的使用脱耦,对软件开发者来说,PYNQ 框架已经提供了完整的访问 FPGA 资源的 library,让上层应用开发者通过 Python 编程就可以调用 FPGA 模块,不需要懂 Verilog/VHDL 硬件编程就可以享受 FPGA 可并行计算、接口可方便扩展和可灵活配置带来的诸多好处。

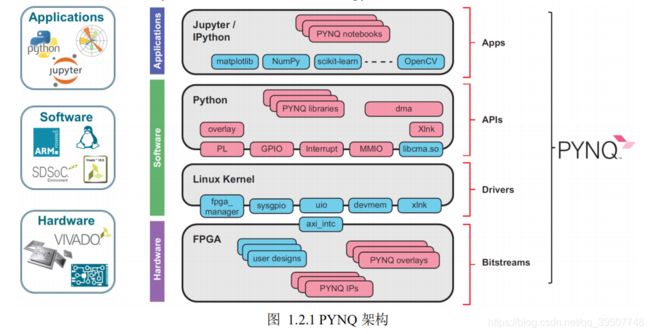

PYNQ 架构如图 1.2.1 所示,从该图可以看到,PYNQ 系统架构分为三层,分别是以 FPGA 设计为主的硬件层、以 linux 内核加 Python 为主的软件层,以及以 Jupyter Notebook 为主的应用层。

硬件层的设计与嵌入式设计方法相同,实现 PS 与 PL 的协同交互。整个 FPGA 部分的设计被称为 overlay,可面向多用户、多应用生成不同的 bitstream 文件,并可以通过软件 API 进行调用,动态的切换 FPGA 上的逻辑功能。

软件层运行在 ZYNQ 的 PS 中,主要由 Ubuntu 操作系统和构建在 Ubuntu 操作系统中的 Python 构成。PYNQ 的 API 库则起到了连接软硬件的作用,使我们可以通过 Python 访问 FPGA 侧的处理单元。

应用层主要由运行在 Python 之上的 Jupyter Notebook 和 IPython 构成。Jupyter Notebook 是一个基于浏览器的交互式计算环境,基于 Python 内核和 Websocket 协议。在 Jupyter Notebook 提供的环境中,可以在其中记录代码、运行代码并查看结果,可视化数据分析并查看输出结果。这些特性使其成为一款执行端到端数据科学工作流程的便捷工具,可以用于数据清理、统计建模、构建和训练机器学习模型,可视化数据以及许多其他用途。通过 Jupyter 创建的交互式 notebook 文档,支持实时代码、交互式小部件、绘图、Markdown、方程式、图像和视频。该工具近年来成为大数据分析以及机器学习领域最火热的工具之一,近三年 github 上传的 notebook 文档数量超过 230 万份!

Jupyter Notebook 在网络浏览器中运行。只需一个兼容的 Web 浏览器即可开始使用 Python 进行 PYNQ编程,从而最终实现通过电脑主机的浏览器访问 Jupyter Notebook,就可以对 PYNQ 进行软件部分的开发。

可见,PYNQ 应用同时包含了硬件设计和软件驱动,比如 PL bitstreams 和 Python 包,用户必须要同时部署这两部分内容才能顺利运行起来。

图 1.2.2 的 PYNQ 框架构成正好简洁地表达了 PYNQ 整体的框架与使用。图 1.2.2 左侧是电脑主机和运行在电脑主机中的浏览器,浏览器中运行的 Jupyter Notebook 与右侧运行在 ZYNQ 或 ZU+中的 Jupyter web server 进行交互。

从图 1.2.2 中,我们也可以看到 PYNQ 是基于 Ubuntu 发行版的 linux 系统构建的。

从图 1.2.4 可以看到,PYNQ 使用基于 Ubuntu 的 linux 系统最大的好处是可以使用 Ubuntu 的根文件系统,从而可以使用 Ubuntu 的包管理工具——apt。换种角度就是 PYNQ 可以使用 Ubuntu 所有的软件库。鉴于 Ubuntu 的流行,以及强大的社区和官方支持,Ubuntu 几乎囊括了所有的Linux 软件和库,从而为开发者省去了移植各种软件和库的麻烦。虽然牺牲了部署效率,但极大的加快了开发速度,从而促进开发人员的生产力。

总而言之,PYNQ 最重要的特点是可以使用 Python 进行编程,并且提供了基于 Web 访问的 Jupyter Notebook 在线编辑工具。运行在 Arm 处理器上的基于 Ubuntu 的 Linux 系统为 PYNQ 提供了软件基础平台,Python 环境以及 Jupyter Notebook 工具都在其上。

启用 PYNQ 的开发板不仅可以使用 Python 在 Jupyter Notebook 中轻松编程,而且使用 Python,开发人员可以在 PL 上使用硬件库或 overlay。硬件库或 overlay 可以加快在 Zynq 或 ZU+开发板上运行的软件的速度,并自定义硬件平台和接口。

三、PYNQ 适用于谁

谈论该话题之前,我们先看下下面这张图(图片来源于 Xilinx):

对比从事于 Vivado 设计的硬件工程师,可以看到从事 ARM 和 C/C++的嵌入式软件工程师与从事于python 相关的 Domain experts 人数都相对较多,其中 Domain experts 人数最多。有鉴于此,PYNQ 旨在为广泛的设计人员和开发人员所使用,包括:

➢ 想要利用 Xilinx 平台的功能而无需使用 ASIC 风格的设计工具来设计硬件的软件开发人员。

➢ 需要简单的软件界面和框架来快速进行 Zynq、Alveo 和 AWS-F1 设计原型开发的系统设计师。

➢ 希望其设计尽可能被广泛的受众使用的硬件设计师。

四、Overlay 是什么

Overlay 也可称为硬件库,是 ZYNQ 的 PL(FPGA)设计,可将用户应用程序从 Zynq 的处理系统 PS 扩展到可编程逻辑 PL。Overlay 可用于加速软件应用程序,也可为特定应用程序定制硬件平台。

例如,图像处理是 FPGA 可以提供加速的典型应用。软件程序员可以以类似于软件库的方式使用 overlay,以在 FPGA 架构上运行某些图像处理功能(例如,边缘检测,阈值处理等)。Overlay 可以根据需要动态加载到 FPGA,就像软件库一样。对于图像处理而言,可以在不同的 overlay 中实现单独的图像处理功能,并按需从 Python 中加载。

PYNQ 提供了一个 Python 界面,允许通过 PS 中运行的 Python 控制 PL 中的 overlay。由于 FPGA 设计是一项专门的任务,需要硬件工程知识和专业知识,所以 PYNQ overlay 由硬件设计人员创建,并使用 PYNQ Python API 包装。然后,软件开发人员可以使用 Python 接口来编程和控制 overlay,而无需自己设计 overlay。这类似于由专家开发人员创建的软件库,然后由应用程序级别的许多其他软件开发人员使用。

默认情况下,在启动时将称为 base 的overlay(bitstream)下载到 PL 中。可以将 base overlay 视为开发板的参考设计。新的 overlay 可以上传或复制到开发板上,并且可以在系统运行时加载到 PL 中。

Overlay 通常包括以下三个部分:

➢ 用于配置 FPGA 架构的 bitstream 文件

➢ 确定 Vivado 设计可用 IP 的 hwh 文件(早期使用 Tcl 文件)

➢ 将 IP 公开为属性的 Python API(归属于 PYNQ 库)

PYNQ Overlay 类可用于加载 overlay。通过指定 bitstream 文件的名称来实例化 overlay。实例化 overlay会默认下载 bitstream 文件(此处以 base.bit 为例)并解析 hwh 文件(早期为 Tcl 文件)。加载 overlay 的代码如下:

from pynq import Overlay

overlay_design = Overlay("base.bit")

实例化 overlay 后,可以使用 help()方法了解 overlay_design 中的内容,如help(overlay_design)。输出的帮助信息可用于与 overlay 进行交互。

五、PYNQ 学习资源汇总

PYNQ 官方网站:http://www.pynq.io/

PYNQ 官方说明文档:https://pynq.readthedocs.io/en/latest/

PYNQ 源码:https://github.com/xilinx/pynq

PYNQ 官方 workshop:https://github.com/Xilinx/PYNQ_Workshop