组原第四章作业

第四章

P.S. 因为未改,不确定对,发现错误一定要告诉我。。

- 第四章

-

- 一.单选题

- 二.多选题

- 三.填空题

- 四.判断题

- 五.简答题

- 六.分析题

一.单选题

1、主机和设备传送数据时,采用(),主机与设备是串行工作的。

A、程序查询方式

B、中断方式

C、DMA方式

D、以上答案均不正确

答案:A

多数外设的工作状态不可预测,CPU需要定时对设备的状态进行查询——程序查询

程序查询控制方式的不足:

- CPU进行I/O控制的工作效率很低

- 只适合于预知或预先估计到的I/O事件

- 只能允许CPU与外设串行工作

2、DMA是在( )之间建立的直接数据通路。

A、CPU与外设

B、主存与外设

C、外设与外设

D、CPU与主存

答案:B

3、在链式查询方式下,若有n个设备,则 ( )。

A、有几条总线请求信号

B、公用一条总线请求信号

C、有n-1条总线请求信号

D、无法确定

答案:B

链式查询方式:

优点:1.自动支持优先级 2. 连接简单,易于扩充设备

缺点:1.对电路故障很敏感2.优先级低的设备获得总线的使用权会很难。

4、在I/O过程控制方式中,有多设备、多批次数据传送时,( )方式下CPU的负担最重。

A、程序查询

B、程序中断

C、DMA

D、通道

答案:A

5、中断允许触发器是用来()。

A、表示外设是否提出了中断请求

B、CPU是否响应了中断

C、CPU是否正在进行中断过程

D、开放或关闭可屏蔽中断

答案:D

中断接口各触发器的主要作用为:

(1)中断请求触发器:暂存中断请求线上由设备发出的中断请求信号。此标志为“1”时表示设备发送了中断请求。

(2)中断屏蔽触发器:CPU是否可以响应中断的标志。中断屏蔽触发器为“0”时,CPU可以响应外界的中断。

(3)中断允许触发器:控制是否允许某设备发出中断请求,为“1”时,某设备可以向CPU发送中断请求。

(4)准备就绪状态触发器:一旦设备做好一次数据的接收或发送,便发送一个设备动作完毕信号,使触发器标志为“1”。

(5)忙状态触发器:该标志为“1”时设备正在工作。

6、周期挪用方式常用于( )方式的输入/输出中。

A、程序传送

B、中断

C、DMA

D、通道

答案:C

7、如果有多个中断请求同时发生,系统将响应中断优先级最高的中断请求。若要调整中断事件的响应次序,可以利用()。、

A、中断嵌套

B、中断向量

C、中断响应

D、中断屏蔽

答案:C

二.多选题

1、I/O设备与主机之间的联络方式包括()。

A、立即响应

B、异步工作采用应答信号

C、同步工作采用同步时标

D、以上答案都不正确

答案:ABC

2、I/O过程的程序直接控制的特点( ):

A、是I/O过程完全处于CPU指令控制下

B、外部设备的有关操作都要由CPU指令直接指定

C、外设随时可以接收数据,永远与CPU同步

D、数据输入输出的控制程序比较复杂

答案:ABC

直接程序传送方式用于系统调试或对速度要求不高的系统。

这种方式CPU通过执行I/O指令控制外设工作,查询外设状态并和外设交换数据,

优点:接口结构简单,实现容易。

缺点:由于CPU和外设串行工作,系统效率低

三.填空题

1、I/O 设备编址方式有统一编址和( )编址。

答案:不统一

2、在可以响应中断的条件下,CPU暂时中止正在执行的程序,转去执行( )程序。

答案:中断服务

3、在中断控制方式下,CPU 和 I/O 是( )行工作(串/并)

答案:并

4、在DMA方式中,CPU与DMA各自能独立地工作:CPU执行程序,DMA控制( )过程。

答案:输入输出

四.判断题

1、接口的功能是,实现高速CPU和低速外设间的速度匹配和同步( )

答案:√

2、总线连接的情况下,CPU和I/O设备并行工作方式包括:中断方式和DMA方式。( )

答案:√

3、DMA方式只能满足高速I/O设备的要求,不利于CPU效率的发挥( )

答案:×

4、主程序运行时,何时转向为外设服务的中断服务程序是预先安排好的。

答案:×

5、DMA方式进行外设与主机交换信息时,不需要向主机发出中断请求。

答案:×

6、一旦中断请求出现,CPU立即停止当前指令的执行,转去受理中断请求。

答案:×

7、DMA控制器和CPU可同时使用总线。

答案:×

8、中断请求信号IRQ源自于设备的状态就绪标志位RD。

答案:√

五.简答题

1、在中断处理的过程中,执行中断服务前后为什么需要保护和恢复现场和断点,现场和断点的具体内容是什么?存放在什么地方了?

答案:

现场:中断发生前程序的运行状态, 一般主要指系统标志寄存器中的内容。

断点:被中断的主程序的下一条待运行的指令的存放地址。

存储到堆栈

六.分析题

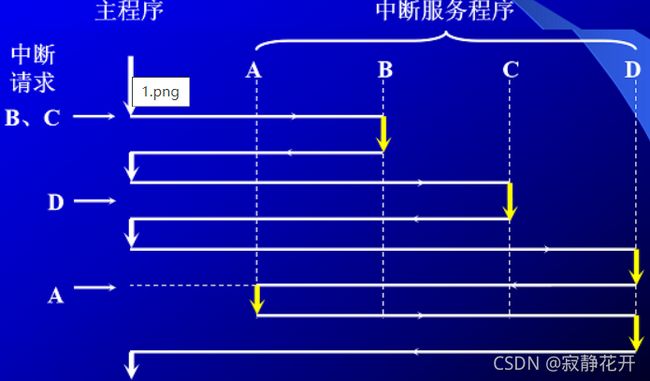

1、图中A、B、C、D是4个中断源,请根据它们的中断请求时间和CPU响应的先后顺序,以此判断出A、B、C、D的中断优先级。

答案:

中断优先级从高到低分别是:BCAD(A和B的优先级无法判断,其他答案也是对的)