systemverilog-数组和队列

文章目录

- 1.定宽数组

-

- 1.1 定宽数组的声明与初始化

- 1.2 Packed array(合并数组)

- 1.3 Upacked array(非合并数组)

- 2.动态数组

- 3.关联数组

- 4.数组的方法

-

- 4.1 数组定位方法

- 4.2 数组的排序方法

- 4.3 数组缩减

- 5.队列

1.定宽数组

Verilog要求在声明定宽数组时必须给出数组的上下界,在system verilog中可以只给出数组宽度。

1.1 定宽数组的声明与初始化

- 对于定宽数组采用单引号加大括号来初始化数组 '{ }

- 可以在大括号前标上重复次数来对多个元素重复赋值 '{4{ }}

- 为没有显示赋值的元素指定一个缺省值 default:

int c_style[4];

c_strle = '{

0,1,2,3};

int array1[2][3];

array1 = '{'{

0,1,2},'{

3,4,5}};

int decend[5];

decend = '{

0,1,2,3,4};

decend[0:2] = '{

0,1,2};//为前三个元素赋值

decend = '{

5{

9}}; //{9,9,9,9,9}

decend = '{

5,6,default:1}; //{5,6,1,1,1}

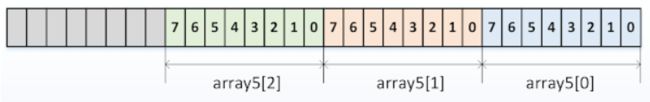

1.2 Packed array(合并数组)

- 一维的packed array也被称为Vector;

- 一个packed array被表示为一个连续的位集合

- 数组大小定义的格式必须是[msb:lsb],而不是[size]

在存储时是连续的:

bit[2:0] [7:0] array5 //定义3个8bit的合并数组

1.3 Upacked array(非合并数组)

非合并数组:

- 可以是任意数据类型

- 定义数组大小在名字之后

- 在存储上bit组是不连续的

在存储时是不连续的:

bit[7:0] array4[2:0]

bit[7:0] array4[3] //定义3个8bit的非合并数组

bit[3:0] [7:0] barray[3]; //生成具有3个合并元素的非合并数组

2.动态数组

动态数组可以在仿真时分配空间或调整数组宽度

- 动态数组在声明时使用空的下标 [ ]

- 调用 new[ ] 操作符来分配空间

- size() 返回动态数组当前的大小

- delete() 清空数组,生成大小为零的数组

int dyn[],d2[];//声明动态数组

initial begin

dyn = new[5]; //分配5个元素

foreach (dyn[j]) dyn[j] = j;//对元素进行初始化

d2 = dyn;//复制动态数组

d2[0] = 5;//修改复制值

dyn = new[100];//分配100个新的整数值

dyn.delete();//删除所有元素

end

3.关联数组

SystemVerilog提供了关联数组类型,用来保存稀疏矩阵的元素。这意味着当你对一个非常大地址空间进行寻址时,SystemVerilog只为实际写入的元素分配空间。

类似哈希数组

- 将内容存储在稀疏矩阵

- 关联数组只有在使用时才分配存储空间

- 关联数组为数组元素分配一个查找表,其中索引作为键

- 关联数组初始化使用:’{} 在大括号内写入键值对的信息,键值对用 : 连接

- 关联数组的大小可以使用size()、num()来实现,没有写入数据时,大小为0

int data_as[bit [31:0]]

int为存储数据类型,bit[63:0]为寻址的类型

data_as = '{

1:20,2:21,3:22};

if(data_as.first(data_index))begin

do

begin

$diaplay("data_as[0x%0d] is 0x%0d",data_index, data_as[data_index]);

end

while(data_as.next(data_index));

end

输出:

data_as[0x0] is 0x20

data_as[0x1] is 0x21

data_as[0x2] is 0x22

方法:

| 方法 | 描述 |

|---|---|

| .num() | 返回元素个数 |

| .delete(index) | 删除index索引的键和值,如果不加index则删除所有键和值 |

| .exists(index) | 检查index键是否在数组中 |

| .first(var) | 将第一个键赋给var |

| .last(var) | 将最后一个键赋给var |

| .next(var) | 将下一个键赋给var,如果后面没有键,则返回最后一个键 |

| .prev(var) | 将上一个键赋给var,如果前面没有键,则返回第一个键 |

4.数组的方法

4.1 数组定位方法

想要在非合并数组中查找数据,可以使用数组定位方法,数组定位方法会搜索满足expression的数组元素或者数组索引,这些方法的返回值通常是一个队列

- 不使用with表达式,这些方法同样适用于合并数组

| 方法 | 描述 |

|---|---|

| min() | 返回最小元素组成的队列 |

| max() | 返回最大元素组成的队列 |

| unique() | 返回数组具有唯一值的队列,即重复值只留下一个 |

int f[6] = '{

1,6,2,6,8,6};

int tq[$];

tq = f.min();//1

tq = f.max();//{8}

tq = f.unique();//{1,2,6,8}

- 数组定义方法find,带with表达式

| 方法 | 描述 |

|---|---|

| find() | 返回所有满足with表达式的元素 |

| find_index() | 返回所有满足with表达式的元素索引 |

| find_first() | 返回满足with表达式的第一个元素 |

| find_first_index() | 返回满足with表达式的第一个元素索引 |

| find_last() | 返回满足with表达式的最后一个元素 |

| find_last_index() | 返回满足with表达式的最后一个元素索引 |

int d[] = '{

9,1,8,3,4,4};

int tq[$];

tq = d.find with (item > 3);//{9,8,4,4}

tq = d.find_index with (item > 3);//{0,2,4,5}

tq = d.find_first with (item > 99);//{}

tq = d.find_first_index with (item == 8);//{2}

4.2 数组的排序方法

数组支持以下排序方法:

| 方法 | 描述 |

|---|---|

| revert() | 对数组中的元素进行逆排序,此方法不能与with条件语句一起使用。 |

| sort() | 按升序对数组进行排序 |

| rsort() | 按降序对数组进行排序 |

| shuffle() | 按随机顺序对数组进行排序,此方法不能与with条件语句一起使用。 |

4.3 数组缩减

数组缩减方法是把一个数组缩减成一个值,这个值的类型与数组元素的类型相同,或者与with表达式值的类型相同。

| 方法 | 数组 |

|---|---|

| sum() | 返回所有数组元素的和,如果指定with表达式,则返回所有数组元素with表达式计算值的和 |

| product()积 | 返回所有数组元素的积,如果指定with表达式,则返回所有数组元素with表达式计算值的积 |

| and() | 返回所有数组元素的与,如果指定with表达式,则返回所有数组元素with表达式计算值的与 |

| or() | 返回所有数组元素的或,如果指定with表达式,则返回所有数组元素with表达式计算值的或 |

| xor() | 返回所有数组元素的或非,如果指定with表达式,则返回所有数组元素with表达式计算值的或非 |

byte f[] = {

1, 2, 3, 4 };

int tq;

tq = f.sum ; // y becomes 10 => 1 + 2 + 3 + 4

tq = f.product ; // y becomes 24 => 1 * 2 * 3 * 4

tq = f.xor with ( item + 4 ); // y becomes 12 => 5 ^ 6 ^ 7 ^ 8

5.队列

队列和链表相似,可以在一个队列中任何地方增加或删除元素,在性能上要优于动态数组

- 队列的声明是使用带有美元符号的下标 [$]

- $ 放在左边代表最小值 [$:2] = [0:2]

- $ 放在右边代表最大值 [1:$] = [1:2]

q2[$] = {

3,4};

q[$] = {

0,2,5};

方法:

| 方法 | 含义 |

|---|---|

| insert(i,j) | 在i位置插入元素j |

| delete(i) | 删除在i位置的元素 |

| push_front(i) | 在队列前面插入元素 |

| push_back(i) | 在队列末尾插入元素 |

| pop_front | 输出队列最前元素 |

| pop_back | 输出队列最后元素 |

总结:

参考文献:SystemVreilog验证测试平台编写指南 - [美]克里斯.斯皮尔

参考:https://blog.csdn.net/qq_33332955/article/details/107641152